lvds多通道驱动器

技术领域

1.本技术属于信号传输技术领域,尤其涉及一种lvds多通道驱动器。

背景技术:

2.随着信息化技术的迅猛发展,cpu(central processing unit,中央处理器)的时钟频率越来越高,处理速度越来越快,在各个设备之间会传输海量的数据。但是在信号传输时,cpu芯片内部高速信号的驱动能力弱,易受干扰。通常采用高速驱动器增加信号的驱动能力,并将信号发送至信号接收器,使得设备接收到cpu发送的数据。但现有高速驱动器只能实现单通道传输,无法实现多通道传输。

技术实现要素:

3.本技术实施例提供了一种lvds(low-voltage differential signaling低压差分信号)多通道驱动器,可以解决现有高速驱动器无法实现多通道传输的问题。

4.第一方面,本技术实施例提供了一种lvds多通道驱动器,包括缓冲电路和多通道驱动电路;

5.所述多通道驱动电路包括多个双环负反馈lvds驱动电路;

6.所述缓冲电路分别与每个所述双环负反馈lvds驱动电路电连接;

7.所述缓冲电路用于接收目标信号,增强所述目标信号的电压,并将增强后的目标信号分别传输至每个所述双环负反馈lvds驱动电路;

8.每个所述双环负反馈lvds驱动电路用于提高所述增强后的目标信号的工作频率,并根据所述增强后的目标信号输出高速差分lvds信号。

9.在第一方面的一种可能的实现方式中,所述缓冲电路包括第一缓冲支路、第二缓冲支路和相位调节电路;

10.所述第一缓冲支路,分别与每个所述双环负反馈lvds驱动电路电连接,用于接收所述目标信号中的第一信号,增强所述第一信号的电压,并将增强后的第一信号分别传输至每个所述双环负反馈lvds驱动电路;

11.所述第二缓冲支路,分别与每个所述双环负反馈lvds驱动电路电连接,用于接收所述目标信号中的第二信号,增强所述第二信号的电压,并将增强后的第二信号分别传输至每个所述双环负反馈lvds驱动电路;

12.所述第一信号和所述第二信号为全摆幅、相位相反的时钟信号或数据信号;

13.所述相位调节电路,分别与所述第一缓冲支路和所述第二缓冲支路电连接,用于调节所述第一信号和所述第二信号的相位关系。

14.在第一方面的一种可能的实现方式中,所述第一缓冲支路包括第一反相器、第三反相器和第七反相器;

15.所述第一反相器的输入端用于接收所述第一信号,所述第一反相器的输出端与所述第三反相器的输入端电连接,所述第三反相器的输出端与所述第七反相器的输入端电连

接,所述第七反相器的输出端分别与每个所述双环负反馈lvds驱动电路电连接。

16.在第一方面的一种可能的实现方式中,所述第二缓冲支路包括第二反相器、第四反相器和第八反相器;

17.所述第二反相器的输入端用于接收所述第二信号,所述第二反相器的输出端与所述第四反相器的输入端电连接,所述第四反相器的输出端与所述第八反相器的输入端电连接,所述第八反相器的输出端分别与每个所述双环负反馈lvds驱动电路电连接。

18.在第一方面的一种可能的实现方式中,所述相位调节电路包括第五反相器和第六反相器;

19.所述第五反相器的输入端与所述第三反相器的输出端电连接,所述第五反相器的输出端与所述第四反相器的输出端电连接,所述第六反相器的输入端与所述第四反相器的输出端电连接,所述第六反相器的输出端与所述第三反相器的输出端电连接。

20.在第一方面的一种可能的实现方式中,每个所述双环负反馈lvds驱动电路均包括第一负反馈电路、第二负反馈电路和驱动输出电路;

21.所述第一负反馈电路和所述第二负反馈电路均与所述驱动输出电路电连接,第一负反馈电路与所述第二负反馈电路电连接,所述第七反相器的输出端和所述第八反相器的输出端均与所述驱动输出电路电连接;

22.所述第一负反馈电路用于接收第一偏置电压,根据所述第一偏置电压输出第一电压至所述驱动输出电路,所述第一电压等于所述第一偏置电压;

23.所述第二负反馈电路用于接收第二偏置电压,根据所述第二偏置电压输出第二电压至所述驱动输出电路,所述第二电压等于所述第二偏置电压;

24.所述驱动输出电路用于接收所述增强后的第一信号和所述增强后的第二信号,所述增强后的第一信号和所述增强后的第二信号触发所述驱动输出电路工作,当所述驱动输出电路工作时,所述驱动输出电路用于根据所述第一电压和所述第二电压输出高速差分lvds信号。

25.在第一方面的一种可能的实现方式中,所述第一负反馈电路包括第一运算放大器、第一尾电流源、第七场效应管、第三电容、第九场效应管和第一电容;所述第一尾电流源为第五场效应管;

26.所述第一运算放大器的反相输入端用于接收所述第一偏置电压,所述第一运算放大器的同相输入端分别与所述第五场效应管的漏极、所述第一电容的第一端、所述第九场效应管的栅极和所述驱动输出电路电连接,所述第一运算放大器的输出端分别与所述第七场效应管的栅极、所述第五场效应管的栅极和第三电容的第一端电连接;所述第三电容的第二端与所述第九场效应管的源极电连接;所述第七场效应管的源极、所述第五场效应管的源极、所述第九场效应管的漏极和所述第一电容的第二端均用于与第一电源电连接;所述第七场效应管的漏极和所述第九场效应管的源极均与所述第二负反馈电路电连接;

27.所述第五场效应管的漏极用于输出所述第一电压;

28.所述第一运算放大器用于调节所述第五场效应管的栅极电压,控制所述第五场效应管输出的漏极电流,使所述第一电压等于所述第一偏置电压;

29.所述第一电容用于稳定所述第一电压;

30.所述第七场效应管、所述第九场效应管和所述第三电容用于调节所述第一负反馈

电路的工作频率,避免所述第一负反馈电路振荡。

31.在第一方面的一种可能的实现方式中,所述第二负反馈电路包括第二运算放大器、第二尾电流源、第八场效应管、第十场效应管、第二电容和第四电容;所述第二尾电流源为第六场效应管;

32.所述第二运算放大器的反向输入端用于接收所述第二偏置电压,所述第二运算放大器的同相输入端分别与所述第六场效应管的漏极、所述第二电容的第一端、所述第八场效应管的栅极和所述驱动输出电路电连接,所述第二运算放大器的输出端分别与所述第十场效应管的栅极、所述第六场效应管的栅极和所述第四电容的第一端电连接;所述第四电容的第二端与所述第八场效应管的源极电连接;所述第十场效应管的源极、所述第六场效应管的源极、所述第八场效应管的漏极和所述第二电容的第二端均接地;所述第八场效应管的源极与所述第七场效应管的漏极电连接,所述第十场效应管的漏极与所述第九场效应管的源极电连接;

33.所述第六场效应管的漏极用于输出所述第二电压;

34.所述第二运算放大器用于调节所述第六场效应管的栅极电压,控制所述第六场效应管输出的漏极电流,使所述第二电压等于所述第二偏置电压;

35.所述第二电容用于稳定所述第二电压;

36.所述第八场效应管、所述第十场效应管和所述第四电容用于调节所述第二负反馈电路的工作频率,避免所述第二负反馈电路振荡。

37.在第一方面的一种可能的实现方式中,所述驱动输出电路包括第一场效应管、第二场效应管、第三场效应管、第四场效应管、第一缓冲器和第二缓冲器;

38.所述第三场效应管的栅极与所述第四场效应管的栅极电连接,作为第一信号输入端;所述第一场效应管的栅极与所述第二场效应管的栅极电连接,作为第二信号输入端;所述第七反相器的输出端与所述第二缓冲器的输入端电连接,所述第二缓冲器的输出端与所述第一信号输入端电连接;所述第八反相器的输出端与所述第一缓冲器的输入端电连接,所述第一缓冲器的输出端与所述第二信号输入端电连接;所述第一场效应管的源极分别与所述第三场效应管的源极和所述第五场效应管的漏极电连接;所述第二场效应管的源极分别与所述第四场效应管的源极和所述第六场效应管的漏极电连接;所述第三场效应管的漏极和所述第四场效应管的漏极电连接,作为第一输出端;所述第一场效应管的漏极与所述第二场效应管的漏极电连接,作为第二输出端;所述第一输出端用于与终端电阻的第一端电连接,所述第二输出端用于与所述终端电阻的第二端电连接,所述终端电阻的两端输出高速差分lvds信号。

39.在第一方面的一种可能的实现方式中,所述第一场效应管和所述第三场效应管为p沟道场效应管,所述第二场效应管和所述第四场效应管为n沟道场效应管。

40.本技术实施例与现有技术相比存在的有益效果是:

41.本技术实施例提供了一种lvds多通道驱动器,包括缓冲电路和多通道驱动电路。多通道驱动电路由多个双环负反馈lvds驱动电路组成,其通道数量可根据实际需求进行设置。缓冲电路分别与每个双环负反馈lvds驱动电路电连接。当cup向目标设备传输数据时,首先通过缓冲电路增强目标信号的电压,提高目标信号的驱动能力,使目标信号不易受到干扰,并将增强后的目标信号分别传输至每个双环负反馈lvds驱动电路。双环负反馈lvds

驱动电路可以提高增强后的目标信号的工作频率,并根据增强后的目标信号输出高速差分lvds信号。多个双环负反馈lvds驱动电路分别根据增强后的目标信号输出多个高速差分lvds信号,并将多个高速差分lvds信号稳定、可靠的传输至多个目标设备,使多个目标设备同时接收到cpu发送的数据。

附图说明

42.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

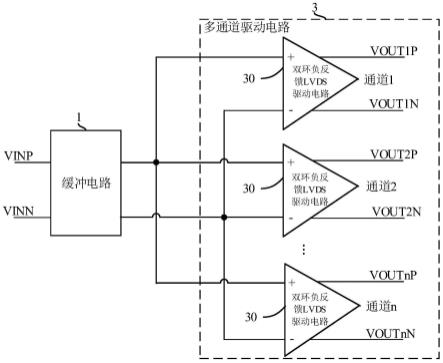

43.图1是本技术一实施例提供的lvds多通道驱动器的结构示意图;

44.图2是本技术另一实施例提供的lvds多通道驱动器的结构示意图;

45.图3是本技术另一实施例提供的lvds多通道驱动器的结构示意图;

46.图4是本技术另一实施例提供的缓冲电路与一个双环负反馈lvds驱动电路的连接示意图;

47.图5是本技术另一实施例提供的缓冲电路与一个双环负反馈lvds驱动电路的连接示意图。

具体实施方式

48.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本技术实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本技术。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本技术的描述。

49.应当理解,当在本技术说明书和所附权利要求书中使用时,术语“包括”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

50.还应当理解,在本技术说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

51.如在本技术说明书和所附权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当

…

时”或“一旦”或“响应于确定”或“响应于检测到”。类似地,短语“如果确定”或“如果检测到[所描述条件或事件]”可以依据上下文被解释为意指“一旦确定”或“响应于确定”或“一旦检测到[所描述条件或事件]”或“响应于检测到[所描述条件或事件]”。

[0052]

另外,在本技术说明书和所附权利要求书的描述中,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0053]

在本技术说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本技术的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变

形都意味着“包括但不限于”,除非是以其他方式另外特别强调。

[0054]

如图1所示,本技术实施例提供了一种lvds多通道驱动器,包括缓冲电路1和多通道驱动电路3。多通道驱动电路3包括多个双环负反馈lvds驱动电路30,缓冲电路1分别与每个双环负反馈lvds驱动电路30电连接。

[0055]

其中,多个双环负反馈lvds驱动电路30分别对应通道1、通道2、

……

、通道n,n为大于1的整数,通道的数量可根据实际需求进行设置。

[0056]

具体的,当cup向目标设备传输数据时,缓冲电路1接收目标信号vinp/vinn,并增强目标信号vinp/vinn的电压,提高目标信号vinp/vinn的驱动能力,使目标信号vinp/vinn不易受到干扰。然后将增强后的目标信号vinp/vinn分别传输至每个双环负反馈lvds驱动电路30。

[0057]

双环负反馈lvds驱动电路30可以提高增强后的目标信号vinp/vinn的工作频率,并根据增强后的目标信号vinp/vinn输出与通道相对应的高速差分lvds信号voutnp/voutnn。

[0058]

多个双环负反馈lvds驱动电路30分别根据增强后的目标信号输出多个将高速差分lvds信号,并将多个将高速差分lvds信号同时传输至多个目标设备,使多个目标设备同时接收到cpu发送的数据。其中多个高速差分lvds信号分别为高速差分lvds信号vout1p/vout1n、高速差分lvds信号vout2p/vout2n、

……

、高速差分lvds信号voutnp/voutnn。

[0059]

如图2所示,缓冲电路1包括第一缓冲支路10、第二缓冲支路11和相位调节电路12。第一缓冲支路10分别与每个双环负反馈lvds驱动电路30电连接。第二缓冲支路12分别与每个双环负反馈lvds驱动电路30电连接。相位调节电路11分别与第一缓冲支路10和第二缓冲支路12电连接。

[0060]

具体的,第一缓冲支路10接收目标信号vinp/vinn中的第一信号vinp,并增强第一信号vinp的电压,提高第一信号vinp的驱动能力,使第一信号vinp不易受到干扰。然后将增强后的第一信号vinp分别传输至每个双环负反馈lvds驱动电路30。

[0061]

第二缓冲支路12接收目标信号vinp/vinn中的第二信号vinn,并增强第二信号vinn的电压,提高第二信号vinn的驱动能力,使第二信号vinn不易受到干扰。然后将增强后的第二信号vinn分别传输至每个双环负反馈lvds驱动电路30。

[0062]

相位调节电路11调节第一信号vinp和第二信号vinn的相位关系,使第一信号vinp和第二信号vinn具有更好的差分关系。其中第一信号vinp和第二信号vinn为全摆幅、相位相反的时钟信号或数据信号。

[0063]

如图3所示,第一缓冲支路10包括第一反相器101、第三反相器103和第七反相器107。第一反相器101的输入端接收第一信号vinp,第一反相器101的输出端与第三反相器103的输入端电连接,第三反相器103的输出端与第七反相器107的输入端电连接,第七反相器107的输出端分别与每个双环负反馈lvds驱动电路30电连接。

[0064]

具体的,第一反相器101的输入端接收第一信号vinp,第一反相器101、第三反相器103和第七反相器107增强第一信号vinp的电压,提高第一信号vinp的驱动能力,使第一信号vinp不易受到干扰。第七反相器107的输出端将增强后的第一信号vinp的电压分别传输至每个双环负反馈lvds驱动电路30。

[0065]

如图3所示,第二缓冲支路12包括第二反相器122、第四反相器124和第八反相器

128。第二反相器122的输入端接收第二信号vinn,第二反相器122的输出端与第四反相器124的输入端电连接,第四反相器124的输出端与第八反相器128的输入端电连接,第八反相器128的输出端分别与每个双环负反馈lvds驱动电路30电连接。

[0066]

具体的,第二反相器122的输入端接收第二信号vinn,第二反相器122、第四反相器124和第八反相器128增强第二信号vinn的电压,提高第二信号vinn的驱动能力,使第二信号vinn不易受到干扰。第八反相器128的输出端将增强后的第二信号vinn分别传输至每个双环负反馈lvds驱动电路30。

[0067]

如图3所示,相位调节电路11包括第五反相器115和第六反相器116。第五反相器115的输入端与第三反相器103的输出端电连接,第五反相器115的输出端与第四反相器124的输出端电连接,第六反相器116的输入端与第四反相器124的输出端电连接,第六反相器116的输出端与第三反相器103的输出端电连接。

[0068]

具体的,第五反相器115和第六反相器116用于调节第一信号vinp和第二信号vinn的相位关系,使第一信号vinp和第二信号vinn具有更好的差分关系,同时保证没有目标信号输入时,输出固定的逻辑信号。

[0069]

如图4所示,每个双环负反馈lvds驱动电路30均包括第一负反馈电路301、第二负反馈电路303和驱动输出电路302。第一负反馈电路301和第二负反馈电路303均与驱动输出电路302电连接,第一负反馈电路301与第二负反馈电路303电连接。第七反相器107的输出端和第八反相器128的输出端均与驱动输出电路302电连接。

[0070]

具体的,第一负反馈电路301接收第一偏置电压vref_h,根据第一偏置电压vref_h输出第一电压至驱动输出电路302,第一电压等于第一偏置电压vref_h。

[0071]

第二负反馈电路接收第二偏置电压vref_l,根据第二偏置电压vref_l输出第二电压至驱动输出电路302,第二电压等于第二偏置电压vref_l。

[0072]

驱动输出电路302接收增强后的第一信号vinp和增强后的第二信号vinn,增强后的第一信号vinp和增强后的第二信号vinn触发驱动输出电路302工作。当驱动输出电路302工作时,驱动输出电路302根据第一电压和第二电压输出高速差分lvds信号voutnp/voutnn。

[0073]

示例性的,第一偏置电压vref_h和第二偏置电压vref_l均由偏置电路产生,偏置电路的实现方式可以用电阻对电源电压进行分压。

[0074]

如图5所示,第一负反馈电路301包括第一运算放大器3011、第一尾电流源、第七场效应管m7、第三电容c3、第九场效应管m9和第一电容c1。第一尾电流源为第五场效应管m5。第一运算放大器3011的反相输入端用于接收第一偏置电压vref_h,第一运算放大器3011的同相输入端分别与第五场效应管m5的漏极、第一电容c1的第一端、第九场效应管m9的栅极和驱动输出电路302电连接,第一运算放大器3011的输出端分别与第七场效应管m7的栅极、第五场效应管m5的栅极和第三电容c3的第一端电连接。第三电容c3的第二端与第九场效应管m9的源极电连接。第七场效应管m7的源极、第五场效应管m5的源极、第九场效应管m9的漏极和第一电容c1的第二端均用于与第一电源vdd电连接,第七场效应管m7的漏极和第九场效应管m9的源极均与第二负反馈电路303电连接。

[0075]

具体的,第一运算放大器3011和第五场效应管m5构成负反馈环路。通过第一运算放大器3011调节第五场效应管m5的栅极电压,从而控制第五场效应管m5输出的漏极电流,

最终使第一电压等于第一偏置电压vref_h,第一电压为节点net1的电压。第一电容c1用于稳定第一电压。第七场效应管m7、第九场效应管m9和第三电容c3用于调节第一负反馈电路301的工作频率,避免第一负反馈电路301振荡。

[0076]

如图5所示,第二负反馈电路303包括第二运算放大器3032、第二尾电流源、第八场效应管m8、第十场效应管m10、第二电容c2和第四电容c4。第二尾电流源为第六场效应管m6。第二运算放大器3032的反向输入端用于接收第二偏置电压vref_l,第二运算放大器3032的同相输入端分别与第六场效应管m6的漏极、第二电容c2的第一端、第八场效应管m8的栅极和驱动输出电路302电连接,第二运算放大器3032的输出端分别与第十场效应管m10的栅极、第六场效应管m6的栅极和第四电容c4的第一端电连接。第四电容c4的第二端与第八场效应管m8的源极电连接。第十场效应管m10的源极、第六场效应管m6的源极、第八场效应管m8的漏极和第二电容c2的第二端均接地。第八场效应管m8的源极与第七场效应管m7的漏极电连接,第十场效应管m10的漏极与第九场效应管m9的源极电连接。

[0077]

具体的,第二运算放大器3032和第六场效应管m6构成负反馈环路。通过第二运算放大器3032调节第六场效应管m6的栅极电压,从而控制第六场效应管m6输出的漏极电流,最终使第二电压等于第二偏置电压vref_l,第二电压为节点net2的电压。第二电容c2用于稳定第二电压。第八场效应管m8、第十场效应管m10和第四电容c4用于调节第二负反馈电路303的工作频率,避免第二负反馈电路303振荡。

[0078]

如图5所示,驱动输出电路302包括第一场效应管m1、第二场效应管m2、第三场效应管m3、第四场效应管m4、第一缓冲器3021和第二缓冲器3022。第三场效应管m3的栅极与第四场效应管m4的栅极电连接,作为第一信号输入端。第一场效应管m1的栅极与第二场效应管m2的栅极电连接,作为第二信号输入端。第七反相器107的输出端与第二缓冲器3022的输入端电连接,第二缓冲器3022的输出端与第一信号输入端电连接。第八反相器128的输出端与第一缓冲器3021的输入端电连接,第一缓冲器3021的输出端与第二信号输入端电连接。第一场效应管m1的源极分别与第三场效应管m3的源极和第五场效应管m5的漏极电连接。第二场效应管m2的源极分别与第四场效应管m4的源极和第六场效应管m6的漏极电连接。第三场效应管m3的漏极和第四场效应管m4的漏极电连接,作为第一输出端。第一场效应管m1的漏极与第二场效应管m2的漏极电连接,作为第二输出端。第一输出端用于与终端电阻rt的第一端电连接,第二输出端用于与终端电阻rt的第二端电连接,终端电阻rt的两端输出高速差分lvds信号voutnp/voutnn。

[0079]

具体的,第一缓冲器3021用于进一步提高增强后的第二信号vinn的驱动能力。第二缓冲器3022用于进一步提高增强后的第一信号vinp的驱动能力。增强后的第二信号vinn施加在第一场效应管m1和第二场效应管m2的栅极上,用于控制第一场效应管m1导通和关断,控制第二场效应管m2的关断和导通。当第一场效应管m1导通,第二场效应管m2关断时,第一电压减去第一场效应管m1的源漏电压,得到高速差分lvds信号voutnn的高电平值。当第一场效应管m1关断,第二场效应管m2导通时,第二电压加上第二场效应管m2的源漏电压,得到高速差分lvds信号voutnn的低电平值。增强后的第一信号vinp施加在第三场效应管m3和第四场效应管m4的栅极上,用于控制第三场效应管m3的导通和关断,控制第四场效应管m4的关断和导通。当第三场效应管m3导通,第四场效应管m4关断时,第一电压减去第三场效应管m3的源漏电压,得到高速差分lvds信号voutnp的高电平值。当第三场效应管m4导通,第

三场效应管m3关断时,第二电压加上第四场效应管m4的源漏电压,得到高速差分lvds信号voutnp的低电平值。最终在终端电阻rt的两端输出高速差分lvds信号voutnp/voutnn。

[0080]

示例性的,第一场效应管m1和第三场效应管m3为p沟道场效应管。第二场效应管m2和第四场效应管m4为n沟道场效应管。

[0081]

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述或记载的部分,可以参见其它实施例的相关描述。

[0082]

以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。