1.本公开涉及知识产权安全锁定装置和方法。

背景技术:

2.诸如处理器之类的知识产权(intellectual property,ip)块可能会在不受信任的代工厂中被过度生产。未经授权生产的ip块可在黑市中被销售。另外,ip块的未经授权的销售可导致收入损失和不法行为。

技术实现要素:

3.根据本公开的实施例,提供了一种用于一个或多个电路块的安全的装置,该装置包括:伪随机生成器,用于生成跳频时间序列;与所述伪随机生成器相耦合的频率合成器,该频率合成器用于接收输入时钟并且生成输出时钟;以及调制器,用于经由所述跳频时间序列将指示一个或多个密钥的代码调制到所述输入时钟上。

4.根据本公开的实施例,提供了一种用于一个或多个电路块的安全的装置,该装置包括:第一通道,用于接收由用于生成跳频时间序列的伪随机生成器生成的跳频时间序列;以及第二通道,用于接收来自频率合成器的输出,其中所述频率合成器的输入时钟被经由所述跳频时间序列用代码来调制,其中所述代码指示一个或多个密钥。

5.根据本公开的实施例,提供了一种包括对一个或多个电路块的保护的封装,该封装包括:衬底;所述衬底上的处理器;以及所述衬底上的集成电路,该集成电路包括信任根,该信任根包括:伪随机生成器,用于生成跳频时间序列;与所述伪随机生成器相耦合的频率合成器,该频率合成器用于接收输入时钟并且生成输出时钟;以及调制器,用于经由所述跳频时间序列将指示一个或多个密钥的代码调制到所述输入时钟上,其中所述跳频时间序列和所述输出时钟被发送到所述处理器。

附图说明

6.通过以下给出的详细描述并且通过本公开的各种实施例的附图将更充分地理解本公开的实施例,然而详细描述和附图不应当被理解为将本公开限制到特定实施例,而只是仅用于说明和理解。

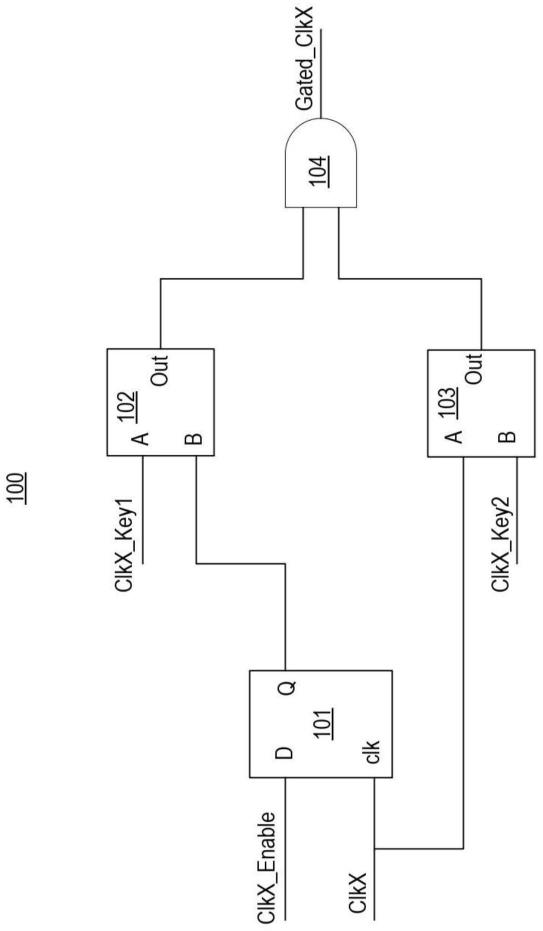

7.图1根据一些实施例图示了一种时钟门控装置,其具有逻辑来根据安全密钥对时钟进行门控或解除门控。

8.图2根据一些实施例图示了知识产权(ip)块中的时钟门控逻辑的层次体系,其中时钟门控逻辑包括逻辑来根据安全密钥对时钟进行门控或解除门控。

9.图3根据一些实施例图示了用于扫描链的时钟门控逻辑,其中该时钟门控逻辑包括逻辑来根据安全密钥对时钟进行门控或解除门控。

10.图4根据一些实施例图示了一种生成加密安全密钥的装置,其中加密安全密钥被解码来随后对时钟缓冲器进行门控或解除门控。

11.图5根据一些实施例图示了一种对存储在熔丝中的加密安全密钥进行解码的装置。

12.图6根据一些实施例图示了具有向处理器或片上系统提供加密安全密钥的信任根(rot)ip块的封装。

13.图7根据一些实施例图示了生成加密安全密钥的方法的流程图,这些加密安全密钥随后被解码来对时钟进行门控或解除门控。

14.图8根据一些实施例图示了具有时钟门控装置的智能设备或者计算机系统或者soc(片上系统),该时钟门控装置具有逻辑来根据安全密钥对时钟进行门控或解除门控。

具体实施方式

15.一些实施例描述了一种用于知识产权(ip)块的安全机制,其中时钟门控逻辑被用加密密钥来增强,这些加密密钥即使在时钟被ip块使能的情况下也被用来对时钟进行门控或解除门控。加密密钥被输入到一个或多个逻辑中,如果密钥得到验证,则该逻辑允许时钟传播,而如果密钥未得到验证,则该逻辑对时钟在ip块中的传播进行门控。在一些实施例中,通过随机改变载波的频率并且在由载波携带的脉冲宽度调制(或占空比调制)信号中编码数字代码来生成加密密钥。随机变化的频率导致载波中的扩频。在扩频中,成为载波的信号(例如,电、电磁或声信号)被以特定的带宽生成,并且在频域中随机扩散,从而产生具有更宽带宽的信号。这种技术允许了在加密密钥生成器和使用加密密钥的时钟门控逻辑之间建立安全通信。各种实施例的技术针对在加密密钥生成器和使用加密密钥(而不是安全通信)的任何硬件逻辑之间分发的密钥允许边通道抵抗。

16.虽然是参考使用加密密钥的时钟门控来说明各种实施例的,但实施例可被扩展到任何逻辑。例如,加密密钥可被用于电力门控逻辑域、禁止访问缓存、禁止访问熔丝、控制多路复用器、控制状态机、禁用本地电力供应调节器,等等。各种实施例的技术还增大了对自然干扰、噪声和人为干扰的抵抗力,以防止检测并且限制功率通量密度。

17.在一些实施例中,脉冲宽度调制(pulse width modulated,pwm)信号与跳频时间序列一起被发送到ip块,供解码器进行解码。跳频时间序列决定了扩频的随机性。例如,知道跳频时间序列后,解码器可以确立载波被调制的频率和时间戳。在各种实施例中,跳频时间序列是低频序列。这里,低频指的是小于500khz的频率。例如,跳频时间序列具有23khz的频率。

18.在一些实施例中,密钥由加密引擎生成,并且这些密钥经由经历扩频的时钟被运载。在一些实施例中,通过在与逻辑零和逻辑一相对应的两个级别上调制时钟占空比,在时钟内编码了密钥。对于这种占空比调制技术,两个时钟线(例如,时钟线1和时钟线2)可被用来提供一种差分编码,以通过确保占空比时钟发射仍然是均匀的,来防止边通道攻击。例如,编码使用例如,时钟线1:1

→

75%0

→

25%,以及时钟线2:0

→

75%,1

→

25%,被解码为值1,以及时钟线1:0

→

75%,1

→

25%,并且时钟线2:1

→

25%,0

→

75%将被解码为值0。在这个示例中,25%和75%表示时钟的占空比,而“1”和“0”表示占空比所表示的逻辑值。

19.伪随机跳频时间序列被用于随机化扩频,而不是使用低频三角波或锯齿波来调制频率合成器的参考时钟(和/或输出时钟)。这种伪随机跳频时间序列是解锁加密密钥的关键。在一些实施例中,pwm加密密钥是由应用于时钟的低频伪随机跳频时间序列所携带的。

为了解码pwm调制的加密密钥,伪随机跳频时间序列被使用。

20.跳频时间序列和具有带跳频时间序列的扩频的调制码的时钟被发送到解码器。在一些实施例中,加密密钥的每个比特都以跳频时间序列中定义的特定频率被传输。

21.在一些实施例中,解码器是ip块的一部分。在一些实施例中,解码器是额外的ip,它被提供给ip块(或处理器)的经验证的购买者或所有者,以便经验证的购买者或所有者可获取加密密钥,以使能ip块的适当或正常功能。在一些实施例中,加密密钥被存储在ip块的熔丝中,供ip块的经验证的购买者或所有者使用。在一些实施例中,ip块中的时钟门控逻辑(或驱动器)使用非标准的时钟生成设备。在一些实施例中,相同的时钟门控逻辑被加密引擎用于生成加密密钥。例如,不同的时钟门控逻辑具有不同的加密密钥。对ip块接收的时钟进行解调、针对不同时钟门控逻辑对密钥进行解码、以及确定随机跳频时间序列,为保护ip块中的时钟的使用提供了一种多级别的方法。

22.在一些实施例中,提供了一种加密引擎,它包括伪随机生成器、频率合成器、以及调制器。伪随机生成器生成跳频时间序列。频率合成器与伪随机生成器耦合。频率合成器接收输入时钟(例如,参考时钟)并且生成输出时钟。在一些实施例中,调制器经由时钟跳频时间序列处的时钟占空比的脉冲宽度调制,将指示一个或多个密钥的代码调制到输入时钟上。该一个或多个密钥被用于对电路进行门控或解除门控。在一些实施例中,该电路包括时钟门控逻辑。在一些实施例中,一个或多个密钥包括第一密钥和第二密钥,其中时钟门控逻辑包括时序单元、第一异或(xor)或者异或非(xnor)门、第二异或或者异或非门、以及与(and)门或者与非(nand)门。时序单元接收本地时钟和使能信号(enable)。第一异或或者异或非门接收时序单元的输出和第一密钥。第二异或或者异或非门接收本地时钟和第二密钥。与门或者与非门与第一异或或者异或非门的输出和第二异或或者异或非门的输出相耦合。

23.在一些实施例中,加密引擎包括:第一通道,用于将跳频时间序列传输到知识产权(ip)块;以及第二通道,用于将输出时钟传输到ip块。在一些实施例中,ip块包括解码器,用于从输出时钟中提取一个或多个密钥。在一些实施例中,ip块包括熔丝,用于存储一个或多个密钥和/或跳频时间序列。在各种实施例中,输入时钟使用跳频时间序列来经历扩频。跳频时间序列是低频跳频时间序列。频率合成器包括锁相环或锁频环以及脉冲宽度调制器。

24.各种实施例有许多技术效果。例如,对于携带编码的密钥的载波带有随机扩频的多级安全机制可以消除(或大大减少)使用在不信任的代工厂中过度生产的ip块或处理器的机会。该安全机制将阻止未经授权生产的ip块在黑市上销售。与未经授权的ip块销售相关联的收入损失也被消除或大大减少。其他技术效果将从各种实施例和附图中清楚显现。

25.在接下来的描述中,论述了许多细节以提供对本公开的实施例的更透彻说明。然而,本领域技术人员将会清楚,没有这些具体细节也可实现本公开的实施例。在其他情况下,以框图形式而不是详细示出公知的结构和设备,以避免模糊本公开的实施例。

26.注意,在实施例的相应附图中,以线条来表示信号。一些线条可能更粗,以指示更多的构成信号路径,和/或在一端或多端具有箭头,以指示主信息流方向。这种指示并不打算是限制性的。更确切地说,这些线条与一个或多个示范性实施例被联合使用来帮助更容易理解电路或逻辑单元。由设计需要或偏好决定的任何所表示的信号可实际上包括可在任一方向上行进并且可利用任何适当类型的信号方案来实现的一个或多个信号。

27.图1根据一些实施例图示了一种时钟门控装置100,其具有逻辑来根据安全密钥对时钟进行门控或解除门控。装置100包括时序逻辑101、第一逻辑102、第二逻辑103、以及与门104。时序逻辑101的数据输入连接到clkx_enable信号,而时钟输入(clk)接收时钟clkx。时序逻辑101的输出“q”被输入到第一逻辑102。第一逻辑102的第二输入端接收第一加密密钥(clkx_key1)。第二逻辑103的第一输入接收clkx,并且第二逻辑103的第二输入接收第二加密密钥(clkx_key2)。在一些实施例中,第一逻辑102和第二逻辑103包括异或门。在其他实施例中,第一逻辑102和第二逻辑103可以是异或非门、异或门、多路复用器、状态机,等等。时序逻辑101可以是触发器或者锁存器。第一逻辑102和第二逻辑103的输出被输入到与门104,与门104输出门控时钟(gated_clkx)。

28.可按许多方式来修改时钟门控装置100,只要其保留由加密密钥clkx_key1和clky_key2对clkx的传播进行门控的功能。例如,可以用与非门来代替与门104,而可以用扫描小工具来代替时序101。当clkx_enable为高时,时序逻辑101的输出q随着翻转时钟clkx而翻转。然而,该翻转输出q和时钟clkx分别被第一和第二逻辑门102和103进行门控。一旦clkx_key1和clkx_key2被使能,输出与门104就对时钟解除门控,并且允许gated_clkx翻转(例如,clkx被传递到gated_clkx节点)。这里,节点名称和信号名称是可互换使用的。例如,取决于句子的上下文,gated_clkx可以指门控的时钟信号或者节点。

29.在各种实施例中,clkx到gated_clkx的传播取决于对加密密钥clkx_key1和clkx_key2的解码和验证。多个机制可被用于生成和传输安全密钥clkx_key1和clkx_key2。在一些实施例中,clkx_key1和clkx_key2是由同一个逻辑或者该逻辑的实例来生成、传输和解码的。例如,用于生成密钥的代码、用代码调制时钟占空比以使得时钟充当可能有扩频的代码信息的载波的方案,以及对接收到的数据进行解码以提取clkx_key1的逻辑,与用于提取clkx_key2的逻辑是相同的(或者是同一逻辑的不同实例)。在一些实施例中,clkx_key1和clkx_key2是由不同的逻辑来生成、传输和/或解码的。例如,与用于提取clkx_key2的方案相比,用于生成密钥的代码、将代码调制到可能有扩频的载波上的方案以及对接收到的数据进行解码以提取clkx_key1的逻辑是不同的(例如,不同的机制)。因此,为每个密钥建立了额外的安全性。

30.虽然是参考使用加密密钥的时钟门控来说明各种实施例的,但实施例可被扩展到任何逻辑。例如,加密密钥可被用于电力门控逻辑域、禁止访问缓存、禁止访问熔丝、控制多路复用器、控制状态机、禁用本地电力供应调节器,等等。

31.图2根据一些实施例图示了知识产权(ip)块中的时钟门控逻辑的层次体系200,其中时钟门控逻辑包括逻辑来根据安全密钥对时钟进行门控或解除门控。在一些实施例中,时钟门控发生在ip块(例如,处理器)中的层次体系的不同级别。clk1由时钟源(例如,锁相环或锁频环)生成。clk1随后被向下分发到不同的逻辑(例如,模块1,模块2,

……

,模块n)。在一些实施例中,随着clk1向下传播时,它被能够对clk1的传播进行门控的驱动器或缓冲器所驱动。这些驱动器或缓冲器被放置在时钟分发网络的不同级别。

32.例如,时钟门驱动器100-1被放置在时钟分发的顶部,并且生成时钟clk2。然后clk2被直接提供给一些时序逻辑(例如,时序逻辑201)和其他时钟门驱动器(例如,100-21至100-2n)。在这个示例中,时钟门驱动器100-21的输出时钟是clk2a,时钟门驱动器100-22的输出是时钟clk2b,时钟门驱动器100-23的输出是时钟clk2c,并且时钟门驱动器100-2n

的输出是clk2n。这些时钟中的每一个(例如,clk2a,clk2b,clk2c,到clk2n)被更多的时钟门驱动器向下驱动和/或被时序逻辑接收。在这个示例中,这些时钟被不同的模块接收。例如,clk2a被模块1并被时钟门驱动器100-31和100-32以及时序单元100-32和202a接收;clk2b被模块2并被时钟门驱动器100-41以及时序单元202b接收;clk2c被模块3并被时钟门驱动器100-51以及时序单元202c接收;并且clk2b被模块n并被时钟门驱动器100-n1以及时序单元202n接收。时钟门驱动器的输出被进一步向下分发。例如,clk3a被时序逻辑202aa接收,clk3b被时序单元202ab接收,clk4a被时序逻辑202ba接收,clk5a被时序逻辑单元202ca接收,并且clk3na被时序逻辑202na接收。

33.在一些实施例中,时钟门驱动器被不同的加密密钥所门控。这就允许了针对未经授权的用户的多级别的保护。如果黑客以某种方式弄清了用于对一类时钟门缓冲器应用扩频的跳频时间表,那么对于其他时钟门缓冲器来说,该黑客弄清跳频时间表和载波上的调制代码的可能性就变得很低,因为要解码的更多。

34.在这个示例中,时钟门缓冲器100-1是由clk1_key1和clk1_key2来门控的。注意,一些或所有的时钟门驱动器具有其正常的使能,以管理功率消耗。例如,当获得正确的密钥clk1_key1和clk1_key2时,来自时钟门驱动器100-1的clk2仍然可被clk1_enable门控。同样,来自时钟门驱动器100-21的clk2a仍然可被clk2_enable门控,来自时钟门驱动器100-22的clk2b仍然可被clk2_enable门控,来自时钟门驱动器100-23的clk2c仍然可被clk2_enable门控,并且来自时钟门驱动器100-2n的clk2n仍然可被clk2_enable门控。clk3_enable用于对时钟驱动器100-31、100-41、100-51和100-n1进行门控。

35.图3根据一些实施例图示了用于扫描链的时钟门控逻辑300,其中该时钟门控逻辑包括逻辑来根据安全密钥对时钟进行门控或解除门控。在这个示例中,clk1是由时钟驱动器100-1门控的。clk2被提供作为寄存器301-1,301-2,301-3,...301-n的链的采样时钟,它们一起形成扫描链。扫描链的输入是scan_in,其在scan_enable被断言时通过每个寄存器(或时序单元)传播。每个寄存器的输出(例如,s0,s1,..sn)被组合起来(例如,s[0:n]),以形成扫描输出scan_out。扫描链携带来自处理器的数据,并且如果此数据被盗用,就会泄露ip块的重要方面。加密密钥(例如,clk1_key1,和clk1_key2)可针对扫描链的未经授权的使用对clk2的传播进行门控(从而禁用扫描链)。类似的概念可被扩展到电力门控,以及任何其他逻辑的锁定或门控。

[0036]

图4根据一些实施例图示了一种生成加密安全密钥的装置400,其中加密安全密钥被解码来随后对时钟缓冲器进行门控或解除门控。装置400包括一个或多个加密逻辑401(例如,401-1、401-2)。为简单起见,加密逻辑是用其一般标签401而不是401-1和401-2来称呼的。在一些实施例中,加密逻辑401包括伪随机数生成器402、脉冲宽度调制器(pwm)403、频率合成器404、以及时钟门控结构405。伪随机数生成器402,也被称为确定性随机比特生成器,是一种用于生成如下数字序列的算法(硬件和/或软件),该数字序列的属性与随机数序列的属性接近。

[0037]

一些实施例使用参考时钟(或输出时钟)的扩频调制作为一种手段,来将射频发射扩散在时钟频率周围的更宽的频带上,并且符合美国联邦通信委员会(fcc)无线电缓解限制。实现扩频的一种方式是用非常低的频率(例如,23khz左右)以周期性方式(例如,三角波或锯齿波)调制时钟频率。这种周期性的跳频可能足以达到在宽频带上扩散rf发射的目的,

但可能会被攻击者跟踪到。例如,攻击者可监视参考时钟的rf发射概况,并且确定特定频率的三角波或锯齿波正被用于建立扩频。

[0038]

在一些实施例中,使用跳频时间序列来应用扩频,该序列是随机的。这个随机序列是由伪随机数生成器402生成的。根据各种实施例,这个随机序列对每一个新的密钥递送都会随机变化,并且也会在随机时间变化,以确保序列的短暂性使得攻击者难以使用边通道技术。任何适当的随机生成器都可被用于实现伪随机数生成器402。通过将随机跳频时间序列应用来建立扩频,任何攻击者都更难弄清扩频的底层方案。随着随机跳频时间序列被建立用于扩频,当时钟(例如,参考时钟)被编码有数据(例如,用于对特定时钟门控驱动器进行门控的密钥)时,编码的数据很难或几乎不可能被破译。在一些实施例中,为特定的时钟门控结构405生成加密密钥。如果ip块(例如,处理器)为其时钟门控驱动器使用不同类型的设计,则可为每个这样的时钟门控驱动器生成单独的加密密钥。

[0039]

在一些实施例中,pwm生成器403接收与时钟门控结构405相关联的代码,其中该代码表示要编码的密钥。然后,pwm生成器403对参考时钟(输入到频率合成器404)或正在由频率合成器404生成的时钟应用调制。这个输入参考时钟(输入到频率合成器404)可由振荡器(例如,晶体振荡器)或任何其他时钟源生成。pwm生成器403可使用任何适当的方案来编码用于时钟门控结构405的密钥的代码。

[0040]

在一个示例中,按75%调制参考时钟(到频率合成器404的参考时钟)表示对逻辑“1”值的编码,而按25%调制参考时钟(到频率合成器404的参考)表示对逻辑“0”的编码。这样,时钟信号(例如,频率合成器404的参考时钟),以及延伸到频率合成器404的输出,携带着嵌入在占空比中的加密密钥,其中每个比特的传输频率是根据跳频模式序列来定义的。根据一些实施例,每次密钥被生成并且传输到时钟门以解锁ip并且使能时钟时,这种跳频模式就会发生变化。攻击者如果不能够实时访问跳频模式以识别每个比特的频率并且从辐射的发射中提取占空比,就不太可能嗅探到加密密钥。

[0041]

频率合成器404的输出从而是pwm时钟(例如,来自加密逻辑401的pwm时钟1,和pwm时钟2)。调制是利用低频的跳频模式序列发生的。在一些实施例中,来自合成器404的输出时钟(pwm时钟)是ip块的参考时钟。例如,来自合成器404的输出时钟被用作ip块中的锁相环的参考时钟。在一些实施例中,来自合成器404的输出时钟(pwm时钟)是ip块中使用的采样时钟。

[0042]

一个或多个加密逻辑401的输出被解码器406(例如,406-1和406-2)接收,该解码器对接收的数据进行解码并且提取加密密钥clkx_key1、clkx_key2。在这个示例中,跳频时间序列(例如,跳频时间序列1和序列2)与参考时钟一起在单独通道(或互连)上被发送到ip块的解码器406。在各种实施例中,通过(在使用跳频时间序列去除扩频之后)提取原生时钟来对pwm时钟上编码的代码(即,密钥)进行解码。因此,密钥被提取出来。在一些实施例中,从解码器提取每个密钥。在一些实施例中,伪随机序列(即,跳频时间序列)被使用具有编码的加密密钥的并行通道(例如,与携带pwm时钟的通道并行)传输到ip块。在一些实施例中,pwm时钟或者到频率合成器404的参考时钟的时钟频率被以随机化模式(来自生成器403)改变,逻辑401可在每次需要使能时钟门但密钥尚未传输时改变该随机化模式。

[0043]

图5根据一些实施例图示了一种对存储在熔丝中的加密安全密钥进行解码的装置500。装置500包括处理器501(例如,图8的soc)和/或配设服务器502。在一些实施例中,配设

服务器502向处理器501提供加密密钥,这些加密密钥由安全逻辑503存储和/或管理。例如,安全逻辑503将加密密钥烧熔在熔丝中。

[0044]

在一些实施例中,安全逻辑503包括具有物理不可克隆功能(physically unclonable function,puf)的电路,该电路产生用作秘密密匙的随机值。puf为每个部件提供唯一标识,该标识是秘密的,并且不会暴露在硬件逻辑之外。在一些实施例中,安全逻辑503包括高级加密标准(advanced encryption standard,aes),用于在管芯上包裹密钥。在一些实施例中,aes引擎提供加密和/或解密操作。在一些实施例中,安全逻辑503包括差错校正码(error correction code,ecc)引擎来签署和/或验证证书,以及服务器证书。

[0045]

在制造流程期间,服务器或板上的平台信任根注册公钥(从puf值得出的密钥对),该公钥将被用作部件(例如,处理器管芯501)的身份。然后在服务器502或平台信任根与部件之间建立安全通道,以按照美国国家标准与技术研究所(national institute of standards and technology,nist)sp800-56a标准,使用椭圆曲线diffie-hellman(elliptic-curve diffie

–

hellman,ecdh)协议来交换会话密钥。ecdh是密钥协商协议,它允许双方(各自拥有椭圆曲线公钥-私钥对)通过不安全的通道建立共享的秘密。这个共享秘密可被直接用作密钥,或者用于得出另一密钥。

[0046]

然后,这个会话密钥被用来加密会话,以允许密钥的传输。在一些实施例中,由服务器502发送唯一的指令序列,安全逻辑503接收该指令序列以继续进行。根据一些实施例,这些唯一的指令序列仅对服务器502和安全逻辑503来说是已知的。在一些实施例中,puf得出的密钥随后被安全加密地发送到服务器502。然后服务器502生成唯一的密钥,然后这些密钥由安全逻辑503利用相同的puf得出密钥进行包裹来烧熔到熔丝中。任何其他必要的熔合都可在此时或以后完成。这就结束了配设过程。在一些实施例中,只有安全逻辑503被允许在配设过程期间发挥作用,在配设完成进入熔丝之前,没有其他逻辑可被解除门控。

[0047]

然后,密钥被不同的逻辑单元504-1、504-2、至504-n解码并且读取。每个逻辑将密钥(key1、key2)提供给理解的时钟门控逻辑(例如,标记为505-1、505-2、至505-n的时钟门控逻辑1至n)。每个时钟门控逻辑的输出是时钟(例如,时钟1、时钟2、至时钟n)。虽然以使用两个密钥的时钟门控逻辑或驱动器来说明了各种实施例,但可以使用单个密钥或者多于两个密钥。另外,实施例适用于可使用一个或多个加密密钥来锁定或门控的任何逻辑。

[0048]

图6根据一些实施例图示了具有向处理器或片上系统提供加密安全密钥的信任根(root-of-trust,rot)ip块的封装600。封装600包括衬底601、信任根(rot)集成电路(ic)602、处理器603(例如,图8的soc)、以及焊球604。在一些实施例中,加密逻辑401被嵌入在rot ic602中。在一些实施例中,当使用两个加密密钥时,可以有两个不同的rot ic,每个加密密钥一个。在一些实施例中,rot ic 602可被用于在对系统解除门控之前对系统进行认证。在一些实施例中,rot ic 602在主板上。在一些实施例中,rot ic 602与处理器603在同一封装上。在一些实施例中,rot ic 602的功能由服务器502执行,服务器502与处理器603以通信方式耦合。

[0049]

在一些实施例中,rot ic 602包括伪随机数生成器402以生成跳频时间序列。rot ic 602还包括耦合到伪随机生成器的频率合成器404,其中频率合成器接收输入时钟并且生成输出时钟。rot ic 602还包括调制器,用于经由跳频时间序列将指示一个或多个密钥的代码调制到输入时钟上。在一些实施例中,一个或多个密钥被用来对电路进行门控或解

除门控。该电路驻留在处理器603中。在一些实施例中,该电路包括时钟门控逻辑。在一些实施例中,一个或多个密钥包括第一密钥和第二密钥,其中,时钟门控逻辑包括:时序单元,用于接收本地时钟和使能信号;第一异或或者异或非门,用于接收时序单元的输出和第一密钥;第二异或或者异或非门,用于接收本地时钟和第二密钥;以及与门或者与非门,其与第一异或或者异或非门的输出和第二异或或者异或非门的输出相耦合。

[0050]

在一些实施例中,rot ic 602在分开的互连通道上向处理器603提供随机化跳频时间序列和编码的时钟(带有扩频)。在一个示例中,rot ic602包括第一通道来将跳频时间序列传输到处理器603(这是ip块的示例);并且包括第二通道来将输出时钟传输到处理器603。

[0051]

在一些实施例中,处理器603包括解码器406,该解码器406使用随机化跳频时间序列对编码的时钟进行解码,并且提取密钥,这些密钥然后被用于对时钟驱动器进行门控或解除门控。在一些实施例中,处理器603包括熔丝,来存储一个或多个密钥和/或跳频时间序列。在一些实施例中,输入时钟使用跳频时间序列来经历扩频。在一些实施例中,跳频时间序列是低频跳频时间序列(例如,低于500khz)。

[0052]

将rot ic 602与处理器603分开,进一步提高了处理器603的安全性。未经授权出售没有相应rot ic 602的处理器603将使得黑客难以入侵到处理器603中。在一些实施例中,rot ic 602是由与处理器603分开的代工厂制造的。虽然根据使用密钥来对时钟驱动器进行门控说明了各种实施例,但可以使用密钥来禁用或使能任何逻辑或电路(模拟或数字的)。

[0053]

图7根据一些实施例图示了供应加密安全密钥的方法的流程图700,这些加密安全密钥随后被解码来对时钟进行门控或解除门控。虽然流程图700的块被以特定顺序图示,但该顺序可被修改。例如,一些块可在其他块之前被执行,而一些块可被并行执行。在一些实施例中,在软件中执行流程图700的一些或所有过程。在一些实施例中,在硬件中执行流程图700的一些或所有过程。在一些实施例中,在软件和硬件的组合中执行流程图700的一些或所有过程。在一些实施例中,可在一个逻辑中执行流程图700的过程。

[0054]

在块701,时钟缓冲器或驱动器被门控,等待接收可验证的密钥。例如,当处理器(具有这些时钟缓冲器)被上电时,时钟门逻辑或驱动器100-1、100-21和/或100-31被门控(即,时钟传播被暂停)。这些时钟缓冲器或驱动器保持门控状态,从而禁止处理器进行任何有意义的功能,直到加密密钥被解码、验证并且应用于时钟缓冲器或驱动器为止。正如本文所论述的,使用加密密钥的时钟门控的概念可被应用于任何逻辑,例如锁相环、锁频环、电压调节器、对存储器的访问、对io(输入-输出)逻辑的访问、io驱动器的传输,等等。使用加密密钥来禁用ip块和/或处理器的正常功能的概念可针对任何逻辑实现,而不仅仅是时钟门控逻辑或驱动器。

[0055]

在块702,生成伪随机跳频时间序列。伪随机跳频时间序列被用于随机化扩频,而不是使用低频三角波或锯齿波来调制频率合成器404的参考时钟(或输出时钟)。这种伪随机跳频时间序列是解锁加密密钥的关键。在一些实施例中,pwm调制的加密密钥是由低频伪随机跳频时间序列所携带的。为了对pwm调制的加密密钥进行解码,使用伪随机跳频时间序列。

[0056]

在块703,由频率合成器404生成时钟,并且使用伪随机跳频时间序列将扩频应用

于该时钟。这个时钟可以是ip块或处理器的参考时钟。频率合成器404的输入时钟是参考时钟,该参考时钟被用于生成相位锁定或频率锁定的输出时钟。该输出时钟被ip块或处理器进一步用作参考时钟或主时钟。在各种实施例中,使用伪随机跳频时间序列将扩频应用于频率合成器404的输入参考时钟。因此,频率合成器404的输出时钟显示了扩频的效果。在一些实施例中,除了将扩频应用于频率合成器404的输入参考时钟以外或作为其替代,扩频被应用于频率合成器404的输出时钟。

[0057]

在704块,表示特定时钟驱动器的密钥的代码被编码到频率合成器404的输入时钟(例如,参考时钟)。该编码可通过占空比调制或脉冲宽度调制来完成。例如,pwm调制的加密密钥(由pwm 403针对特定时钟门控结构进行调制)被低频伪随机跳频时间序列所携带,该序列被调制到频率合成器404的输入时钟上。为了对pwm调制的加密密钥进行解码,使用伪随机跳频时间序列,因为跳频时间序列是解锁加密密钥的关键。

[0058]

在一些实施例中,解码的或解锁的密钥被安全逻辑保存或存储,如块705所示。在块706,解码器使用伪随机跳频时间序列对加密代码进行解码。因此,密钥被提取出来。在块707,提取的密钥被用于对时钟缓冲器或驱动器或为其生成密钥的任何逻辑解除门控。

[0059]

也可以以用于存储计算机可执行指令(例如,实现本文论述的任何其他过程的指令)的机器可读介质(例如,存储器)的形式来提供实施例的元素(例如,参考各种实施例的流程图)。在一些实施例中,计算平台包括耦合在一起的存储器、处理器、机器可读存储介质(也称为有形机器可读介质)、通信接口(例如,无线或有线接口)、以及网络总线。

[0060]

在一些实施例中,处理器是实现简单的有限状态机以执行参考各种流程图的方法和/或各种实施例等等的数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、通用中央处理单元(central processing unit,cpu)或者低功率逻辑。

[0061]

在一些实施例中,系统的各种逻辑块经由网络总线耦合在一起。可以用任何适当的协议来实现网络总线。在一些实施例中,机器可读存储介质包括如参考各种实施例和流程图所描述的用于参考另一设备计算或测量设备的距离和相对取向的指令(也称为程序软件代码/指令)。

[0062]

与参考各种流程图和/或各种实施例的流程图相关联并且被执行来实现公开的主题的实施例的程序软件代码/指令可实现为如下项的一部分:被称为“程序软件代码/指令”、“操作系统程序软件代码/指令”、“应用程序软件代码/指令”或者简称为“软件”或嵌入在处理器中的固件的操作系统或特定应用、组件、程序、对象、模块、例程或者其他指令序列或者指令序列的组织。在一些实施例中,参考各种流程图和/或各种实施例与流程图相关联的程序软件代码/指令由系统执行。

[0063]

在一些实施例中,与参考各种流程图和/或各种实施例相关联的程序软件代码/指令被存储在计算机可执行存储介质中并且由处理器执行。这里,计算机可执行存储介质是可用于存储程序软件代码/指令和数据的有形机器可读介质,该程序软件代码/指令和数据当被计算设备执行时,使得一个或多个处理器执行可在针对所公开的主题的一个或多个所附权利要求中记载的(一个或多个)方法。

[0064]

有形机器可读介质可包括可执行软件程序代码/指令和数据在各种有形位置中的存储,包括例如rom、易失性ram、非易失性存储器、和/或缓存、和/或本技术中引用的其他有

形存储器。此程序软件代码/指令和/或数据的一些部分可被存储在这些存储装置和存储器设备中的任何一者中。另外,程序软件代码/指令可以是从其他存储装置获得的,包括例如通过集中式服务器或对等网络等等获得,包括互联网。可在不同的时间和在不同的通信会话中或者在同一通信会话中获得软件程序代码/指令和数据的不同部分。

[0065]

(与参考各种流程图和/或各种实施例相关联的)软件程序代码/指令以及数据可在各个软件程序或应用被计算设备执行之前被完全获得。或者,可在执行需要时动态地(例如,刚好及时地)获得软件程序代码/指令和数据的一些部分。或者,获得软件程序代码/指令和数据的这些方式的某种组合可例如针对不同的应用、组件、程序、对象、模块、例程或者其他指令序列或指令序列的组织发生。从而,不要求数据和指令在特定的时刻全部在有形机器可读介质上。

[0066]

有形计算机可读介质的示例包括但不限于可记录和不可记录类型的介质,例如易失性和非易失性存储器设备、只读存储器(rom)、随机访问存储器(ram)、闪存设备、软盘和其他可移除盘、磁存储介质、光存储介质(例如、致密盘只读存储器(cd rom)、数字多功能盘(dvd),等等),等等。软件程序代码/指令可被临时存储在数字有形通信链路中,同时通过这种有形通信链路实现电的、光的、声学的或者其他形式的传播信号,例如载波、红外信号、数字信号,等等。

[0067]

一般而言,有形机器可读介质包括以机器(即,计算设备)可访问的形式提供信息(即,以数字形式存储和/或发送信息,例如数据分组)的任何有形机制,其可被包括在例如通信设备、计算设备、网络设备、个人数字助理、制造工具、移动通信设备(无论其是否能够从通信网络(例如互联网)下载和运行应用和资助应用,例如等等)、或者包括计算设备的任何其他设备中。在一个实施例中,基于处理器的系统采取如下形式或者被包括在如下项内:pda(个人数字助理)、蜂窝电话、笔记本计算机、平板设备、游戏机、机顶盒、嵌入式系统、tv(电视)、个人桌面计算机,等等。或者,在所公开的主题的一些实施例中可以使用传统的通信应用和(一个或多个)补贴应用。

[0068]

图8根据一些实施例图示了具有门控装置的智能设备或者计算机系统或者soc(片上系统),该装置具有逻辑来根据安全密钥对信号或供给进行门控或解除门控。这里的任何块都可具有根据安全密钥对时钟进行门控或解除门控的逻辑。在一些实施例中,soc包括加密引擎,以为平台内的其他ip块生成密钥。要指出的是,图8的具有与任何其他图中的元素相同的标号(或名称)的那些元素可按与所描述的相似的任何方式操作或工作,但不限于此。此智能设备中的任何块都可具有门控装置,该门控装置具有逻辑来对信号或供给进行门控或解除门控。

[0069]

在一些实施例中,设备5500表示适当的计算设备,例如计算平板、移动电话或智能电话、膝上型电脑、桌面型电脑、物联网(internet-of-things,iot)设备、服务器、可穿戴设备、机顶盒、具备无线能力的电子阅读器,等等。将会理解,某些组件被概括示出,并且在设备5500中没有示出这种设备的所有组件。

[0070]

在一示例中,设备5500包括soc(片上系统)5501。soc 5501的示例边界在图8中利用虚线来图示,其中一些示例组件被图示为包括在soc5501内,然而,soc 5501可包括设备5500的任何适当组件。

[0071]

在一些实施例中,设备5500包括处理器5504。处理器5504可包括一个或多个物理

设备,例如微处理器、应用处理器、微控制器、可编程逻辑器件、处理核心,或者其他处理实现,例如多个计算、图形、加速器、i/o和/或其他处理芯片的分解组合。处理器5504执行的处理操作包括对其上执行应用和/或设备功能的操作平台或操作系统的执行。处理操作包括关于与人类用户或与其他设备的i/o(输入/输出)的操作、关于功率管理的操作、关于将计算设备5500连接到另一设备的操作,等等。处理操作还可包括关于音频i/o和/或显示i/o的操作。

[0072]

在一些实施例中,处理器5504包括多个处理核心(也称为核心)5508a、5508b、5508c。虽然在图8中只图示了三个核心5508a、5508b、5508c,但处理器5504可包括任何其他适当数目的处理核心,例如数十个或者甚至数百个处理核心。处理器核心5508a、5508b、5508c可被实现在单个集成电路(ic)芯片上。另外,芯片可包括一个或多个共享和/或私有缓存、总线或互连、图形和/或存储器控制器,或者其他组件。

[0073]

在一些实施例中,处理器5504包括缓存5506。在一示例中,缓存5506的一些区段可专用于个体核心5508(例如,缓存5506的第一区段专用于核心5508a,缓存5506的第二区段专用于核心5508b,等等依此类推)。在一示例中,缓存5506的一个或多个区段可以是两个或更多个核心5508之间共享的。缓存5506可被分割成不同的级别,例如第1级(l1)缓存、第2级(l2)缓存、第3级(l3)缓存,等等。

[0074]

在一些实施例中,处理器核心5504可包括取得单元来取得指令(包括具有条件分支的指令)来供核心5504执行。可以从诸如存储器5530之类的任何存储设备取得指令。处理器核心5504也可包括解码单元来对取得的指令进行解码。例如,解码单元可将取得的指令解码成多个微操作。处理器核心5504可包括调度单元来执行与存储经解码的指令相关联的各种操作。例如,调度单元可保存来自解码单元的数据,直到指令准备好派谴为止,例如,直到解码的指令的所有源值变得可用为止。在一个实施例中,调度单元可调度和/或发出(或派谴)解码的指令到执行单元以便执行。

[0075]

执行单元可在派谴的指令被解码(例如,被解码单元解码)和派谴(例如,被调度单元派谴)之后执行这些指令。在一实施例中,执行单元可包括多于一个执行单元(例如,成像计算单元、图形计算单元、通用计算单元,等等)。执行单元也可执行各种算术操作,例如加法、减法、乘法和/或除法,并且可包括一个或多个算术逻辑单元(arithmetic logic unit,alu)。在一实施例中,协处理器(未示出)可联合执行单元来执行各种算术操作。

[0076]

另外,执行单元可无序地执行指令。因此,处理器核心5504在一个实施例中可以是无序处理器核心。处理器核心5504也可包括引退单元。引退单元可在执行的指令被提交之后引退这些指令。在一实施例中,执行的指令的引退可导致处理器状态被从指令的执行提交、指令使用的物理寄存器被解除分配,等等。处理器核心5504还可包括总线单元来使能处理器核心5504的组件和其他组件之间经由一个或多个总线的通信。处理器核心5504还可包括一个或多个寄存器来存储被核心5504的各种组件访问的数据(例如与指派的app优先级和/或子系统状态(模式)关联有关的值)。

[0077]

在一些实施例中,设备5500包括连通性电路5531。例如,连通性电路5531包括硬件设备(例如,无线和/或有线连接器和通信硬件)和/或软件组件(例如,驱动器、协议栈),来例如使得设备5500能够与外部设备通信。设备5500可与诸如其他计算设备、无线接入点或基站等等之类的外部设备分离。

[0078]

在一示例中,连通性电路5531可包括多种不同类型的连通性。概括而言,连通性电路5531可包括蜂窝连通性电路、无线连通性电路,等等。连通性电路5531的蜂窝连通性电路一般指的是由无线运营商提供的蜂窝网络连通性,例如经由以下所列项来提供:gsm(global system for mobile communications,全球移动通信系统)或者变体或衍生物,cdma(code division multiple access,码分多址接入)或者变体或衍生物,tdm(time division multiplexing,时分复用)或者变体或衍生物,第3代合作伙伴计划(3rd generation partnership project,3gpp)通用移动电信系统(universal mobile telecommunications systems,umts)系统或者变体或衍生物,3gpp长期演进(long-term evolution,lte)系统或者变体或衍生物,3gpp lte高级版(lte-advanced,lte-a)系统或者变体或衍生物,第五代(5g)无线系统或者变体或衍生物,5g移动网络系统或者变体或衍生物,5g新无线电(new radio,nr)系统或者变体或衍生物,或者其他蜂窝服务标准。连通性电路5531的无线连通性电路(或无线接口)指的是非蜂窝的无线连通性,并且可包括个人区域网(例如蓝牙、近场等等)、局域网(例如wi-fi)和/或广域网(例如wimax),和/或其他无线通信。在一示例中,连通性电路5531可包括网络接口,例如有线或无线接口,例如,使得系统实施例可被包含到无线设备中,例如,蜂窝电话或个人数字助理。

[0079]

在一些实施例中,设备5500包括控制中枢5532,该控制中枢5532表示关于与一个或多个i/o设备的交互的硬件设备和/或软件组件。例如,处理器5504可经由控制中枢5532与显示器5522、一个或多个外围设备5524、存储设备5528、一个或多个其他外部设备5529等等中的一个或多个进行通信。控制中枢5532可以是芯片组、平台控制中枢(platform control hub,pch),等等。

[0080]

例如,控制中枢5532说明了连接到设备5500的附加设备的一个或多个连接点,例如,用户可通过这些附加设备与系统交互。例如,可附接到设备5500的设备(例如,设备5529)包括麦克风设备、扬声器或立体声系统、音频设备、视频系统或其他显示设备、键盘或小键盘设备、或者用于特定应用的其他i/o设备,例如读卡器或其他设备。

[0081]

如上所述,控制中枢5532可与音频设备、显示器5522等等交互。例如,通过麦克风或其他音频设备的输入可为设备5500的一个或多个应用或功能提供输入或命令。此外,取代显示输出,或者除了显示输出以外,可提供音频输出。在另一示例中,如果显示器5522包括触摸屏,则显示器5522也充当输入设备,该输入设备可至少部分由控制中枢5532管理。在计算设备5500上也可以有额外的按钮或开关来提供由控制中枢5532管理的i/o功能。在一个实施例中,控制中枢5532管理诸如加速度计、相机、光传感器或其他环境传感器之类的设备,或者可被包括在设备5500中的其他硬件。输入可以是直接用户交互的一部分,以及向系统提供环境输入以影响其操作(例如对噪声的过滤,调整显示器以进行亮度检测,对相机应用闪光灯,或者其他特征)。

[0082]

在一些实施例中,控制中枢5532可利用任何适当的通信协议耦合到各种设备,例如pcie(peripheral component interconnect express,快速外围组件互连)、usb(universal serial bus,通用串行总线)、thunderbolt、高清晰度多媒体接口(high definition multimedia interface,hdmi)、firewire,等等。

[0083]

在一些实施例中,显示器5522表示提供视觉和/或触觉显示来供用户与设备5500交互的硬件(例如,显示设备)和软件(例如,驱动器)组件。显示器5522可包括显示接口、显

示屏、和/或用于向用户提供显示器的硬件设备。在一些实施例中,显示器5522包括向用户提供输出和输入两者的触摸屏(或触摸板)设备。在一示例中,显示器5522可直接与处理器5504通信。显示器5522可以是像在移动电子设备或膝上型电脑设备中那样的内部显示设备或者经由显示接口(例如,displayport等等)附接的外部显示设备中的一个或多个。在一个实施例中,显示器5522可以是头戴式显示器(head mounted display,hmd),例如立体显示设备,用于虚拟现实(virtual reality,vr)应用或增强现实(augmented reality,ar)应用中。

[0084]

在一些实施例中,虽然在附图中没有图示,但除了处理器5504以外(或者取代处理器5504),设备5500还可包括图形处理单元(graphics processing unit,gpu),该图形处理单元包括一个或多个图形处理核心,其可控制在显示器5522上显示内容的一个或多个方面。

[0085]

控制中枢5532(或者平台控制器中枢)可包括硬件接口和连接器,以及软件组件(例如,驱动器、协议栈),来进行例如到外围设备5524的外围连接。

[0086]

将会理解,设备5500既可以是其他计算设备的外围设备,也可以有外围设备连接到它。设备5500可具有“坞接”连接器来连接到其他计算设备,以便例如管理设备5500上的内容(例如,下载和/或上传、改变、同步)。此外,坞接连接器可允许设备5500连接到某些外设,这些外设允许计算设备5500控制例如到视听或其他系统的内容输出。

[0087]

除了专属坞接连接器或其他专属连接硬件以外,设备5500还可经由常见的或者基于标准的连接器来进行外围连接。常见类型可包括通用串行总线(universal serial bus,usb)连接器(其可包括多种不同硬件接口中的任何一种)、包括minidisplayport(mdp)的displayport、高清晰度多媒体接口(high definition multimedia interface,hdmi)、firewire或者其他类型。

[0088]

在一些实施例中,连通性电路5531可耦合到控制中枢5532,例如除了直接耦合到处理器5504以外或者取代直接耦合到处理器5504。在一些实施例中,显示器5522可耦合到控制中枢5532,例如除了直接耦合到处理器5504以外或者取代直接耦合到处理器5504。

[0089]

在一些实施例中,设备5500包括存储器5530,其经由存储器接口5534耦合到处理器5504。存储器5530包括用于存储设备5500中的信息的存储器设备。

[0090]

在一些实施例中,存储器5530包括装置来维持稳定的时钟控制(clocking),如参考各种实施例所述。存储器可包括非易失性存储器设备(如果到存储器设备的电力中断,状态不会变化)和/或易失性存储器设备(如果到存储器设备的电力中断,则状态不确定)。存储器设备5530可以是动态随机访问存储器(dynamic random-access memory,dram)设备、静态随机访问存储器(static random-access memory,sram)设备、闪存设备、相变存储器设备或者具有适当的性能来用作进程存储器的某种其他存储器设备。在一个实施例中,存储器5530可充当设备5500的系统存储器,以存储数据和指令来在一个或多个处理器5504执行应用或进程时使用。存储器5530可存储应用数据、用户数据、音乐、照片、文档或其他数据,以及与设备5500的应用和功能的执行有关的系统数据(无论是长期的还是暂时的)。

[0091]

各种实施例和示例的元素也可以以用于存储计算机可执行指令(例如,实现本文论述的任何其他过程的指令)的机器可读介质(例如,存储器5530)的形式提供。机器可读介质(例如,存储器5530)可包括但不限于闪存、光盘、cd-rom、dvd rom、ram、eprom、eeprom、磁

卡或光卡、相变存储器(phase change memory,pcm)或者适合用于存储电子或计算机可执行指令的其他类型的机器可读介质。例如,本公开的实施例可作为计算机程序(例如,bios)被下载,该计算机程序可经由通信链路(例如,调制解调器或网络连接)借由数据信号被从远程计算机(例如,服务器)传送到请求计算机(例如,客户端)。

[0092]

在一些实施例中,设备5500包括温度测量电路5540,例如用于测量设备5500的各种组件的温度。在一示例中,温度测量电路5540可被嵌入、或者耦合或附接到其温度要被测量和监视的各种组件。例如,温度测量电路5540可测量核心5508a、5508b、5508c、电压调节器5514、存储器5530、soc 5501的主板和/或设备5500的任何适当组件中的一个或多个的温度(或者其内的温度)。在一些实施例中,温度测量电路5540包括低功率混合反向(low power hybrid reverse,lphr)带隙基准(bandgap reference,bgr)和数字温度传感器(digital temperature sensor,dts),其利用亚阈值金属氧化物半导体(metal oxide semiconductor,mos)晶体管和pnp寄生双极结晶体管(bi-polar junction transistor,bjt)器件来形成作为可配置bgr或dts操作模式的基础的反向bgr。lphr体系结构使用低成本mos晶体管和标准的寄生pnp器件。基于反向带隙电压,lphr可作为可配置的bgr工作。通过比较可配置bgr与缩放的基极-发射极电压,该电路也可作为具有线性传递函数的dts来运转,并具有单温度修整以获得高准确度。

[0093]

在一些实施例中,设备5500包括功率测量电路5542,例如用于测量设备5500的一个或多个组件消耗的功率。在一示例中,除了测量功率以外,或者取代测量功率,功率测量电路5542还可测量电压和/或电流。在一示例中,功率测量电路5542可被嵌入、或者耦合或附接到其功率、电压和/或电流消耗要被测量和监视的各种组件。例如,功率测量电路5542可测量由一个或多个电压调节器5514供应的功率、电流和/或电压、供应到soc 5501的功率、供应到设备5500的功率、由设备5504的处理器5500(或任何其他组件)消耗的功率,等等。

[0094]

在一些实施例中,设备5500包括一个或多个电压调节器电路,一般称为电压调节器(voltage regulato,vr)5514。vr 5514按适当的电压水平生成信号,这些信号可被供应来操作设备5500的任何适当组件。仅作为示例,vr 5514被图示为向设备5500的处理器5504供应信号。在一些实施例中,vr 5514接收一个或多个电压标识(voltage identification,vid)信号,并且基于vid信号生成处于适当水平的电压信号。可利用各种类型的vr用于vr 5514。例如,vr 5514可包括“降压”vr、“升压”vr、降压和升压vr的组合、低压差(low dropout,ldo)调节器、开关dc-dc调节器、基于恒定导通时间控制器的dc-dc调节器,等等。降压vr一般用于其中输入电压需要被以小于单位一的比率变换成输出电压的电力输送应用中。升压vr一般用于其中输入电压需要被以大于单位一的比率变换成输出电压的电力输送应用中。在一些实施例中,每个处理器核心具有其自己的vr,该vr被pcu 5510a/b和/或pmic 5512控制。在一些实施例中,每个核心具有分布式ldo的网络来提供对功率管理的高效控制。ldo可以是数字的、模拟的或者是数字或模拟ldo的组合。在一些实施例中,vr 5514包括电流跟踪装置来测量通过(一个或多个)电力供应轨的电流。

[0095]

在一些实施例中,vr 5514包括数字控制方案来管理比例-积分-微分(proportional-integral-derivative,pid)滤波器(也被称为数字iii型补偿器)的状态。数字控制方案控制pid滤波器的积分器实现饱和占空比的非线性控制,在此期间pid的比例

和微分项被设置为0,而积分器及其内部状态(先前值或存储器)被设置为作为当前标称占空比加上deltad之和的占空比。deltad是用于从iccmin到iccmax调节电压调节器的最大占空比增量,并且是可以在流片后设置的配置寄存器。状态机从非线性全开状态(这使输出电压vout回到调节窗口)转移到维持输出电压略高于所需参考电压vref的开环占空比。在按指令的占空比的这个开环状态下经过一段时间后,状态机于是缓降开环占空比值,直到输出电压接近指令的vref为止。这样,来自vr 5514的输出供应上的输出颤动被完全消除(或基本消除),并且只有一个单一的欠冲过渡,这可导致基于比较器延迟和负载的di/dt与可用输出解耦电容的保证vmin。

[0096]

在一些实施例中,vr 5514包括单独的自启动控制器,它在没有熔丝和/或修整信息的情况下发挥作用。自启动控制器保护vr 5514免受大的浪涌电流和电压过冲的影响,同时能够遵循系统施加的可变vid(电压标识)参考渐变。在一些实施例中,自启动控制器使用内置到控制器中的松弛振荡器来设置降压转换器的开关频率。可利用时钟或电流参考来将该振荡器初始化到接近期望的操作频率。vr 5514的输出与振荡器弱耦合,以设置闭环操作的占空比。该控制器是自然偏置的,从而输出电压总是略高于设置点,消除了对任何工艺、电压和/或温度(process,voltage,and/or temperature,pvt)施加的修整的需要。

[0097]

在一些实施例中,设备5500包括一个或多个时钟生成器电路,一般称为时钟生成器5516。时钟生成器5516可按适当的频率水平生成时钟信号,这些信号可被供应给设备5500的任何适当组件。仅作为示例,时钟生成器5516被图示为向设备5500的处理器5504供应时钟信号。在一些实施例中,时钟生成器5516接收一个或多个频率标识(frequency identification,fid)信号,并且基于fid信号以适当的频率生成时钟信号。

[0098]

在一些实施例中,设备5500包括向设备5500的各种组件供应电力的电池5518。仅作为示例,电池5518被图示为在向处理器5504供应电力。虽然在附图中没有图示,但设备5500可包括充电电路,以例如基于从交流电(alternating current,ac)适配器接收的ac电力供应来对电池再充电。

[0099]

在一些实施例中,电池5518周期性地检查实际电池容量或能量,并且充电到预设的电压(例如,4.1v)。电池然后决定电池容量或能量。如果容量或能量不足,那么电池中的装置或者与之相关联的装置就会将充电电压略微增大到容量充足的点(例如,从4.1v到4.11v)。执行周期性检查并且略微增大充电电压的过程,直到充电电压达到规格限制(例如4.2v)为止。本文描述的方案有一些益处,例如可以延长电池寿命,可以降低能量储备不足的风险,可以尽可能地使用突发功率,和/或甚至可以使用更高的突发功率。

[0100]

在一些实施例中,电池5518是多电池系统,具有与工作负载相关的负载共享机制。该机制是一种能量管理系统,它在三种模式中操作:节能模式、平衡器模式和极速模式。节能模式是一种正常模式,其中多个电池(总体示为电池5518)以最小的电阻耗散向其自己的一组负载提供电力。在平衡模式中,电池通过在活跃模式下操作的开关连接,使得共享的电流与相应的电池充电状态成反比。在极速模式中,两个电池都通过开关(例如,接通开关)并联连接,以向处理器或负载提供最大功率。在一些实施例中,电池5518是混合电池,它包括快速充电电池和高能量密度电池。快速充电电池(fast charging,fc)是指能够比高能量密度电池(high energy,he)更快地充电的电池。fc可以是当今的锂离子电池,因为它能够比he更快地充电。在一些实施例中,控制器(电池5518的一部分)优化混合电池的序列和充电

速率,以最大化电池的充电电流和充电速度两者,同时使得电池寿命能够更长。

[0101]

在一些实施例中,充电电路(例如,5518)包括降压-升压转换器。这个降压-升压转换器包括drmos或者drgan器件,用于替代传统降压-升压转换器的半桥。这里的各种实施例是参考drmos来描述的。然而,实施例也适用于drgan。drmos器件由于降低了寄生性和优化了mosfet封装,因此允许了更好的功率转换效率。由于死区时间管理是在drmos内部的,因此死区时间管理比传统的降压-升压转换器更准确,从而使转换效率更高。更高的操作频率允许了更小的电感器尺寸,这进而又降低了包括基于drmos的降压-升压转换器的充电器的z高度。各种实施例的降压-升压转换器包括用于drmos器件的双折自举(dual-folded bootstrap)。在一些实施例中,除了传统的自举电容器以外,还添加了折叠式自举电容器,这些折叠式自举电容器将电感器节点交叉耦合到两组drmos开关。

[0102]

在一些实施例中,设备5500包括功率控制单元(power control unit,pcu)5510(也称为功率管理单元(power management unit,pmu)、功率管理控制器(power management controller,pmc)、功率单元(p单元),等等)。在一示例中,pcu 5510的一些部分可由一个或多个处理核心5508实现,并且pcu 5510的这些部分利用虚线框来象征性图示并且被标注为pcu 5510a。在一示例中,pcu 5510的一些其他部分可在处理核心5508外部实现,并且pcu 5510的这些部分利用虚线框来象征性图示并且被标注为pcu 5510b。pcu 5510可为设备5500实现各种功率管理操作。pcu 5510可包括硬件接口、硬件电路、连接器、寄存器等等,以及软件组件(例如,驱动器、协议栈),来为设备5500实现各种功率管理操作。

[0103]

在各种实施例中,pcu或者pmu 5510以层次化方式组织,形成层次化功率管理(hierarchical power management,hpm)。各种实施例的hpm构建了一种能力和基础设施,允许了对平台的封装级管理,同时仍然迎合可能存在于封装中的构成管芯之间的自治岛屿。hpm并不假定物理分区到域的预定映射。hpm域可与集成在小管芯内部的功能对齐,与小管芯边界对齐,与一个或多个小管芯对齐,与配套管芯对齐,甚至与分立的cxl器件对齐。hpm解决了同一管芯的多个实例的集成,与集成在同一管芯或者单独管芯上的专有功能或者第三方功能相混合,甚至是经由cxl(例如,flexbus)连接的加速器,这些加速器可能在封装内部,或者以分立的形状因子存在。

[0104]

hpm使设计者能够满足可缩放性、模块化和后期绑定的目标。hpm还允许利用可能已经存在于其他管芯上的pmu功能,而不是在平坦方案中被禁用。hpm使得能够管理任何任意的功能集合,与它们的集成水平无关。各种实施例的hpm是可缩放的、模块化的,可与对称的多芯片处理器(multi-chip processor,mcp)一起工作,也可与非对称的mcp一起工作。例如,hpm不需要信号pm控制器和封装基础设施,就能在合理的缩放限制之外增长。hpm使得能够在封装中后期添加管芯,而不需要基础管芯基础设施的改变。hpm解决了不同工艺技术节点的管芯在单个封装中耦合的分解解决方案的需求。hpm还解决了封装内和封装外的配套管芯集成解决方案的需求。

[0105]

在各种实施例中,每个管芯(或者小管芯)包括功率管理单元(pmu)或者p单元。例如,处理器管芯可具有监督者p单元、被监督者p单元、或者双重角色的监督者/被监督者p单元。在一些实施例中,i/o管芯具有其自己的双重角色p单元,例如监督者和/或被监督者p单元。每个管芯中的p单元可以是通用p单元的实例。在一个这样的示例中,所有的p单元具有相同的能力和电路,但被(动态或者静态地)配置为扮演监督者、被监督者和/或两者的角

色。在一些实施例中,用于计算管芯的p单元是计算p单元的实例,而用于io管芯的p单元是不同于计算p单元的io p单元的实例。取决于角色,p单元获取特定的责任来管理多芯片模块和/或计算平台的功率。虽然各种p单元被描述为多芯片模块或者片上系统中的管芯,但p单元也可以是外部设备的一部分,例如i/o设备的一部分。

[0106]

这里,各种p单元不一定是相同的。hpm体系结构可操作类型非常不同的p单元。p单元的一个共同特征是,它们被预期接收hpm消息,并且被预期能够理解这些消息。在一些实施例中,io管芯的p单元可能与计算管芯的p单元不同。例如,io p单元中的每一类寄存器的寄存器实例的数目与计算管芯的p单元中的不同。io管芯有能力成为cxl连接器件的hpm监督器,但计算管芯可能不需要有这种能力。io管芯和计算管芯还具有不同的固件流程,并且可能具有不同的固件镜像。这些都是实现方式可做出的选择。hpm体系结构可选择具有一个超集固件镜像,并且选择性地执行与固件所关联的管芯类型相关的流程。或者,对于每个p单元类型可以有一个客户固件;它可允许针对每个p单元类型的固件存储要求的大小更加精简。

[0107]

每个管芯中的p单元可被配置为监督者p单元、被监督者p单元或者具有监督者/被监督者的双重角色。这样,p单元可为各种域执行监督者或被监督者的角色。在各种实施例中,p单元的每个实例能够自主地管理本地专用资源,并且包含用于聚合数据和在实例间通信的结构,以使得被配置为共享资源监督者的实例能够进行共享资源管理。提供了一种基于消息和导线的基础设施,它可被复制和配置来促进多个p单元之间的管理和流动。

[0108]

在一些实施例中,功率和热阈值由监督者p单元传达给被监督者p单元。例如,监督者p单元了解每个管芯的工作负载(当前和未来)、每个管芯的功率测量值以及其他参数(例如,平台级功率边界),并且为每个管芯确定新的功率限制。这些功率限制随后由监督者p单元经由一个或多个互连和架构被传达给被监督者p单元。在一些实施例中,架构表示一组架构和互连,包括第一架构、第二架构和快速响应互连。在一些实施例中,第一架构用于监督者p单元和被监督者p单元之间的共同通信。这些共同通信包括基于若干个因素(例如,未来的工作负载、用户行为,等等)规划的管芯的电压、频率和/或功率状态的变化。在一些实施例中,第二架构用于监督者p单元和被监督者p单元之间的更高优先级的通信。更高优先级的通信的示例包括由于可能的热失控条件、可靠性问题等等而要扼制的消息。在一些实施例中,快速响应互连被用于传达所有管芯的快速或者硬扼制。在此情况下,例如,监督者p单元可向所有其他p单元发送快速扼制消息。在一些实施例中,快速响应互连是传统的互连,其功能可由第二架构执行。

[0109]

各种实施例的hpm体系结构实现了对称和/或非对称管芯的可缩放性、模块化和后期绑定。这里,对称管芯是相同大小、类型和/或功能的管芯,而非对称管芯是不同大小、类型和/或功能的管芯。层次化方案还允许了利用可能已经存在于其他管芯上的pmu功能,而不是在传统的平坦功率管理方案中被禁用。hpm并不假定物理分区到域的预定映射。hpm域可与集成在小管芯内部的功能对齐,与小管芯边界对齐,与一个或多个小管芯对齐,与配套管芯对齐,甚至与分立的cxl器件对齐。hpm使得能够管理任何任意的功能集合,与它们的集成水平无关。在一些实施例中,基于一个或多个因素宣布p单元为监督者p单元。这些因素包括存储器大小、物理约束(例如,引脚输出的数目)和传感器的位置(例如,温度、功率消耗,等等),以确定处理器的物理限制。

[0110]

各种实施例的hpm体系结构提供了一种缩放功率管理的手段,使得单个p单元实例不需要意识到整个处理器。这使得功率管理的颗粒度能够更小,并且改善了响应时间和有效性。层次化结构维持了对用户的单片视图。例如,在操作系统(os)级别,hpm体系结构给予os单一的pmu视图,即使pmu在物理上是分布在一个或多个监督者-被监督者配置中的。

[0111]

在一些实施例中,hpm体系结构是集中式的,其中一个监督者控制所有被监督者。在一些实施例中,hpm体系结构是分散的,其中各种管芯中的各种p单元通过对等通信控制整体功率管理。在一些实施例中,hpm体系结构是分布式的,其中对于不同的域有不同的监督者。分布式体系结构的一个示例是树状体系结构。

[0112]

在一些实施例中,设备5500包括功率管理集成电路(power management integrated circuit,pmic)5512,以例如为设备5500实现各种功率管理操作。在一些实施例中,pmic 5512是可重配置功率管理ic(reconfigurable power management ic,rpmic)和/或imvp(mobile voltage positioning,移动电压定位)。在一示例中,pmic在与处理器5504分离的ic管芯内。这可为设备5500实现各种功率管理操作。pmic 5512可包括硬件接口、硬件电路、连接器、寄存器等等,以及软件组件(例如,驱动器、协议栈),来为设备5500实现各种功率管理操作。

[0113]

在一示例中,设备5500包括pcu 5510或pmic 5512中的一者或两者。在一示例中,pcu 5510或者pmic 5512中的任何一者可在设备5500中不存在,因此这些组件是利用虚线来图示的。

[0114]

设备5500的各种功率管理操作可由pcu 5510、由pmic 5512或者由pcu 5510和pmic 5512的组合来执行。例如,pcu 5510和/或pmic 5512可为设备5500的各种组件选择功率状态(例如,p状态)。例如,pcu 5510和/或pmic 5512可为设备5500的各种组件选择功率状态(例如,根据acpi(advanced configuration and power interface,高级配置和电力接口)规范)。仅作为示例,pcu 5510和/或pmic 5512可使得设备5500的各种组件转变到睡眠状态、转变到活跃状态、转变到适当的c状态(例如,c0状态,或者另一适当的c状态,根据acpi规范),等等。在一示例中,pcu 5510和/或pmic 5512可控制由vr 5514输出的电压和/或由时钟生成器输出的时钟信号的频率,例如分别通过输出vid信号和/或fid信号。在一示例中,pcu 5510和/或pmic 5512可控制电池功率使用、电池5518的充电以及与功率节省操作有关的特征。

[0115]

时钟生成器5516可包括锁相环(phase locked loop,pll)、锁频环(frequency locked loop,fll)、或者任何适当的时钟源。在一些实施例中,处理器5504的每个核心具有其自己的时钟源。这样,每个核心可按独立于其他核心的操作频率的频率来操作。在一些实施例中,pcu 5510和/或pmic 5512执行自适应或者动态频率缩放或调整。例如,如果核心没有以其最大功率消耗阈值或限度在操作,则可增大该处理器核心的时钟频率。在一些实施例中,pcu 5510和/或pmic 5512确定处理器的每个核心的操作条件,并且当pcu 5510和/或pmic 5512确定核心在以低于目标性能水平操作时,适时地调整该核心的频率和/或电力供应电压,而核心钟控源(例如,该核心的pll)不会失去锁定。例如,如果核心在从电力供应轨汲取电流,该电流小于为该核心或处理器5504分配的总电流,则pcu 5510和/或pmic 5512可临时增大对于该核心或处理器5504的功率汲取(例如,通过增大时钟频率和/或电力供应电压水平),使得该核心或处理器5504可以按更高的性能水平来运转。这样,可以为处理器

5504临时增大电压和/或频率,而不会违反产品可靠性。

[0116]

在一示例中,pcu 5510和/或pmic 5512可例如至少部分基于从功率测量电路5542、温度测量电路5540接收测量、接收电池5518的充电水平、和/或接收可用于功率管理的任何其他适当的信息,来执行功率管理操作。为此,pmic 5512通信地耦合到一个或多个传感器来感测/检测对于系统/平台的功率/热行为具有影响的一个或多个因素中的各种值/变化。一个或多个因素的示例包括电流、电压垂落、温度、操作频率、操作电压、功率消耗、核心间通信活动,等等。这些传感器中的一个或多个可设在计算系统的一个或多个组件或者逻辑/ip块的物理近邻(和/或与其热接触/耦合)。此外,(一个或多个)传感器在至少一个实施例中可直接耦合到pcu 5510和/或pmic 5512以允许pcu 5510和/或pmic 5512至少部分基于由这些传感器中的一个或多个检测到的(一个或多个)值来管理处理器核心能量。

[0117]

还图示了设备5500的示例软件栈(虽然没有图示该软件栈的所有元素)。仅作为示例,处理器5504可执行应用程序5550、操作系统5552、一个或多个功率管理(power management,pm)特定应用程序(例如,一般称为pm应用5558),等等。pm应用5558也可被pcu 5510和/或pmic 5512执行。os 5552也可包括一个或多个pm应用5556a、5556b、5556c。os 5552也可包括各种驱动器5554a、5554b、5554c等等,其中一些可以专用于功率管理目的。在一些实施例中,设备5500还可包括基本输入/输出系统(basic input/output system,bios)5520。bios 5520可与os 5552通信(例如,经由一个或多个驱动器5554),与处理器5504通信,等等。

[0118]

例如,pm应用5558、5556、驱动器5554、bios 5520等等中的一个或多个可用于实现功率管理特定任务,例如控制设备5500的各种组件的电压和/或频率,控制设备5500的各种组件的唤醒状态、睡眠状态和/或任何其他适当的功率状态,控制电池功率使用、电池5518的充电、与功率节省操作有关的特征,等等。

[0119]

在一些实施例中,电池5518是锂金属电池,具有压力室,以使电池上的压力均匀。压力室由金属板(例如均压板)支撑,用于给电池均匀的压力。压力室可包括受压气体、弹性材料、弹簧板,等等。压力室的外皮可以自由弯曲,其边缘受到(金属)皮肤的约束,但仍在压缩电池单元的板上施加均匀的压力。压力室给电池以均匀的压力,这用于实现高能量密度的电池,例如,电池寿命增加20%。

[0120]

在一些实施例中,电池5518包括混合技术。例如,(一个或多个)高能量密度电荷(例如,锂离子电池)携带设备和低能量密度电荷携带设备(例如,超级电容器)的混合被用作电池或者存储设备。在一些实施例中,控制器(例如,硬件、软件或者它们的组合)被用于分析峰值功率模式,并且使得对基于高能量密度电荷携带设备的电池单元的整体寿命的影响最小化,同时使峰值功率消除功能的服务时间最大化。该控制器可以是电池5518的一部分或者p单元5510b的一部分。

[0121]

在一些实施例中,在pcu 5510a/b上执行的pcode具有允许额外的计算和遥测资源用于pcode的运行时间支持的能力。这里pcode指的是由pcu 5510a/b执行以管理soc 5501的性能的固件。例如,pcode可为处理器设置频率和适当的电压。pcode的一部分可经由os 5552来访问。在各种实施例中,提供了机制和方法,这些机制和方法基于工作负载、用户行为和/或系统条件来动态地改变能量性能偏好(energy performance preference,epp)值。在os 5552和pcode之间可能有定义明确的接口。该接口可允许或者促进几个参数的软件配

置和/或可向pcode提供提示。作为示例,一epp参数可告知pcode算法是性能还是电池寿命更重要。

[0122]

这种支持也可由os 5552完成,其方式是包括机器学习支持作为os 5552的一部分,并且通过机器学习预测来调节os提示给硬件(例如,soc 5501的各种组件)的epp值,或者通过以与动态调优技术(dynamic tuning technology,dtt)驱动器所做的类似的方式将机器学习预测递送给pcode。在这种模式中,os 5552可看到与dtt可用的遥测集合相同的遥测集合。作为dtt机器学习提示设置的结果,pcode可调整其内部算法,以实现激活类型的机器学习预测之后的最优功率和性能结果。作为示例,pcode可增大对处理器利用率变化的责任,以使能对用户活动的快速响应,或者可通过减小对处理器利用率的责任或者通过调整能量节省优化以节省更多的功率和增大性能损失来增大对于能量节省的偏向。这种方案可促进节省更多的电池寿命,以防使能的活动的类型相对于系统能够使能的失去一些性能水平。pcode可包括用于动态epp的算法,该算法可取得两个输入,一个来自os 5552,另一个来自软件,例如dtt,并且可以选择性地选择提供更高的性能和/或响应性。作为此方法的一部分,pcode可在dtt中使能一个选项来对于不同类型的活动调整其对dtt的反应。

[0123]

在一些实施例中,pcode改善了soc在电池模式中的性能。在一些实施例中,pcode允许了电池模式中的大幅提高的soc峰值功率极限水平(从而允许了更高的turbo性能)。在一些实施例中,pcode实现了功率扼制,并且是英特尔的动态调优技术(dtt)的一部分。在各种实施例中,峰值功率极限被称为pl4。然而,实施例适用于其他峰值功率极限。在一些实施例中,pcode以防止系统意外关机(或者黑屏)的方式设置vth阈值电压(平台将对soc进行扼制的电压水平)。在一些实施例中,pcode根据阈值电压(vth)计算psoc,pk soc峰值功率极限(例如,pl4)。这是两个依从的参数,如果一个被设置,则另一个可被计算出来。pcode被用于基于系统参数以及操作的历史来最优地设置一个参数(vth)。在一些实施例中,pcode提供了一种方案来基于可用电池功率(变化缓慢)动态地计算扼制水平(psoc,th)并且设置soc扼制峰值功率(psoc,th)。在一些实施例中,pcode基于psoc,th决定频率和电压。在这种情况下,扼制事件对soc性能的负面影响较小。各种实施例提供了一种允许最大性能(pmax)框架来进行操作的方案。

[0124]

在一些实施例中,vr 5514包括电流传感器,用于感测和/或测量通过vr 5514的高侧开关的电流。在一些实施例中,电流传感器使用在反馈中带有电容耦合输入的放大器,以感测放大器的输入偏移,其可在测量期间来进行补偿。在一些实施例中,在反馈中带有电容耦合输入的放大器被用来在输入共模规格宽松的区域中操作放大器,从而使反馈环增益和/或带宽更高。在一些实施例中,在反馈中带有电容耦合输入的放大器被用来从转换器输入电压操作传感器,其方式是通过采用高psrr(电力供应抑制比)调节器来创造一个局部、干净的供应电压,这对开关区域中的电力网造成更少的干扰。在一些实施例中,该设计的一个变体可用于对输入电压和控制器供应之间的差异进行采样,并将其重创建于电源的漏极电压和复制开关之间。这允许了传感器不被暴露于供电电压。在一些实施例中,在反馈中带有电容耦合输入的放大器被用来补偿电流感测期间输入电压中的与电力输送网络相关(pdn相关)的变化。

[0125]

一些实施例使用三个组件来基于usb type-c设备5529的状态调整soc 5501的峰值功率。这些组件包括os峰值功率管理器(os 5552的一部分)、usb type-c连接器管理器

(os 5552的一部分)、以及usb type-c协议设备驱动器(例如,驱动器5554a、5554b、5554c之一)。在一些实施例中,当usb type-c电力宿设备附接到soc 5501或者与soc 5501脱离时,usb type-c连接器管理器向os峰值功率管理器发送同步请求,并且当电力宿转变设备状态时,usb type-c协议设备驱动器向峰值功率管理器发送同步请求。在一些实施例中,当usb type-c连接器附接到电力宿并且活跃(例如,高功率设备状态)时,峰值功率管理器从cpu取得功率预算。在一些实施例中,当usb type-c连接器脱离或者附接并且电力宿设备空闲(最低设备状态)时,峰值功率管理器将功率预算还给cpu以获得性能。

[0126]

在一些实施例中,提供了逻辑来为bios加电流程和睡眠退出流程(例如,s3、s4和/或s5)动态地挑选最佳操作处理核心。对引导处理器(bootstrap processor,bsp)的选择被转移到早期加电时间,而不是在任何时间的固定硬件选择。为了获得最大的启动性能,该逻辑在早期加电时选择最快的胜任核心作为bsp。此外,为了获得最大的功率节省,该逻辑选择最高能效的核心作为bsp。选择bsp的处理器或切换发生在启动以及加电流程(例如,s3、s4和/或s5流程)期间。

[0127]

在一些实施例中,这里的存储器是以多级存储器体系结构组织的,并且其性能由分散方案来支配。该分散方案包括p单元5510和存储器控制器。在一些实施例中,该方案基于应用在如何使用远离处理器核心的存储器级别,对于平台5500中逐渐远离处理器的存储器级别,动态地平衡若干个参数,例如功率、热能、成本、时延和性能。在一些示例中,对远端存储器(fm)的状态的决策作出是分散的。例如,处理器功率管理单元(p单元)、近端存储器控制器(nmc)和/或远端存储器主机控制器(fmhc)在其各自的级别上对fm的功率和/或性能状态作出决策。这些决策被协调起来,以便在给定的时间内提供fm的最优功率和/或性能状态。存储器的功率和/或性能状态自适应地变化,以适应不断变化的工作负载和其他参数,即使当(一个或多个)处理器处于特定功率状态中时。

[0128]

在一些实施例中,实现了硬件和软件协调处理器功率状态策略(例如,c-状态的策略),该策略通过考虑在进入空闲的核心上预期调度的线程的性能和/或响应性需求,提供最优的功率状态选择,以为运行用户关键任务的核心实现改善的每周期指令(instructions per cycle,ipc)和性能。该方案提供了为在片上系统上运行的重要和/或用户关键的线程提供响应性增益的能力。耦合到多个处理核心的p单元5510接收来自操作系统5552的提示,该提示指示出基于情境切换中的线程的优先级,对于多个处理核心中的至少一个处理核心的功率状态或性能状态的偏向。

[0129]

说明书中提及“一实施例”、“一个实施例”、“一些实施例”或者“其他实施例”的意思是联系这些实施例描述的特定特征、结构或特性被包括在至少一些实施例中,但不一定是所有实施例中。“一实施例”、“一个实施例”或“一些实施例”的各种出现不一定全都指的是相同实施例。如果说明书陈述“可”、“可能”或者“可以”包括某一组件、特征、结构或特性,那么并不是必须要包括该特定组件、特征、结构或特性。如果说明书或权利要求提及“一”元素,那么并不意味着只有一个该元素。如果说明书或权利要求提及“一额外”元素,那么并不排除有多于一个额外元素。

[0130]

在整个说明书各处,以及在权利要求中,术语“连接”的意思是直接连接,例如连接的事物之间的电连接、机械连接或磁连接,没有任何中间设备。

[0131]

术语“耦合”的意思是直接或间接连接,例如连接的事物之间的直接电连接、机械

连接或磁连接,或者通过一个或多个无源或有源中间设备的间接连接。

[0132]

这里的术语“邻近”一般指的是一个事物的位置与另一事物挨着(例如,紧挨着或者接近并且其间有一个或多个事物)或者毗邻(例如,与其邻接)。

[0133]

术语“电路”或“模块”可以指被布置为与彼此合作来提供期望的功能的一个或多个无源和/或有源组件。

[0134]

术语“信号”可以指至少一个电流信号、电压信号、磁信号、或者数据/时钟信号。“一”和“该”的含义包括多数指代。“在

……

中”的含义包括“在

……

中”和“在

……

上”。

[0135]

术语“模拟信号”是任何这样的连续信号:对于该连续信号,该信号的时变特征(变量)是某个其他时变量的表示,即,类似于另一时变信号。

[0136]

术语“数字信号”是这样的物理信号:其是例如任意比特流的或者数字化的(采样并且模数转换的)模拟信号的离散值(量化离散时间信号)的序列的表示。

[0137]

术语“缩放”一般是指将某个设计(图解和布局)从一个工艺技术转换到另一个工艺技术并且可随后减小布局面积。在一些情况下,缩放也指从一个工艺技术到另一个工艺技术扩大设计的规模并且可随后增大布局面积。术语“缩放”一般也指在同一技术节点内缩小或扩大布局和器件的规模。术语“缩放”还可以指相对于另一参数(例如电力供应水平)调整信号频率(例如,减慢或加速——即分别是缩小或放大)。

[0138]

术语“基本上”、“接近”、“大致”、“近似”和“大约”一般指在目标值的 /-10%内。

[0139]

除非另有指明,否则使用序数形容词“第一”、“第二”和“第三”等等来描述共同对象只是表明相似对象的不同实例被引用,而并不打算暗示这样描述的对象必须在时间上、空间上、排名上或者以任何其他方式处于给定的序列中。

[0140]

对于本公开而言,短语“a和/或b”和“a或b”的意思是(a)、(b)或者(a和b)。对于本公开而言,短语“a、b和/或c”的意思是(a)、(b)、(c)、(a和b)、(a和c)、(b和c)或者(a、b和c)。

[0141]

说明书中和权利要求中的术语“左”、“右”、“前”、“后”、“顶”、“底”、“上”、“下”等等(如果有的话)是用于描述性目的的,而并不一定用于描述永久的相对位置。

[0142]

要指出,附图的具有与任何其他附图的元素相同的标号(或名称)的那些元素可按与所描述的相似的任何方式来操作或工作,但不限于此。

[0143]

对于实施例而言,这里描述的各种电路和逻辑块中的晶体管是金属氧化物半导体(metal oxide semiconductor,mos)晶体管或其衍生物,其中mos晶体管包括漏极、源极、栅极和体端子。晶体管和/或mos晶体管衍生物也包括三栅和finfet晶体管、全包围栅圆柱体晶体管、隧道效应fet(tunneling fet,tfet)、方形线晶体管、或者矩形带状晶体管、铁电fet(ferroelectric fet,fefet)或者像碳纳米管或自旋器件之类的实现晶体管功能的其他器件。mosfet对称源极和漏极端子是相同的端子并且在这里可被互换使用。另一方面,tfet器件具有非对称源极和漏极端子。本领域技术人员将会明白,在不脱离本公开的范围的情况下,可以使用其他晶体管,例如双极结晶体管(bjt pnp/npn)、bicmos、cmos等等。

[0144]

这里的术语“管芯”(die)一般是指一块连续的半导体材料(例如硅),其中晶体管或者构成处理器核心的其他组件可位于其中。多核心处理器可在单个管芯上具有两个或更多个处理器,但另一种情况是,可分别在两个或更多个管芯上提供两个或更多个处理器。每个管芯具有专用的功率控制器或者功率控制单元(p单元),其可动态或者静态地被配置为监督者或者被监督者。在一些示例中,管芯具有相同的尺寸和功能,即,对称的核心。然而,

管芯也可以是不对称的。例如,一些管芯的尺寸和/或功能与其他管芯不同。每个处理器也可以是小管芯或者小芯片。

[0145]

这里的术语“小管芯(dielet)”或者“小芯片(chiplet)”一般是指物理上分立的半导体管芯,通常以如下方式与相邻的管芯连接:使跨管芯边界的架构像单个架构那样运作,而不是作为两个分立的架构运作。从而,至少一些管芯可以是小管芯。每个小管芯可包括一个或多个p单元,它们可动态或静态地被配置为监督者、被监督者或者两者。

[0146]

这里的术语“架构(fabric)”一般是指具有一组已知的源、目的地、路由规则、拓扑和其他属性的通信机制。源和目的地可以是任何类型的数据处理功能单元,例如功率管理单元。架构可以是沿着管芯的x-y平面的二维跨越和/或沿着垂直和水平放置的管芯的堆叠的x-y-z平面的三维(3d)跨越。单个架构可跨越多个管芯。架构可采取任何拓扑,例如网状拓扑、星形拓扑、菊链状拓扑。架构可以是具有多个代理的片上网络(network-on-chip,noc)的一部分。这些代理可以是任何功能单元。

[0147]

在此,术语“处理器核心”一般是指独立的执行单元,它可在某个时间与其他核心并行地运行一个程序线程。处理器核心可包括专用的功率控制器或者功率控制单元(p单元),其可被动态或者静态地配置为监督者或者被监督者。在一些示例中,这个专用p单元也被称为自主p单元。在一些示例中,所有的处理器核心都具有相同的尺寸和功能,即,对称的核心。然而,处理器核心也可以是不对称的。例如,一些处理器核心的尺寸和/或功能与其他处理器核心不同。处理器核心可以是虚拟处理器核心或者物理处理器核心。

[0148]

这里,术语“互连”是指两个或更多个点或节点之间的通信链路,或者通道。它可包括一个或多个单独的传导路径,例如导线、通孔、波导、无源组件和/或有源组件。它也可包括架构。在一些实施例中,p单元经由接口与os耦合。

[0149]

这里,术语“接口”一般是指用于与互连进行通信的软件和/或硬件。接口可包括逻辑和i/o驱动器/接收器,以通过互连或者一条或多条导线发送和接收数据。

[0150]

这里,术语“域”(domain)一般是指具有类似属性(例如,电源电压、操作频率、电路或逻辑的类型和/或工作负载类型)和/或由特定代理控制的逻辑或者物理周界。例如,域可以是由特定的监督者控制的一组逻辑单元或者功能单元。域也可被称为自主周界(autonomous perimeter,ap)。域可以是整个片上系统(soc)或者片上系统的一部分,并且由p单元管理。

[0151]

这里,术语“监督者”(supervisor)一般是指功率控制器或者功率管理单元(“p单元”),其单独或者与一个或多个其他p单元合作,监视和管理一个或多个关联的功率域的功率和性能相关参数。功率/性能相关参数可包括但不限于域功率、平台功率、电压、电压域电流、管芯电流、负载线、温度、设备时延、利用率、时钟频率、处理效率、当前/未来工作负载信息以及其他参数。它可为一个或多个域确定新的功率或性能参数(限制、平均操作,等等)。这些参数随后可经由一个或多个架构和/或互连,被传达给被监督者p单元,或者直接传达给被控制或者监视的实体,例如vr或者时钟扼制控制寄存器。监督者了解一个或多个管芯的工作负载(当前和未来)、一个或多个管芯的功率测量值和其他参数(例如,平台级功率边界),并且确定一个或多个管芯的新功率限制。这些功率限制随后由监督者p单元经由一个或多个架构和/或互连被传达给被监督者p单元。在一个管芯有一个p单元的示例中,监督者(svor)p单元也被称为监督者管芯。

[0152]

这里的术语“被监督者”(supervisee)一般是指功率控制器或者功率管理单元(“p单元”),其单独或者与一个或多个其他p单元合作,监视和管理一个或多个关联的功率域的功率和性能相关参数,并且接收来自监督者的指令,为其关联的功率域设置功率和/或性能参数(例如,电源电压、操作频率、最大电流、扼制阈值,等等)。在一个管芯有一个p单元的示例中,被监督者(svee)p单元也可被称为被监督者管芯。注意,p单元可作为svor、svee或者同时作为svor/svee p单元。

[0153]

此外,在一个或多个实施例中可按任何适当的方式来组合特定的特征、结构、功能或特性。例如,在与两个实施例相关联的特定特征、结构、功能或特性不互斥的任何地方,可将第一实施例与第二实施例相组合。

[0154]

虽然已结合其特定实施例描述了本公开,但本领域普通技术人员根据前述描述将清楚这种实施例的许多替换、修改和变化。本公开的实施例打算包含落在所附权利要求的宽广范围内的所有这种替换、修改和变化。

[0155]

此外,为了图示和论述的简单,并且为了不模糊本公开,在给出的附图内可能示出或者不示出到集成电路(ic)芯片和其他组件的公知电源/接地连接。另外,可以框图形式示出布置以避免模糊本公开,并且同时也考虑到了如下事实:关于这种框图布置的实现的具体细节是高度取决于要在其内实现本公开的平台的(即,这种具体细节应当完全在本领域技术人员的视野内)。在阐述具体细节(例如,电路)以便描述本公开的示例实施例的情况下,本领域技术人员应当清楚,没有这些具体细节,或者利用这些具体细节的变体,也可实现本公开。从而说明书应当被认为是说明性的,而不是限制性的。

[0156]

以下示例涉及进一步实施例。示例中的具体细节可被用在一个或多个实施例中的任何地方。也可对于方法或过程实现本文描述的装置的所有可选特征。可按任何组合来组合这些示例。例如,示例4可与示例2相组合。

[0157]

示例1:一种装置,包括:伪随机生成器,用于生成跳频时间序列;与所述伪随机生成器相耦合的频率合成器,该频率合成器用于接收输入时钟并且生成输出时钟;以及调制器,用于经由所述跳频时间序列将指示一个或多个密钥的代码调制到所述输入时钟上。

[0158]

示例2:如示例1所述的装置,其中所述一个或多个密钥被用于对电路进行门控或解除门控。

[0159]

示例3:如示例2所述的装置,其中所述电路包括时钟门控逻辑或者电力门控电路。

[0160]

示例4:如示例3所述的装置,其中所述一个或多个密钥包括第一密钥和第二密钥,其中所述时钟门控逻辑包括:时序单元,用于接收本地时钟和使能信号;第一异或或者异或非门,用于接收所述时序单元的输出和所述第一密钥;第二异或或者异或非门,用于接收所述本地时钟和所述第二密钥;以及与门或者与非门,用于与所述第一异或或者异或非门的输出和所述第二异或或者异或非门的输出相耦合。

[0161]

示例5:如示例1所述的装置,包括:第一通道,用于将所述跳频时间序列传输到知识产权(ip)块;以及第二通道,用于将所述输出时钟传输到所述ip块。

[0162]

示例6:如示例5所述的装置,其中所述ip块包括解码器,用于从所述输出时钟中提取所述一个或多个密钥。

[0163]

示例7:如示例5所述的装置,其中所述ip块包括熔丝,用于存储所述一个或多个密钥和/或所述跳频时间序列。

[0164]

示例8:如示例1所述的装置,其中所述输入时钟经历使用所述跳频时间序列的扩频。

[0165]

示例9:如示例1所述的装置,其中所述跳频时间序列是低频跳频时间序列。

[0166]

示例10:如示例1所述的装置,其中所述频率合成器包括锁相环或者锁频环。

[0167]

示例11:如示例1所述的装置,包括解调器,用于从由所述频率合成器生成的时钟中提取所述一个或多个密钥。

[0168]

示例12:一种装置,包括:第一通道,用于接收由用于生成跳频时间序列的伪随机生成器生成的跳频时间序列;以及第二通道,用于接收来自频率合成器的输出,其中所述频率合成器的输入时钟被经由所述跳频时间序列用代码来调制,其中所述代码指示一个或多个密钥。

[0169]

示例13:如示例11所述的装置,包括解码器,用于利用所述跳频时间序列提取所述一个或多个密钥。

[0170]

示例14:如示例11所述的装置,包括电路,该电路根据所述一个或多个密钥被门控或解除门控。

[0171]

示例15:如示例14所述的装置,其中所述电路包括时钟门控逻辑或者电力门控逻辑。

[0172]

示例16:如示例15所述的装置,其中所述一个或多个密钥包括第一密钥和第二密钥,其中所述时钟门控逻辑包括:时序单元,用于接收本地时钟和使能信号;第一异或或者异或非门,用于接收所述时序单元的输出和所述第一密钥;第二异或或者异或非门,用于接收所述本地时钟和所述第二密钥;以及与门或者与非门,其与所述第一异或或者异或非门的输出和所述第二异或或者异或非门的输出相耦合。

[0173]

示例17:如示例11所述的装置,包括熔丝,用于存储所述一个或多个密钥和/或所述跳频时间序列。

[0174]

示例18:如示例11所述的装置,其中所述输入时钟经历使用所述跳频时间序列的扩频。

[0175]

示例19:如示例11所述的装置,其中所述跳频时间序列是低频跳频时间序列。

[0176]

示例20:一种封装,包括:衬底;所述衬底上的处理器;以及所述衬底上的集成电路,该集成电路包括信任根,该信任根包括:伪随机生成器,用于生成跳频时间序列;与所述伪随机生成器相耦合的频率合成器,该频率合成器用于接收输入时钟并且生成输出时钟;以及调制器,用于经由所述跳频时间序列将指示一个或多个密钥的代码调制到所述输入时钟上,其中所述跳频时间序列和所述输出时钟被发送到所述处理器。

[0177]

示例21:如示例20所述的封装,其中所述处理器包括时钟门控逻辑,其中所述一个或多个密钥包括第一密钥和第二密钥,其中所述时钟门控逻辑包括:时序单元,用于接收本地时钟和使能信号;第一异或或者异或非门,来接收所述时序单元的输出和所述第一密钥;第二异或或者异或非门,用于接收所述本地时钟和所述第二密钥;以及与门或者与非门,用于与所述第一异或或者异或非门的输出和所述第二异或或者异或非门的输出相耦合。

[0178]

提供了摘要,其将允许读者确定本技术公开的性质和主旨。摘要是在如下理解下提交的:它不会被用于限制权利要求的范围或含义。特此将所附权利要求并入到详细描述中,其中每个权利要求独立作为一个单独的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。