1.本公开涉及对可以在诸如现场可编程门阵列(fpga)、专用集成电路(asic)等之类的集成电路设备上仿真的集成电路系统的非破坏性(non-destructive)读回和写回。

背景技术:

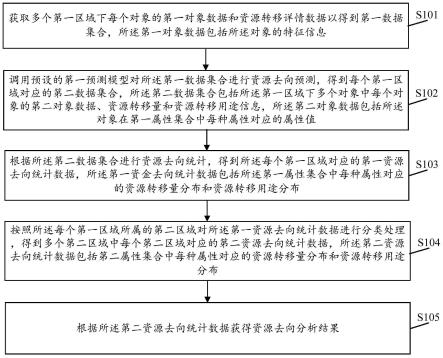

2.本节旨在向读者介绍可能与本公开的各种方面相关的本领域的各种方面,这些方面在下面描述和/或要求保护。该讨论被认为有助于向读者提供背景信息以促进更好地理解本公开的各种方面。因此,可以理解的是,这些陈述将根据这一点阅读,而不是作为对现有技术的承认。

3.集成电路设备可以用于各种目的或应用,并且可编程逻辑器件可以用于执行这些功能。可编程逻辑器件的设计可能受到可用的硬件资源的量的限制。例如,fpga设备可以用于对具有非破坏性读回和写回能力的asic设备进行仿真。一种这样做的方式涉及向fpga添加专用的影子寄存器。然而,这些专用的影子寄存器可能增加功率成本并占用集成电路上的大量面积。

附图说明

4.在阅读以下详细描述并且参考附图之后,可以更好地理解本公开的各种方面,在附图中:

5.图1是根据本公开的实施例的可以使用dsp块实现算术运算的系统的框图;

6.图2是根据本公开的实施例的图1的集成电路设备的框图;

7.图3是根据本公开的实施例的图1的集成电路设备的自适应逻辑元件的框图;

8.图4是根据本公开的实施例的图3的自适应逻辑元件在仿真读回期间执行用户数据采样操作的框图;

9.图5是根据本公开的实施例的图3的自适应逻辑元件在仿真读回期间执行移位操作的框图;以及

10.图6是根据本公开的实施例的图3的自适应逻辑元件在仿真写回期间执行移位操作的框图。

11.图7是根据本公开的实施例的图3的自适应逻辑元件在仿真写回期间执行写入操作的框图。

12.图8是根据本公开的实施例的用于在fpga设备上进行asic仿真的系统的框图。

13.图9是根据本公开的实施例的图8的系统的时序图。

14.图10是根据本公开的实施例的数据处理系统。

具体实施方式

15.下面将描述一个或多个具体实施例。为了提供对这些实施例的简明描述,在说明书中并未描述实际实现方式的所有特征。应该认识到的是,在任何此类实际实现方式的开

发中,就像在任何工程或设计项目中一样,必须做出许多特定于实现方式的决策来实现开发者的特定目标,例如,遵守系统相关和业务相关的约束,这些约束可能从一个实现方式到另一实现方式而变化。此外,应当认识到的是,这样的开发工作可能是复杂且耗时的,但是对于受益于本公开的普通技术人员而言,这不过是设计、制造和生产的常规任务。

16.当介绍本公开的各种实施例的元素时,冠词“一(a)”、“一(an)”和“该(the)”旨在表示存在元素中的一个或多个。术语“包括”和“具有”旨在是包含性的并且意味着除了所列元素之外可能还存在附加元素。另外地,应当理解,对本公开的“一些实施例”、“多个实施例”、“一个实施例”或“实施例”的引用并不旨在被解释为排除也并入引述的特征的附加实施例的存在。此外,短语a“基于”b旨在表示a至少部分地基于b。此外,术语“或”旨在包含性的(例如,逻辑or)而不是排除性的(例如,逻辑xor)。换言之,短语a“或”b旨在表示a,b,或a和b两者。

17.集成电路设备的可编程逻辑结构可以被编程以实现可编程电路设计,以执行宽范围的功能和操作。可编程逻辑结构可以包括可编程逻辑的可配置块(例如,有时称为逻辑阵列块(lab)或可配置逻辑块(clb)),这些可编程逻辑的可配置块具有查找表(lut),该lut可以被配置为作为不同逻辑元件基于被编程到块中的存储器单元的配置数据来操作。

18.如本文所使用的,“asic仿真”指代将专用集成电路(asic)电路设计的至少一部分实现到另一可编程逻辑器件(例如,fpga)中以便验证asic电路设计的功能。本系统和技术涉及在asic仿真期间用于可编程逻辑器件的非破坏性读回和写回的系统和方法的实施例。集成电路设备可以用于各种目的或应用,并且可编程逻辑器件可以用于执行这些功能。可编程逻辑器件的设计可能受到可用的硬件资源的量的限制。例如,fpga设备可以用于对具有非破坏性读回和写回能力的asic设备进行仿真。影子寄存器存储数据,并且可以将专用的影子寄存器添加到fpga,这增加了功率成本并占用大量面积。因此,不要求专用的影子寄存器的技术可以增加功率节省和fpga上可用的硬件资源。

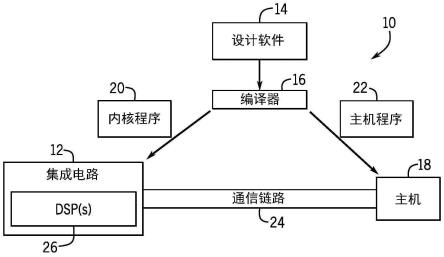

19.考虑到这一点,图1示出了系统10的框图,该系统10可以使用集成电路设备的组件(例如,可编程逻辑器件的组件(例如,可配置逻辑块、自适应逻辑模块、dsp块))来实现算术运算。设计者可能期望在集成电路设备12(例如,现场可编程门阵列(fpga)、专用集成电路(asic)、可编程逻辑阵列(pla)等)上实现诸如本公开的实现方式操作之类的功能。在一些情况下,设计者可以指定要实现的高级程序(例如,opencl程序),这可以使设计者能够更高效且更容易地提供编程指令来配置集成电路设备12的可编程逻辑单元的集合,而无需低级硬件描述语言(例如,verilog或vhdl)的特定知识。例如,因为opencl与其他高级编程语言(例如,c )非常相似,所以熟悉这种编程语言的可编程逻辑的设计者可以通过避免学习不熟悉的低级硬件描述语言实现集成电路设备12中的新功能,从而降低学习曲线。

20.设计者可以使用设计软件14(例如,intel公司的的版本)来实现他们的高级设计。设计软件14可以使用编译器16将高级程序转换为低级描述。编译器16可以向主机18和集成电路设备12提供代表高级程序的机器可读指令。主机18可以接收可以由内核程序20实现的主机程序22。为了实现主机程序22,主机18可以经由通信链路24将来自主机程序22的指令传送到集成电路设备12,该通信链路24可以是例如直接存储器访问(dma)通信或快速外围组件互连(pcie)通信。在一些实施例中,内核程序20和主机18可以实现集成电路设备12上的一个或多个dsp块26的配置。dsp块26可以包括电路以例如实现操

作,以执行针对ai或非ai数据处理的矩阵-矩阵乘法或矩阵-向量乘法。集成电路设备12可以包括许多(例如,数百或数千个)dsp块26。另外地,dsp块26可以通信地耦合到另一dsp块,使得从一个dsp块26输出的数据可以被提供给其他dsp块26。

21.虽然上面描述的技术指代高级程序的应用,但在一些实施例中,设计者可以使用设计软件14来生成和/或指定低级程序,例如,上面描述的低级硬件描述语言。此外,在一些实施例中,可以在没有单独的主机程序22的情况下实现系统10。此外,在一些实施例中,本文所描述的技术可以在电路中被实现为不可编程的电路设计。因此,本文所描述的实施例旨在是说明性而非限制性的。

22.现在转向集成电路设备12的更详细的讨论,图2示出了作为可编程逻辑器件(例如,现场可编程门阵列(fpga))的集成电路设备12的示例。此外,应当理解,集成电路设备12可以是任何其他合适类型的集成电路设备(例如,专用集成电路和/或专用标准产品)。如所示的,集成电路设备12可以具有输入/输出电路42,该输入/输出电路42用于驱动信号离开设备并用于经由输入/输出引脚44从其他设备接收信号。互连资源46(例如,全局和局部垂直和水平导线和总线)可以用于在集成电路设备12上路由信号。另外地,互连资源46可以包括固定互连(导线)和可编程互连(例如,在相应的固定互连之间的可编程连接)。可编程逻辑48可以包括组合和顺序逻辑电路。例如,可编程逻辑48可以包括查找表、寄存器和复用器。在各种实施例中,可编程逻辑48可以被配置为执行定制的逻辑功能。与互连资源相关联的可编程互连可以被认为是可编程逻辑48的一部分。

23.可编程逻辑器件(例如,集成电路设备12)可以在可编程逻辑48内包含可编程元件50。例如,如上面所讨论的,设计者(例如,客户)可以对可编程逻辑48进行编程(例如,配置)以执行一个或多个期望的功能。通过示例的方式,一些可编程逻辑器件可以通过使用掩模编程布置配置其可编程元件50来进行编程,这在半导体制造期间执行。在半导体制造操作已经完成之后,配置其他可编程逻辑器件,例如,通过使用电编程或激光编程来对其可编程元件50进行编程。通常,可编程元件50可以基于任何合适的可编程技术,例如,熔丝、反熔丝、电可编程只读存储器技术、随机存取存储器单元、掩模编程元件等。

24.许多可编程逻辑器件是电编程的。利用电编程布置,可编程元件50可以由一个或多个存储器单元形成。例如,在编程期间,使用引脚44和输入/输出电路42将配置数据加载到存储器单元中。在一个实施例中,存储器单元可以被实现为随机存取存储器(ram)单元。本文所描述的对基于ram技术的存储器单元的使用旨在仅作为一个示例。此外,因为这些ram单元在编程期间加载有配置数据,所以这些ram单元有时被称为配置ram单元(cram)。这些存储器单元可以各自提供对应的静态控制输出信号,该静态控制输出信号控制可编程逻辑48中相关联的逻辑组件的状态。例如,在一些实施例中,输出信号可以被施加到可编程逻辑48内的金属氧化物半导体(mos)晶体管的栅极。

25.图3是根据本公开的实施例的图1的集成电路设备12的自适应逻辑元件100的框图。自适应逻辑元件100可以包括任何合适数量的寄存器。如所示的,自适应逻辑元件100包括四个用户寄存器114、116、118和120。每个寄存器可以是存储单元并且可以存储单个数据位。另外地,每个寄存器可以接收可以改变寄存器的输出的时钟信号。在一些实施例中,时钟信号可以是时钟信号的低到高转换。寄存器114、116可以形成第一寄存器对,并且寄存器118、120可以形成第二寄存器对。每个寄存器对可以在asic仿真期间用作单个寄存器。在一

些实施例中,任何合适数量的寄存器(例如,三个寄存器、四个寄存器,等等)可以在asic仿真期间用作单个寄存器。寄存器114和寄存器118可以是快速寄存器,并且寄存器116、120可以是慢速寄存器。如本文所使用的,可以在asic仿真期间针对asic被测设备(device-under-test,dut)逻辑利用“快速寄存器”,并且“慢速寄存器”可以通过提供非破坏性寄存器读回来用作影子寄存器。在一些实施例中,快速寄存器可以支持比慢速寄存器的最大频率更高的最大频率。例如,快速寄存器可以以比慢寄存器的频率更高的频率操作。慢速寄存器可以使用可以占用较少管芯空间的电路来形成,或者与快速寄存器相比可以不那么昂贵。慢速寄存器是使用高vt(例如,高阈值电压)晶体管设计的以具有较少的功率泄漏,由此与快速寄存器相比降低功耗。因此,如下文将讨论的,使用寄存器对可以高效地实现非破坏性读回和写回,该寄存器对使用慢速寄存器(例如,116)和快速寄存器(例如,114)。然而,在期望时,寄存器对可以由两个或更多个快速寄存器或者两个或更多个慢速寄存器形成。实际上,在一些示例中,自适应逻辑元件100可以仅包括快速寄存器或仅包括慢速寄存器。另外或可替代地,慢速寄存器可以以等于或小于快速寄存器的频率的频率操作。

26.自适应逻辑元件100可以包括lab时钟信号122和测试设计(design for test,dft)时钟信号124。快速寄存器114、118可以接收lab时钟信号122作为时钟源。每个慢速寄存器(例如,慢速寄存器116、120)可以连接到到对应的复用器102。在某些实施例中,复用器102可以接收lab时钟信号122和dft时钟信号124,并且可以选择时钟信号中的一个以提供作为用于慢速寄存器116、120的时钟源。自适应逻辑元件100的每个寄存器可以连接到复用器(例如,复用器106连接到寄存器114)以提供测试数据作为输入。

27.图4是根据本公开的实施例的图3的自适应逻辑元件100在仿真读回期间执行用户数据采样操作的框图。在数据采样操作期间,从快速寄存器114、118输出的数据可以存储在对应的慢速寄存器116、120中。快速寄存器114、118可以接收lab时钟信号122作为时钟源。快速寄存器114、118可以连接到复用器104,该复用器104接收dft卸载信号136,并且选择用户数据输入信号156、160分别作为来自复用器104的输出。复用器102可以接收仿真信号126,并且仿真信号126可以指示复用器102选择dft时钟信号124作为由慢速寄存器116、120接收到的输出134。来自快速寄存器114的测试数据输出140可以由连接到慢速寄存器116的复用器108接收。复用器108可以接收dft加载信号130,并且可以选择来自快速寄存器114的测试数据输出140作为对慢速寄存器116的输入。复用器112可以接收dft加载信号130,并且可以选择来自快速寄存器118的测试数据输出144作为对慢速寄存器120的输入。因此,慢速寄存器116可以存储测试数据输出140,并且慢速寄存器120可以存储测试数据输出144。在数据采样操作期间供应给自适应逻辑元件100的寄存器的控制和时钟信号可以基于逻辑表,例如,表1。虽然表1描述了针对dft加载信号130、dft卸载信号136和仿真信号126的特定位值,但可以使用任何合适的位值、信号状态和/或极性。

[0028][0029]

图5是根据本公开的实施例的图3的自适应逻辑元件100在仿真读回期间执行移位操作的框图。复用器102可以选择dft时钟信号124作为输出134,并且慢速寄存器116、120可以接收dft时钟信号124。快速寄存器114、118可以包括复用器,该复用器接收dft卸载信号136,并且选择用户数据输入信号156、160分别作为来自复用器的输出。复用器108可以接收dft加载信号130,并且选择来自另一慢速寄存器的测试数据输出信号128作为慢速寄存器116的数据输入信号。因此,自适应逻辑元件100可以将数据从另一慢速寄存器移位到慢速寄存器116。复用器112可以选择来自慢速寄存器116的测试数据输出信号142,并且慢速寄存器120可以接收测试数据输出信号142作为测试数据输入信号。先前存储在慢速寄存器120中的数据可以作为输出信号152移出。因此,自适应逻辑元件100可以将数据从慢速寄存器116移位到慢速寄存器120,并且可以将来自慢速寄存器120的数据作为输出信号152移出。供应给自适应逻辑元件100的寄存器的控制和时钟信号可以基于逻辑表,例如,表2。虽然表2描述了针对dft加载信号130、dft卸载信号136和仿真信号126的特定位值,但可以使用任何合适的位值、信号状态和/或极性。

[0030]

[0031]

图6是根据本公开的实施例的图3的自适应逻辑元件在仿真写回期间执行移位操作的框图。复用器102可以选择dft时钟信号124作为输出134,并且慢速寄存器116、120可以接收dft时钟信号124。快速寄存器114、118可以包括复用器,该复用器接收dft卸载信号136,并且选择用户数据输入信号156、160分别作为来自复用器的输出。复用器108可以接收dft加载信号130,并且选择来自另一慢速寄存器的测试输出数据信号128作为慢速寄存器116的数据输入信号。因此,自适应逻辑元件100可以将数据从另一慢速寄存器移位到慢速寄存器116。复用器112可以选择来自慢速寄存器116的测试数据输出信号142,并且慢速寄存器120可以接收测试数据输出信号142作为测试数据输入信号。先前存储在慢速寄存器120中的数据可以作为输出信号152移出。因此,自适应逻辑元件100可以将数据从慢速寄存器116移位到慢速寄存器120,并且可以将来自慢速寄存器120的数据作为输出信号152移出。作为图5和图6中的移位操作的结果,先前存储在慢速寄存器116、118中的数据可以被移出。供应给自适应逻辑元件100的寄存器的控制和时钟信号可以基于逻辑表,例如,表3。虽然表3描述了针对dft加载信号130、dft卸载信号136和仿真信号126的特定位值,但可以使用任何合适的位值、信号状态和/或极性。

[0032][0033]

图7是根据本公开的实施例的图3的自适应逻辑元件在仿真写回期间执行写入操作的框图。快速寄存器114、118可以接收lab时钟信号122作为时钟源。复用器106可以接收dft加载信号130,并且复用器106可以选择来自慢速寄存器116的测试数据输出信号142作为快速寄存器114的测试数据输入。因此,存储在慢速寄存器116中的数据可以作为测试数据输出信号142输出,并且自适应逻辑元件100将数据写入快速寄存器114。复用器110可以接收dft加载信号130,并且复用器110可以选择来自慢速寄存器120的测试数据输出信号152作为快速寄存器118的测试数据输入。因此,存储在慢速寄存器120中的数据可以作为测试数据输出信号152输出,并且自适应逻辑元件100将数据写入快速寄存器118。在写入操作期间供应给自适应逻辑元件100的寄存器的控制和时钟信号可以基于逻辑表,例如,表4。虽然表4描述了针对dft加载信号130、dft卸载信号136和仿真信号126的特定位值,但可以使用任何合适的位值、信号状态和/或极性。

[0034][0035][0036]

图8是根据本公开的实施例的用于在fpga设备上进行asic仿真的系统200的框图。系统200可以包括读回/写回外围设备204,该读回/写回外围设备204包括寄存器访问接口206、控制寄存器208和任何数量的附加寄存器210。读回/写回外围设备204可以通信地耦合到读回/写回控制器202。例如,读回/写回控制器202可以经由寄存器访问接口206与控制寄存器208通信。系统200还可以包括脉冲生成器212,并且脉冲生成器212可以生成单波脉冲。脉冲生成器212可以经由控制寄存器208通信地耦合到读回/写回外围设备204。在一些实施例中,系统200可以包括在核心结构222中的流水线寄存器218、220。流水线寄存器218、220可以接收来自脉冲生成器212的单波脉冲,并且可以确保采样请求脉冲242和由dut时钟216生成的dut时钟信号250具有相同的频率。在一些实施例中,由dut时钟216生成的dut时钟信号250可以具有上至六百mhz的频率(例如,上至一百mhz、上至二百mhz、上至三百mhz等等)。dut时钟216可以经由时钟分配网络214通信地耦合到脉冲生成器212和核心结构222。逻辑阵列块核心结构268可以包括复用器244、时钟门246、复用器248、第一用户寄存器254、第二用户寄存器256、第一影子寄存器260和第二影子寄存器262。复用器244可以向第一用户寄存器254和第二用户寄存器256提供dut时钟信号。本地仿真管理器226可以包括观察寄存器228和第一控制寄存器230、第二控制寄存器232和第三控制寄存器234。第一控制寄存器230可以生成时钟覆盖信号238,并且第三控制寄存器234可以生成移位/加载信号240。配置时钟224可以生成仿真时钟信号236。

[0037]

读回/写回控制器202可以经由寄存器访问接口206与控制寄存器208通信。读回/写回控制器202可以将控制寄存器208中的采样请求位设置为1。脉冲生成器212可以检测采样请求位的上升沿,并且可以生成采样请求脉冲242。采样请求脉冲242可以与dut时钟216同步。另外地,采样请求脉冲242可以在一个周期内为高。时钟门246可以接收采样请求脉冲242,并且可以生成单个dut时钟216脉冲,复用器248可以接收该单个dut时钟216脉冲作为输入。因此,影子寄存器260、262可以接收单个dut时钟216脉冲作为来自复用器248的输出252,并且影子寄存器260、262可以分别对来自用户寄存器254、256的数据进行采样,并且影子寄存器260、262可以以与用户寄存器254、256相同的频率操作。在某些实施例中,影子寄

存器260、262可以以等于或小于用户寄存器254、256的频率的频率操作。

[0038]

本地仿真管理器226可以例如在观察寄存器228处接收采样请求脉冲242。作为响应,本地仿真管理器226可以经由控制寄存器230生成时钟覆盖信号238。复用器248可以接收时钟覆盖信号238,并且可以选择仿真时钟236作为输出252。另外地,本地仿真管理器226可以经由控制寄存器234生成移位/加载信号240,并且影子寄存器260、262可以接收移位/加载信号240。因此,影子寄存器260、262可以被配置为移位寄存器模式,并且存储在影子寄存器262中的数据可以作为输出264被移出。存储在影子寄存器260中的数据可以在影子寄存器时钟252的第一脉冲上被移位到影子寄存器262,并且可以在影子寄存器时钟252的后续脉冲上移出影子寄存器262。

[0039]

图9是根据本公开的实施例的图8的系统的时序图300。时序图300包括波形302、304。波形302描绘了用户寄存器(例如,用户寄存器254)的状态,并且波形304描绘了影子寄存器(例如,影子寄存器260)的状态。如时序图300中示出的,影子寄存器可以对用户寄存器的状态进行采样。例如,采样请求脉冲242可以由时钟门246接收,并且时钟门246可以生成单个脉冲,复用器248可以接收该单个脉冲并将该单个脉冲作为输出252提供。影子寄存器可以在输出252的单个脉冲的上升沿处对用户寄存器的数据(状态a0)进行采样。本地仿真管理器226可以生成时钟覆盖信号238。然后,影子寄存器可以接收移位/加载信号240,并且移位/加载信号240可以将影子寄存器配置为移位寄存器模式。因此,影子寄存器可以将存储在影子寄存器中的数据移出。

[0040]

集成电路设备12可以是数据处理系统或被包括在数据处理系统中的组件。例如,集成电路设备12可以是图10中示出的数据处理系统60的组件。数据处理系统60可以包括主机处理器62(例如,中央处理单元(cpu))、存储器和/或存储电路64以及网络接口66。数据处理系统60可以包括更多或更少的组件(例如,电子显示器、用户接口结构、专用集成电路(asic))。主机处理器62可以包括任何合适的处理器,例如,处理器或精简指令处理器(例如,精简指令集计算机(risc)、高级risc机器(arm)处理器),其可以管理针对数据处理系统60的数据处理请求(例如,以执行调试、数据分析、加密、解密、机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航等)。存储器和/或存储电路64可以包括随机存取存储器(ram)、只读存储器(rom)、一个或多个硬盘驱动器、闪速存储器等。存储器和/或存储电路64可以保存要由数据处理系统60处理的数据。在一些情况下,存储器和/或存储电路64还可以存储用于对集成电路设备12进行编程的配置程序(位流)。网络接口66可以允许数据处理系统60与其他电子设备通信。数据处理系统60可以包括若干不同的封装,或者可以被包含在单个封装衬底上的单个封装内。

[0041]

在一个示例中,数据处理系统60可以是处理各种不同请求的数据中心的一部分。例如,数据处理系统60可以经由网络接口66接收数据处理请求以执行asic仿真、调试、错误检测、数据分析、加密、解密、机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航、数字信号处理或某种其他专门任务。

[0042]

因此,本文所描述的技术使得能够在可编程逻辑器件(例如,fpga)上进行asic仿真。例如,要在fpga(例如,集成电路12)上实现的针对电路的电路设计和信号数据收集使得能够进行asic仿真,并增强了集成电路设备(例如,可编程逻辑器件(例如,fpga))的能力以

供asic仿真应用使用,同时使该集成电路设备仍适用于数字信号处理应用。

[0043]

虽然本公开中阐述的实施例可能易于受到各种修改和替代形式的影响,但已经通过示例的方式在附图中示出并且已经在本文中详细描述了具体实施例。然而,应当理解,本公开并不旨在限于所公开的特定形式。本公开将涵盖落入由以下所附权利要求书限定的本公开的精神和范围内的所有修改、等效物和替代方案。

[0044]

本文呈现和要求保护的技术被引用并应用于实体对象和具有实际性质的具体示例,它们明确地改进了当前技术领域,并因此不是抽象的、无形的或纯理论的。此外,如果附加到本说明书末尾的任何权利要求包含被指定为“用于[执行][功能]

…

的单元”或“用于[执行][功能]

…

的步骤”一个或多个元素,则旨在根据35u.s.c.112(f)来解释这种元素。然而,对于包含以任何其他方式指定的元素的任何权利要求,旨在不根据35u.s.c.112(f)解释这种元素。

[0045]

本公开的示例实施例

[0046]

以下编号的条款定义了本公开的某些示例实施例。

[0047]

示例实施例1、一种方法,包括:

[0048]

在自适应逻辑元件上提供来自第一时钟的具有第一频率的第一时钟信号和来自第二时钟的具有第二频率的第二时钟信号,其中,提供第一时钟信号作为用于第一寄存器的第一时钟源;

[0049]

在复用器处选择第二时钟信号作为用于第二寄存器的第二时钟源;

[0050]

基于选择第二时钟信号作为第二时钟源来进行以下操作:

[0051]

对来自第一寄存器的第一数据进行采样;以及

[0052]

将第一经采样的数据存储在第二寄存器上,其中,第二频率等于或低于第一频率。

[0053]

示例实施例2、示例实施例1的方法,包括:在第二复用器处选择来自第一寄存器的第一经采样的数据作为针对第二寄存器的数据输入。

[0054]

示例实施例3、示例实施例1的方法,包括:

[0055]

提供第一时钟信号作为用于第三寄存器的第三时钟源;以及

[0056]

在第三复用器处选择第二时钟信号作为用于第四寄存器的第四时钟源。

[0057]

示例实施例4、示例实施例3的方法,包括:

[0058]

基于选择第二时钟信号作为第四时钟源来进行以下操作:

[0059]

对来自第三寄存器的第二数据进行采样;以及

[0060]

将第二经采样的数据存储在第四寄存器上。

[0061]

示例实施例5、示例实施例4的方法,其中,第一频率上至六百mhz。

[0062]

示例实施例6、示例实施例1的方法,其中,第二寄存器是影子寄存器。

[0063]

示例实施例7、示例实施例4的方法,包括:将所存储的第二经采样的数据移出第四寄存器。

[0064]

示例实施例8、示例实施例4的方法,包括:将所存储的第一经采样的数据从第二寄存器移位到第四寄存器。

[0065]

示例实施例9、示例实施例8的方法,包括:将第一经采样的数据移出第四寄存器。

[0066]

示例实施例10、一种自适应逻辑元件,包括:

[0067]

第一寄存器对,该第一寄存器对包括:

[0068]

第一寄存器,该第一寄存器能够被配置为以第一频率操作;以及

[0069]

第二寄存器,该第二寄存器能够被配置为:

[0070]

以第二频率操作,其中,第二频率等于或低于第一频率;以及

[0071]

存储来自第一寄存器的数据;

[0072]

第一时钟,该第一时钟能够被配置为向第一寄存器提供第一时钟信号;

[0073]

第二时钟,该第二时钟能够被配置为提供第二时钟信号;以及

[0074]

复用器,该复用器能够被配置为选择第一时钟信号或第二时钟信号作为用于第二寄存器的时钟源。

[0075]

示例实施例11、示例实施例10的自适应逻辑元件,包括:

[0076]

第二寄存器对,该第二寄存器对包括:

[0077]

第三寄存器,该第三寄存器能够被配置为以第一频率操作;以及

[0078]

第四寄存器,该第四寄存器能够被配置为以第二频率操作,其中,

[0079]

第四寄存器能够被配置为存储来自第三寄存器的数据。

[0080]

示例实施例12、示例实施例11的自适应逻辑元件,包括:第二复用器,该第二复用器能够被配置为选择第一时钟信号或第二时钟信号作为用于第四寄存器的第二时钟源。

[0081]

示例实施例13、示例实施例11的自适应逻辑元件,其中,第一时钟能够被配置为向第三寄存器提供第一时钟信号。

[0082]

示例实施例14、示例实施例12的自适应逻辑元件,其中,第二复用器选择第二时钟信号以将来自第三寄存器的数据存储在第四寄存器上。

[0083]

示例实施例15、示例实施例10的自适应逻辑元件,其中,复用器选择第二时钟信号以将来自第一寄存器的数据存储在第二寄存器上。

[0084]

示例实施例16、示例实施例10的自适应逻辑元件,包括:第三复用器,该第三复用器能够被配置为选择来自第一寄存器的数据作为用于第二寄存器的输入数据。

[0085]

示例实施例17、一种系统,包括:

[0086]

第一寄存器对,该第一寄存器对包括:

[0087]

第一寄存器,该第一寄存器能够被配置为以第一频率操作;以及

[0088]

第二寄存器,该第二寄存器能够被配置为:

[0089]

以第二频率操作,其中,第二频率等于或低于第一频率;以及

[0090]

存储来自第一寄存器的数据;

[0091]

第二寄存器对,该第二寄存器对包括:

[0092]

第三寄存器,该第三寄存器能够被配置为以第一频率操作;以及

[0093]

第四寄存器,该第四寄存器能够被配置为以第二频率操作,其中,第四寄存器能够被配置为存储来自第三寄存器的数据,并且其中,第四寄存器能够被配置为存储从第二寄存器移出的数据。

[0094]

示例实施例18、示例实施例17的系统,包括:第一复用器,该第一复用器能够被配置为选择第一频率的第一时钟信号或第二频率的第二时钟信号作为用于第二寄存器的时钟源。

[0095]

示例实施例19、示例实施例18的系统,包括:第二复用器,该第二复用器能够被配置为选择第一时钟信号或第二时钟信号作为用于第四寄存器的第二时钟源。

[0096]

示例实施例20、示例实施例18的系统,其中,第二复用器选择第二时钟信号以将所存储的数据从第二寄存器移位到第四寄存器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。