1.本发明涉及一种集成电路并发测试装置及方法,集成电路自动测试领域。

背景技术:

::2.随着集成电路多芯片封装技术的成熟,及单芯片集成了更多的数字模拟混合信号等,在集成电路的自动测试设备(autotestequipment,简称ate)中,如何更高效的在多测试站(site)间同步并行或异步并发测试中,完成数字与模拟信号的混合测试等方面提出了更多的挑战。例如:在一颗soc芯片测试中,需要通过数字通道往spi接口不断发送trimming数据给芯片,然后通过模拟源测试ref电压输出,寻找最佳trimming值。因为soc芯片规模越来越大,集成的参考电压等模拟信号也越来越多,导致这类扫描测试所花费的时间占总体测试时间的比重不断加大。3.传统测试解决方法,是将数字信号测试由测试处理器完成,模拟信号测试由pc完成。数字信号测试与模拟信号测试在两种处理器间切换。例如:由测试处理器完成一个spi数据的发送,改变芯片ref电压输出,然后由pc完成ref信号的电压值测量,依此循环。此类方法的优点是成本较低,编程灵活,但是存在几个问题:1.测试在两种处理器间切换,导致花费较多的时间在切换的过程中,测试效率较低。4.2.对于多测试站的测试,由于pc只能通过pcie总线串行读取测试数据,从而只能串行的对各个测试站的模拟信号完成测试,导致测试效率较低。5.3.对于各个测试站无法同步的情况,例如:芯片在通过数字信号测试后,经过一定的时间,输出模拟脉冲信号。但各个测试站的模拟脉冲信号上升沿产生时间不一致,导致各个测试站需要能并发自主完成模拟信号的匹配测试,同时模拟信号的测试需要能与数字信号测试精确同步。此类情形对于传统测试方法,因为模拟信号的测试需要切换到pc完成,而pc只能串行测试,同时也无法与被测信号精确同步,导致各个测试站无法并发完成测试。技术实现要素:6.发明目的:为了克服现有技术中存在的不足,本发明提供一种集成电路并发测试装置及方法,本发明关键是要能实现将模拟信号测试与数字信号测试都统一到测试处理器中。由于数字信号由数字信号发生板卡产生,而模拟信号由独立的模拟信号发生板卡产生,例如:模拟电源板卡,任意信号发生器板卡等。由于模拟与数字板卡都是通过系统背板总线,由pc直接控制。而若要将模拟信号测试统一到测试处理器中,需要在测试处理器与模拟测试通道间建立新的控制总线。并实现模拟测试通道在测试处理器与模拟测试通道间的编译与解释执行。7.技术方案:为实现上述目的,本发明采用的技术方案为:一种集成电路并发测试装置,包括测试处理器tp、parameterpattern编译器ppc、通道参数测试控制器ptc、仪表控制总线icb,其中:所述测试处理器tp包括时序发生器tg、测试图形发生器、信号处理单元控制指令发生器、测试图形存储器、存储控制器、仪表控制总线命令发生器icmg,所述存储控制器分别与时序发生器tg、测试图形发生器、信号处理单元控制指令发生器、仪表控制总线命令发生器icmg连接,所述测试图形发生器分别与时序发生器tg、信号处理单元控制指令发生器连接。8.所述测试处理器tp处理的测试图形发生器文件包括两个以上的仪表控制指令组合向量,仪表控制指令组合向量由测试图形发生器控制指令、时序设置、数字通道列表、模拟器件管脚列表组成,所述模拟器件管脚列表由仪表控制指令组成。9.parameterpattern编译器ppc根据仪表控制指令与仪表控制消息转换表将仪表控制指令转换成仪表控制消息icm。10.所述parameterpattern编译器ppc通过仪表控制总线icb与通道参数测试控制器ptc连接。11.优选的:每个唯一的仪表控制指令组合向量称为一个仪表控制指令组。12.优选的:两个以上的仪表控制指令组组成一个仪表控制指令表。13.优选的:每个唯一的仪表控制指令组合向量被赋予一个仪表控制指令值。14.一种集成电路并发测试方法,包括以下步骤:步骤1,测试处理器tp发出仪表控制消息icm,经过仪表控制总线icb的传输,进入每个测试通道的仪表控制总线控制器icbrc。15.步骤2,仪表控制总线控制器icbrc将仪表控制消息值icm转化为通道的仪表控制码icc。16.步骤3,仪表控制码icc再经过通道参数测试控制器ptc的解析,完成对模拟通道的最终控制。17.优选的:同一个仪表控制消息icm经过各个不同通道的仪表控制总线控制器icbrc,会映射为不同的仪表控制码icc,以对应各自通道的仪表控制指令ico。18.优选的:仪表控制总线控制器icbrc选择接收指定测试处理器的仪表控制消息icm,从而允许多个测试处理器并发控制各自指定的一组模拟测试通道。19.本发明相比现有技术,具有以下有益效果:本发明通过将数字信号测试与模拟信号测试都统一到测试处理器控制,从而避免了传统测试的各项问题,可以带来以下的优势:1.由于ate可以有多个测试处理器(可以为每个测试站分配一个测试处理器),而每个测试处理器可以异步并发的工作,从而可以很好的完成数字信号与模拟信号的异步并发混合测试。20.2.由于数字信号测试与模拟信号测试都由测试处理器直接完成,所以数字信号与模拟信号测试的时序可以精确同步,从而可以准确完成复杂的数字模拟信号混合测试要求。21.3.通过将数字信号测试的编程与模拟信号的编程统一在一个图形(pattern)文件中,从而降低了测试程序编写的难度,提高了混合信号测试程序开发调试的效率。附图说明22.图1为测试处理器内部结构原理图。23.图2为传统测试图形文件(pattern)示意图。24.图3为本发明实施例测试图形文件(pattern)示意图。25.图4为ico与icm转换表。26.图5为多通道并发测试装置控制示意图,具体为icm如何从测试处理器发送到模拟测试通道的过程。27.图6为多测试站数字模拟混合并发测试示意图。具体实施方式28.下面结合附图和具体实施例,进一步阐明本发明,应理解这些实例仅用于说明本发明而不用于限制本发明的范围,在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落于本技术所附权利要求所限定的范围。29.一种集成电路并发测试装置,如图1所示,包括测试处理器tp4(testprocessor,简称tp)、parameterpattern编译器ppc14(parameterpatterncompiler,简称ppc)、通道参数测试控制器ptc(parametertestcontroller,简称ptc)、仪表控制总线icb(instrumentscontrolbus,简称icb),其中:所述测试处理器4包括时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3、测试图形存储器、存储控制器、仪表控制总线命令发生器icmg5,所述存储控制器分别与时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3、仪表控制总线命令发生器5连接,所述测试图形发生器2分别与时序发生器tg1、信号处理单元控制指令发生器3连接。30.时序发生器tg1(timinggenerator,简称tg),用于按照图形文件指定的时序要求,产生每个周期所需的精确时序信号(包括周期,时沿等)。31.测试图形发生器2(patterngenerator),用于按照图形文件(patternfile)的指令要求,产生图形测试所需的控制时序(包括:跳转、循环等)。32.信号处理单元控制指令发生器3(signalprocessorunitcommandgenerator,spucg),用于根据图形文件控制数据要求,产生用于同步控制数字测试通道子系统的指令信号。33.测试处理器tp4(testprocessor,简称tp)。时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3通过存储控制器(memorycontrol)访问测试图形存储器(patternmemory),获取指令和数据,时序发生器tg1负责产生当前周期相应的周期和时钟边沿等信息,并提供给其他模块。测试图形发生器2负责执行测试图形文件(pattern)中的指令要求,实现跳转、循环等,同时控制存储控制器(memorycontrol)对测试图形存储器(patternmemory)的地址访问。信号处理单元控制指令发生器3在测试图形发生器2的控制下,将测试子系统控制指令发送给相应的子系统,实现对子系统的同步控制。另外,从架构图可以看出测试处理器tp4是一个典型的冯诺伊曼结构的处理器,但指令集采用ate专用指令集,专用于处理信号,而非数据。34.所述仪表控制总线命令发生器icmg5(icmgenerator,icmg)用于将仪表控制指令ico(instrumentcontrolopcodes,简称ico,具体参考图3说明)转化为仪表控制消息icm(instrumentscontrolmessage,简称icm)。通过仪表控制总线icb传递给各个通道参数测试控制器ptc,从而测试处理器完成了对各个非数字通道的测试控制。35.如图2所示,为传统的测试处理器处理的pattern文件,传统的测试处理器处理的pattern文件由测试图形发生器控制指令11、时序设置12、数字通道列表13构成,提供了图形测试发生器所需的所有信息。36.测试图形发生器控制指令11(patterngeneratorcommand),产生图形测试所需的控制时序,包括:跳转(jump)、循环(repeat、loop)、停止(halt)等。37.时序设置12(timingset),定义了图形发生器产生每个周期所需的精确时序信信息(包括周期,时沿等)。38.数字通道列表13(digitalchannellist),描述了每个周期不同时序条件下各个数字通道的工作状态。根据需求这些通道可以被设定为不同模式,如:i/o既可以作为驱动管脚也可以作为接受管脚,其中驱动管脚的有效数据为0和1,接受管脚的有效数据为:l、h和x。39.从图3中可以看出,所有控制都是针对数字测试通道的,可以精确的描述每个数字测试通道的测试时序.本发明实施例在原有pattern的基础上新增了模拟通道管脚的控制指令内容,如图3所示,本实施例所述测试处理器tp4处理的测试图形发生器文件包括两个以上的仪表控制指令组合向量,仪表控制指令组合向量由测试图形发生器控制指令11、时序设置12、数字通道列表13、模拟器件管脚列表15组成,所述模拟器件管脚列表15由仪表控制指令组成。提供了测试处理器所需的所有信息。通过这些指令能在纯数字测试通道控制的基础上新增模拟测试通道的控制。从而可以同时将数字信号测试与模拟信号统一在一个pattern文件中进行描述。40.如图3所示,10为pattern文件的每一行表示一个向量(vector),此处列出向量索引只为后续介绍方便,在实际pattern不包含该向量的索引。测试图形发生器控制指令11、时序设置12、数字通道列表13与传统测试图形文件内容相同。41.模拟器件管脚列表15可以包含多个模拟器件通道控制(这里包含了3个),其内容是仪表控制指令(instrumentcontrolopcode,简称ico),通过这些指令可以定义模拟器件的状态,例如设置电压值(set_voltage1.8v)、将模拟通道输出设为高阻态(gate_off)、采集dut结果(strobe)等。42.因此本实施例所述测试处理器tp4处理的测试图形发生器文件pattern不仅可以控制数字测试通道也可以用于控制模拟通道,可以精确的描述每个数字、模拟测试通道的测试时序。43.接下来要解决的问题是,一个测试处理器如何将一组ico同时发送给多个不同的非数字测试通道的cptc,完成同步控制,并让各个通道实现不同的操作。44.首先需要将控制指令组转换为icm。如图4所示,说明了编译器如何将仪表控制指令ico如何转化为icm。45.新的pattern文件每个vector可以包含多个模拟测试通道指令列表,每行vector中的多个仪表控制指令(instrumentcontrolopcodes)代表一个仪表控制指令组合,每个唯一的控制指令组合称为一个仪表控制指令组(instrumentcontrolopcodesgroup,简称icog)(见图3),多个唯一的icog组成了一个icmtable,每一行icog被赋予一个icm值。46.如图4所示,图3中gate_off命令会被编译成ico1,set_voltage1.8v被编译成ico2、strobe被编译成ico3、gateon被编译成ico4等等。图3中有6个唯一的icog(vector5和vector7相同,所以只能算一种),编译后会生成6种不同的icm。47.parameterpattern编译器ppc14根据仪表控制指令与仪表控制消息转换表将仪表控制指令转换成仪表控制消息icm。所述parameterpattern编译器ppc14通过仪表控制总线icb与通道参数测试控制器ptc连接。48.parameterpattern编译器ppc14对整个pattern测试程序进行编译成设备能执行的命令。pattern测试程序根据测试需求可能包含仪器仪表相关的控制指令(还有许多其他控制命令)进行编译,这些被编译后的指令将会交给仪表控制总线命令发生器icmg5对命令进行解析,然后生成仪器仪表模块能识别的命令。这些命令会发送到仪表控制总线icb上,哪写仪器能识别这些命令通过仪表控制总线控制器icbrc进行管理。49.一种集成电路并发测试方法,如图5所示,包括以下步骤:步骤1,测试处理器tp4发出仪表控制消息icm,经过仪表控制总线icb的传输,进入每个测试通道的仪表控制总线控制器icbrc(icbreceivercontroller,简称icbrc)。50.步骤2,仪表控制总线控制器icbrc将仪表控制消息值icm转化为通道的仪表控制码icc(instrumentscontrolcode,简称icc)。51.步骤3,仪表控制码icc再经过通道参数测试控制器ptc的解析,完成对模拟通道的最终控制。52.其中,同一个仪表控制消息icm经过各个不同通道的仪表控制总线控制器icbrc,会映射为不同的仪表控制码icc,以对应各自通道的仪表控制指令ico。从而通过一个测试处理器,即可同步控制多个不同模拟测试通道,同时完成不同的测试。53.同时,仪表控制总线控制器icbrc可以选择接收指定测试处理器的仪表控制消息icm,从而允许多个测试处理器并发控制各自指定的一组模拟测试通道。如果为每个测试站分配一个测试处理器,即可实现多测试站的并发多时钟域测试。54.如图6所示,为出了两个测试站的情况,本发明也适用更多测试站的情况。从图6可以看出,每个测试站(deviceundertest,简称dut)都分配了一组数字测试通道,与一组模拟测试通道。分别都由一个独立测试处理器控制。当两个测试处理器工作在不同的时钟域时,两个测试站即可工作在并发测试状态。从图6中可以看出,数字测试通道与模拟测试通道的控制在测试过程中不需要pc的参与。多时钟域测试也适用于单测试站内部的情况。55.本发明可以实现数字测试与模拟测试统一在同一个pattern文件,简化测试程序开发。可以同步并发的控制数字测试通道与模拟测试通道,不需要在测试处理器与pc处理器直接切换,提高测试效率,降低测试成本。可以实现模拟测试通道与数字测试通道的精确同步,从而实现更复杂的集成电路参数测试,提高测试覆盖率。56.以上所述仅是本发明的优选实施方式,应当指出:对于本

技术领域:

:的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。当前第1页12当前第1页12

背景技术:

::2.随着集成电路多芯片封装技术的成熟,及单芯片集成了更多的数字模拟混合信号等,在集成电路的自动测试设备(autotestequipment,简称ate)中,如何更高效的在多测试站(site)间同步并行或异步并发测试中,完成数字与模拟信号的混合测试等方面提出了更多的挑战。例如:在一颗soc芯片测试中,需要通过数字通道往spi接口不断发送trimming数据给芯片,然后通过模拟源测试ref电压输出,寻找最佳trimming值。因为soc芯片规模越来越大,集成的参考电压等模拟信号也越来越多,导致这类扫描测试所花费的时间占总体测试时间的比重不断加大。3.传统测试解决方法,是将数字信号测试由测试处理器完成,模拟信号测试由pc完成。数字信号测试与模拟信号测试在两种处理器间切换。例如:由测试处理器完成一个spi数据的发送,改变芯片ref电压输出,然后由pc完成ref信号的电压值测量,依此循环。此类方法的优点是成本较低,编程灵活,但是存在几个问题:1.测试在两种处理器间切换,导致花费较多的时间在切换的过程中,测试效率较低。4.2.对于多测试站的测试,由于pc只能通过pcie总线串行读取测试数据,从而只能串行的对各个测试站的模拟信号完成测试,导致测试效率较低。5.3.对于各个测试站无法同步的情况,例如:芯片在通过数字信号测试后,经过一定的时间,输出模拟脉冲信号。但各个测试站的模拟脉冲信号上升沿产生时间不一致,导致各个测试站需要能并发自主完成模拟信号的匹配测试,同时模拟信号的测试需要能与数字信号测试精确同步。此类情形对于传统测试方法,因为模拟信号的测试需要切换到pc完成,而pc只能串行测试,同时也无法与被测信号精确同步,导致各个测试站无法并发完成测试。技术实现要素:6.发明目的:为了克服现有技术中存在的不足,本发明提供一种集成电路并发测试装置及方法,本发明关键是要能实现将模拟信号测试与数字信号测试都统一到测试处理器中。由于数字信号由数字信号发生板卡产生,而模拟信号由独立的模拟信号发生板卡产生,例如:模拟电源板卡,任意信号发生器板卡等。由于模拟与数字板卡都是通过系统背板总线,由pc直接控制。而若要将模拟信号测试统一到测试处理器中,需要在测试处理器与模拟测试通道间建立新的控制总线。并实现模拟测试通道在测试处理器与模拟测试通道间的编译与解释执行。7.技术方案:为实现上述目的,本发明采用的技术方案为:一种集成电路并发测试装置,包括测试处理器tp、parameterpattern编译器ppc、通道参数测试控制器ptc、仪表控制总线icb,其中:所述测试处理器tp包括时序发生器tg、测试图形发生器、信号处理单元控制指令发生器、测试图形存储器、存储控制器、仪表控制总线命令发生器icmg,所述存储控制器分别与时序发生器tg、测试图形发生器、信号处理单元控制指令发生器、仪表控制总线命令发生器icmg连接,所述测试图形发生器分别与时序发生器tg、信号处理单元控制指令发生器连接。8.所述测试处理器tp处理的测试图形发生器文件包括两个以上的仪表控制指令组合向量,仪表控制指令组合向量由测试图形发生器控制指令、时序设置、数字通道列表、模拟器件管脚列表组成,所述模拟器件管脚列表由仪表控制指令组成。9.parameterpattern编译器ppc根据仪表控制指令与仪表控制消息转换表将仪表控制指令转换成仪表控制消息icm。10.所述parameterpattern编译器ppc通过仪表控制总线icb与通道参数测试控制器ptc连接。11.优选的:每个唯一的仪表控制指令组合向量称为一个仪表控制指令组。12.优选的:两个以上的仪表控制指令组组成一个仪表控制指令表。13.优选的:每个唯一的仪表控制指令组合向量被赋予一个仪表控制指令值。14.一种集成电路并发测试方法,包括以下步骤:步骤1,测试处理器tp发出仪表控制消息icm,经过仪表控制总线icb的传输,进入每个测试通道的仪表控制总线控制器icbrc。15.步骤2,仪表控制总线控制器icbrc将仪表控制消息值icm转化为通道的仪表控制码icc。16.步骤3,仪表控制码icc再经过通道参数测试控制器ptc的解析,完成对模拟通道的最终控制。17.优选的:同一个仪表控制消息icm经过各个不同通道的仪表控制总线控制器icbrc,会映射为不同的仪表控制码icc,以对应各自通道的仪表控制指令ico。18.优选的:仪表控制总线控制器icbrc选择接收指定测试处理器的仪表控制消息icm,从而允许多个测试处理器并发控制各自指定的一组模拟测试通道。19.本发明相比现有技术,具有以下有益效果:本发明通过将数字信号测试与模拟信号测试都统一到测试处理器控制,从而避免了传统测试的各项问题,可以带来以下的优势:1.由于ate可以有多个测试处理器(可以为每个测试站分配一个测试处理器),而每个测试处理器可以异步并发的工作,从而可以很好的完成数字信号与模拟信号的异步并发混合测试。20.2.由于数字信号测试与模拟信号测试都由测试处理器直接完成,所以数字信号与模拟信号测试的时序可以精确同步,从而可以准确完成复杂的数字模拟信号混合测试要求。21.3.通过将数字信号测试的编程与模拟信号的编程统一在一个图形(pattern)文件中,从而降低了测试程序编写的难度,提高了混合信号测试程序开发调试的效率。附图说明22.图1为测试处理器内部结构原理图。23.图2为传统测试图形文件(pattern)示意图。24.图3为本发明实施例测试图形文件(pattern)示意图。25.图4为ico与icm转换表。26.图5为多通道并发测试装置控制示意图,具体为icm如何从测试处理器发送到模拟测试通道的过程。27.图6为多测试站数字模拟混合并发测试示意图。具体实施方式28.下面结合附图和具体实施例,进一步阐明本发明,应理解这些实例仅用于说明本发明而不用于限制本发明的范围,在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落于本技术所附权利要求所限定的范围。29.一种集成电路并发测试装置,如图1所示,包括测试处理器tp4(testprocessor,简称tp)、parameterpattern编译器ppc14(parameterpatterncompiler,简称ppc)、通道参数测试控制器ptc(parametertestcontroller,简称ptc)、仪表控制总线icb(instrumentscontrolbus,简称icb),其中:所述测试处理器4包括时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3、测试图形存储器、存储控制器、仪表控制总线命令发生器icmg5,所述存储控制器分别与时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3、仪表控制总线命令发生器5连接,所述测试图形发生器2分别与时序发生器tg1、信号处理单元控制指令发生器3连接。30.时序发生器tg1(timinggenerator,简称tg),用于按照图形文件指定的时序要求,产生每个周期所需的精确时序信号(包括周期,时沿等)。31.测试图形发生器2(patterngenerator),用于按照图形文件(patternfile)的指令要求,产生图形测试所需的控制时序(包括:跳转、循环等)。32.信号处理单元控制指令发生器3(signalprocessorunitcommandgenerator,spucg),用于根据图形文件控制数据要求,产生用于同步控制数字测试通道子系统的指令信号。33.测试处理器tp4(testprocessor,简称tp)。时序发生器tg1、测试图形发生器2、信号处理单元控制指令发生器3通过存储控制器(memorycontrol)访问测试图形存储器(patternmemory),获取指令和数据,时序发生器tg1负责产生当前周期相应的周期和时钟边沿等信息,并提供给其他模块。测试图形发生器2负责执行测试图形文件(pattern)中的指令要求,实现跳转、循环等,同时控制存储控制器(memorycontrol)对测试图形存储器(patternmemory)的地址访问。信号处理单元控制指令发生器3在测试图形发生器2的控制下,将测试子系统控制指令发送给相应的子系统,实现对子系统的同步控制。另外,从架构图可以看出测试处理器tp4是一个典型的冯诺伊曼结构的处理器,但指令集采用ate专用指令集,专用于处理信号,而非数据。34.所述仪表控制总线命令发生器icmg5(icmgenerator,icmg)用于将仪表控制指令ico(instrumentcontrolopcodes,简称ico,具体参考图3说明)转化为仪表控制消息icm(instrumentscontrolmessage,简称icm)。通过仪表控制总线icb传递给各个通道参数测试控制器ptc,从而测试处理器完成了对各个非数字通道的测试控制。35.如图2所示,为传统的测试处理器处理的pattern文件,传统的测试处理器处理的pattern文件由测试图形发生器控制指令11、时序设置12、数字通道列表13构成,提供了图形测试发生器所需的所有信息。36.测试图形发生器控制指令11(patterngeneratorcommand),产生图形测试所需的控制时序,包括:跳转(jump)、循环(repeat、loop)、停止(halt)等。37.时序设置12(timingset),定义了图形发生器产生每个周期所需的精确时序信信息(包括周期,时沿等)。38.数字通道列表13(digitalchannellist),描述了每个周期不同时序条件下各个数字通道的工作状态。根据需求这些通道可以被设定为不同模式,如:i/o既可以作为驱动管脚也可以作为接受管脚,其中驱动管脚的有效数据为0和1,接受管脚的有效数据为:l、h和x。39.从图3中可以看出,所有控制都是针对数字测试通道的,可以精确的描述每个数字测试通道的测试时序.本发明实施例在原有pattern的基础上新增了模拟通道管脚的控制指令内容,如图3所示,本实施例所述测试处理器tp4处理的测试图形发生器文件包括两个以上的仪表控制指令组合向量,仪表控制指令组合向量由测试图形发生器控制指令11、时序设置12、数字通道列表13、模拟器件管脚列表15组成,所述模拟器件管脚列表15由仪表控制指令组成。提供了测试处理器所需的所有信息。通过这些指令能在纯数字测试通道控制的基础上新增模拟测试通道的控制。从而可以同时将数字信号测试与模拟信号统一在一个pattern文件中进行描述。40.如图3所示,10为pattern文件的每一行表示一个向量(vector),此处列出向量索引只为后续介绍方便,在实际pattern不包含该向量的索引。测试图形发生器控制指令11、时序设置12、数字通道列表13与传统测试图形文件内容相同。41.模拟器件管脚列表15可以包含多个模拟器件通道控制(这里包含了3个),其内容是仪表控制指令(instrumentcontrolopcode,简称ico),通过这些指令可以定义模拟器件的状态,例如设置电压值(set_voltage1.8v)、将模拟通道输出设为高阻态(gate_off)、采集dut结果(strobe)等。42.因此本实施例所述测试处理器tp4处理的测试图形发生器文件pattern不仅可以控制数字测试通道也可以用于控制模拟通道,可以精确的描述每个数字、模拟测试通道的测试时序。43.接下来要解决的问题是,一个测试处理器如何将一组ico同时发送给多个不同的非数字测试通道的cptc,完成同步控制,并让各个通道实现不同的操作。44.首先需要将控制指令组转换为icm。如图4所示,说明了编译器如何将仪表控制指令ico如何转化为icm。45.新的pattern文件每个vector可以包含多个模拟测试通道指令列表,每行vector中的多个仪表控制指令(instrumentcontrolopcodes)代表一个仪表控制指令组合,每个唯一的控制指令组合称为一个仪表控制指令组(instrumentcontrolopcodesgroup,简称icog)(见图3),多个唯一的icog组成了一个icmtable,每一行icog被赋予一个icm值。46.如图4所示,图3中gate_off命令会被编译成ico1,set_voltage1.8v被编译成ico2、strobe被编译成ico3、gateon被编译成ico4等等。图3中有6个唯一的icog(vector5和vector7相同,所以只能算一种),编译后会生成6种不同的icm。47.parameterpattern编译器ppc14根据仪表控制指令与仪表控制消息转换表将仪表控制指令转换成仪表控制消息icm。所述parameterpattern编译器ppc14通过仪表控制总线icb与通道参数测试控制器ptc连接。48.parameterpattern编译器ppc14对整个pattern测试程序进行编译成设备能执行的命令。pattern测试程序根据测试需求可能包含仪器仪表相关的控制指令(还有许多其他控制命令)进行编译,这些被编译后的指令将会交给仪表控制总线命令发生器icmg5对命令进行解析,然后生成仪器仪表模块能识别的命令。这些命令会发送到仪表控制总线icb上,哪写仪器能识别这些命令通过仪表控制总线控制器icbrc进行管理。49.一种集成电路并发测试方法,如图5所示,包括以下步骤:步骤1,测试处理器tp4发出仪表控制消息icm,经过仪表控制总线icb的传输,进入每个测试通道的仪表控制总线控制器icbrc(icbreceivercontroller,简称icbrc)。50.步骤2,仪表控制总线控制器icbrc将仪表控制消息值icm转化为通道的仪表控制码icc(instrumentscontrolcode,简称icc)。51.步骤3,仪表控制码icc再经过通道参数测试控制器ptc的解析,完成对模拟通道的最终控制。52.其中,同一个仪表控制消息icm经过各个不同通道的仪表控制总线控制器icbrc,会映射为不同的仪表控制码icc,以对应各自通道的仪表控制指令ico。从而通过一个测试处理器,即可同步控制多个不同模拟测试通道,同时完成不同的测试。53.同时,仪表控制总线控制器icbrc可以选择接收指定测试处理器的仪表控制消息icm,从而允许多个测试处理器并发控制各自指定的一组模拟测试通道。如果为每个测试站分配一个测试处理器,即可实现多测试站的并发多时钟域测试。54.如图6所示,为出了两个测试站的情况,本发明也适用更多测试站的情况。从图6可以看出,每个测试站(deviceundertest,简称dut)都分配了一组数字测试通道,与一组模拟测试通道。分别都由一个独立测试处理器控制。当两个测试处理器工作在不同的时钟域时,两个测试站即可工作在并发测试状态。从图6中可以看出,数字测试通道与模拟测试通道的控制在测试过程中不需要pc的参与。多时钟域测试也适用于单测试站内部的情况。55.本发明可以实现数字测试与模拟测试统一在同一个pattern文件,简化测试程序开发。可以同步并发的控制数字测试通道与模拟测试通道,不需要在测试处理器与pc处理器直接切换,提高测试效率,降低测试成本。可以实现模拟测试通道与数字测试通道的精确同步,从而实现更复杂的集成电路参数测试,提高测试覆盖率。56.以上所述仅是本发明的优选实施方式,应当指出:对于本

技术领域:

:的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。当前第1页12当前第1页12

再多了解一些

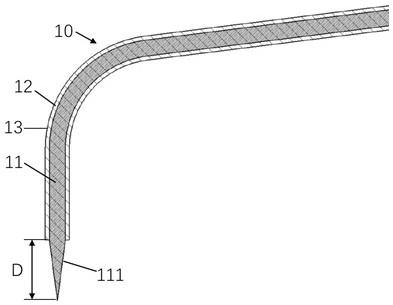

本文用于企业家、创业者技术爱好者查询,结果仅供参考。