处理系统、相关集成电路和方法

1.相关申请的交叉引用

2.本技术要求于2020年12月17日提交的意大利专利申请第102020000031235号的优先权,该申请通过引用并入本文。

技术领域

3.本公开总体上涉及一种电子系统和方法,并且,在特定实施例中,涉及一种处理系统、相关集成电路和方法。

背景技术:

4.包括至少一个数字处理单元的数字处理系统,例如片上系统(soc)是本领域公知的。

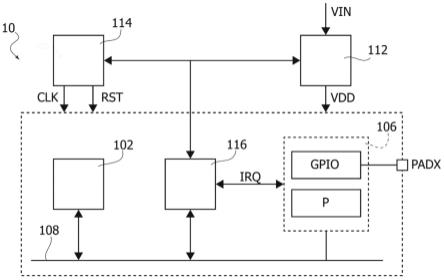

5.图1示出了示例性数字处理系统10(例如soc)的框图,即,图1的处理系统可以集成在集成电路中,例如微控制器或数字信号处理器(dsp)。在所考虑的示例中,处理系统10包括经由软件指令编程的至少一个可编程数字处理单元102,例如微处理器,通常是中央处理单元(cpu)。

6.已知大量的微处理器/cpu体系结构。例如,如美国专利号us6,889,317b2中所公开的,并为此目的通过引用并入本文中,微处理器/cpu 102通常包括:

[0007]-一个或多个算术逻辑单元(alu),被配置为实现多个算术逻辑操作;

[0008]-多个寄存器;

[0009]-路由电路,例如多路复用器和解复用器的形式,被配置为将alu连接到寄存器;以及

[0010]-指令解码器,被配置为根据当前软件指令来驱动路由电路和一个或多个alu,例如,为了将至少一个寄存器连接到alu的输入并且将寄存器连接到alu的输出,选择要由一个或多个alu执行的算术操作,与存储器交换数据等。

[0011]

通常,由处理单元/cpu 102执行的软件存储在程序存储器104中,例如非易失性存储器,例如闪存或eeprom。通常,存储器104可以在单个集成电路中与处理单元102集成,或者存储器104可以以单独集成电路的形式并且例如经由印刷电路板的迹线连接到处理单元102。因此,通常,存储器104被配置为存储处理单元102的固件/软件。

[0012]

通常,处理单元/cpu 102还关联易失性存储器100,例如随机存取存储器(ram),用于存储计算的临时结果。此外,存储器100可以在单个集成电路中与处理单元102集成,或者存储器100可以以单独集成电路的形式并连接到处理单元102。

[0013]

在所考虑的示例中,处理单元/cpu 102可以与从以下组中选择的一个或多个资源106相关联:

[0014]-一个或多个通用输入/输出gpio;

[0015]-一个或多个通信接口if,例如用于经由通信系统20交换数据,例如经由通用异步接收机/发射机(uart)、串行外围接口总线(spi)、集成电路间(i2c)、控制器局域网(can)总

线和/或以太网接口和/或调试接口;和/或

[0016]-一个或多个模数转换器ad和/或数模转换器da;和/或

[0017]-一个或多个专用数字组件dc,例如硬件定时器和/或计数器,或密码协处理器;和/或

[0018]-一个或多个模拟组件ac,例如比较器、传感器,例如温度传感器等;和/或

[0019]-一个或多个混合信号组件msc,例如pwm(脉宽调制)驱动器。

[0020]

因此,数字处理系统10可以支持不同的功能。例如,处理单元102的行为由存储在存储器104a中的固件确定,例如,由soc 10的微处理器/cpu 102(诸如微控制器或dsp)执行的软件指令。因此,通过安装不同的固件,相同的硬件(soc)可以用于不同的应用。

[0021]

在许多应用中,处理系统10可支持低功率模式,以减少处理系统10的功率消耗。例如,这在电池供电系统的情况下或对于实现包括处理系统10的电子系统的待机模式来说特别重要。

[0022]

例如,图2示出了处理系统10的第二示例,为了简单起见,其仅示出了相关部分。具体地,图2示出了典型的处理系统10还可以包括:

[0023]-振荡器和复位电路114,被配置为提供时钟信号clk和复位信号rst;以及

[0024]-电源电路112,例如电子转换器或线性调节器,被配置为从输入电压vin产生处理系统10的电源电压vdd。

[0025]

通常,这些电路114和/或112可以集成在包括处理单元102的集成电路/soc中,或者可以(至少部分地)相对于处理单元102的集成电路/soc在外部。例如,电源电路112的控制电路可以集成在集成电路/soc中,而电源电路112的较大电感器和/或电容器可以外部连接到集成电路。

[0026]

例如,典型地,振荡器和复位电路114被配置为一旦提供了电源电压vdd就产生处理系统10的时钟信号clk,然后经由复位信号rst产生复位,以便使处理系统进入复位状态。例如,为此目的,通常重置处理系统10的各种寄存器,例如,重置处理单元102和资源106的寄存器。

[0027]

在所考虑的示例中,处理系统10还包括功率管理电路116。具体地,该功率管理电路116被配置为选择性地激活正常工作模式或低功率模式。例如,如图2中示意性示出的,功率管理电路116可被配置为驱动振荡器和复位电路114,以便降低时钟信号clk的频率或甚至关断至少提供给处理单元102的时钟信号中的时钟信号clk的产生。因此,在低功率模式中,处理单元102可以以减小的时钟频率操作,或者可以暂停。相反,当恢复正常工作模式时,功率管理电路116可被配置为驱动振荡器和复位电路114,以便再次使用时钟信号clk的正常(较高)频率。

[0028]

关断时钟信号clk可能导致处理单元102不能执行任何操作。为此,功率管理电路116可被配置为响应于一个或多个事件恢复正常工作模式(具有正常时钟频率)。例如,通常这些事件对应于由一个或多个资源106提供的一个或多个唤醒信号irq,例如输入引脚的逻辑电平的改变或由诸如定时器、比较器等的另一个资源p产生的中断。例如,虽然未在图2中示出,但为此目的,包括时序逻辑电路的一个或多个资源106仍然可以接收时钟信号clk或另一个(通常是低频)时钟信号,或者可以异步地产生唤醒信号irq。

[0029]

因此,通常,功率管理电路116可经由处理单元102编程/配置,例如,通过执行用于

编程功率管理电路116的多个寄存器中的一个寄存器的一个或多个软件指令。例如,为此目的,功率管理电路116可以类似于资源106,例如经由总线系统108连接到处理单元102。例如,功率管理电路116通常是可编程的,以便选择功率节省模式和/或选择唤醒源,其应该恢复正常工作模式。

[0030]

为了进一步降低功率,功率管理电路116还可以被配置为去激活处理系统10的电源。但是,这可能导致处理系统的寄存器丢失其内容。

[0031]

因此,为了避免这种信息丢失,处理系统10可以对寄存器使用所谓的保持触发器,寄存器必须保持配置。保持触发器在本领域中是公知的,并且例如在美国专利申请号us 2018/0159513 a1中公开,为此目的将其内容通过引用结合于此。例如,典型地,保持触发器用经由第一电源电压供电的主锁存器和由第二电源电压供电的从锁存器来实现,并且控制部被配置为:

[0032]-在激活低功率模式之前,还将主锁存器的信息存储到从锁存器;

[0033]-当退出低功率模式时,从所述从锁存器中恢复信息。

[0034]

因此,在低功率模式下,主锁存器和控制部的电源电压可以被去激活,而从锁存器仍然存储原始数据。

技术实现要素:

[0035]

发明人已经观察到保持触发器有几个缺点。

[0036]

一方面,保持触发器是复杂的,由于双锁存器结构,保持触发器很大。因此,使用这样的保持触发器(在处理单元/cpu 102和资源106中)可能不适用于所有应用。

[0037]

另一方面,保持触发器在低功率模式下也继续消耗能量。因此,对处理单元/cpu 102使用保持触发器仍然可能导致过度的功率消耗。

[0038]

此外,保持触发器只允许在低功率模式结束时从从锁存器恢复信息。因此,存储到保持触发器的数据不能在低功率模式中使用。例如,该问题在cpu和通用输入/输出的上下文中可能特别相关,其中集成电路(包括处理系统10)的管芯的每个焊盘可能具有相关联的几个配置位。然而,如前所述,这种通用输入/输出可以直接是用于恢复正常工作模式的唤醒信号的源,或者用于产生唤醒信号的另一资源106仍然能够经由集成电路的焊盘发送和/或接收数据,例如通信接口。在这方面,现代片上系统还可以包括大量gpio焊盘。

[0039]

一些实施例涉及诸如片上系统(soc)的处理系统内的通用输入/输出的管理。

[0040]

一些实施例提供用于管理集成电路的通用输入/输出焊盘的解决方案,特别是用于实现低功率工作模式。

[0041]

一些实施例提供了通过使用具有所附权利要求中具体阐述的特征的处理系统来管理集成电路的通用输入/输出焊盘的解决方案。一些实施例还涉及相关的集成电路和方法。

[0042]

权利要求是本文提供的本公开的技术教导的组成部分。

[0043]

各种实施例涉及包括至少一个焊盘的处理系统,例如集成电路,例如片上系统。

[0044]

具体地,在各种实施例中,处理系统包括第一子电路、第二子电路和电源电路。电源电路被配置为接收输入电压并产生用于第一子电路的第一电源电压和用于第二子电路的第二电源电压。此外,电源电路被配置为根据第一控制信号选择性地关断第一电源电压,

从而关断第一子电路。

[0045]

在各种实施例中,第一子电路包括被配置为通过软件指令编程的数字处理单元,例如微处理器,优选是cpu,以及被配置为通过由数字处理单元执行的软件指令编程的通用输入/输出寄存器。具体地,在各种实施例中,通用输入/输出寄存器被配置为与至少一个焊盘连接。为此目的,通用输入/输出寄存器可接收(至少)第一数据输入信号并提供包括第一输出使能信号、第一数据输出信号和外围设备选择信号的配置数据,即,通用输入/输出寄存器被配置为从数字处理单元接收配置数据并将第一数据输入信号的值提供给数字处理单元。

[0046]

在各种实施例中,第二子电路包括用于焊盘的输入/输出接口。具体地,在各种实施例中,输入/输出接口包括输出驱动器,输出驱动器被配置为经由输出使能信号使能,并且当使能时,根据二进制数据输出信号的逻辑电平向焊盘施加电压(通常是第二电源电压或地)。此外,输入/输出接口包括输入缓冲器,输入缓冲器被配置为根据焊盘处的电压产生二进制数据输入信号。

[0047]

在各种实施例中,存储到通用输入/输出寄存器的配置数据不直接提供给输入/输出接口。具体地,在各种实施例中,第二子电路包括存储电路,该存储电路包括多个锁存器,例如d型锁存器,用于提供所存储的配置数据,该配置数据包括所存储的第一输出使能信号、所存储的第一数据输出信号和所存储的外围设备选择信号。具体地,多个锁存器被配置为根据第二控制信号提供或保持施加到多个锁存器的相应输入端子的配置数据。具体地,锁存器被配置为:

[0048]-当第二控制信号具有第一逻辑电平(例如,高)时,在锁存器的输出端子处提供施加到锁存器的输入端子的配置数据,即,锁存器基本上是透明的,并且

[0049]-当第二控制信号具有第二逻辑电平(例如,低)时,锁存器在锁存器的输出端子处保持配置数据的值。

[0050]

在各种实施例中,存储电路还可以包括针对多个锁存器中的每一个锁存器的相应隔离单元。具体地,这些隔离单元被配置为根据第三控制信号选择性地将通用输入/输出寄存器连接到多个锁存器的输入端子,从而选择性地将配置数据提供到多个锁存器的输入。

[0051]

在各种实施例中,第二子电路还可以包括至少一个外围设备,例如通信接口,例如can或spi接口,被配置为接收第二数据输入信号并提供第二输出使能信号和第二数据输出信号。在这种情况下,第二子电路可以包括第一选择电路,第一选择电路被配置为根据所存储的第一数据输出信号、第二数据输出信号和所存储的外围设备选择信号来确定输入/输出接口的数据输出信号的逻辑电平。例如,第一选择电路可被配置为根据所存储的外围设备选择信号选择所存储的第一数据输出信号或第二数据输出信号作为数据输出信号。

[0052]

类似地,第二选择电路可被配置为根据所存储的第一输出使能信号、第二输出使能信号和所存储的外围设备选择信号来确定输入/输出接口的输出使能信号的逻辑电平。例如,第二选择电路可被配置为根据所存储的外围设备选择信号选择所存储的第一输出使能信号或第二输出使能信号作为输出使能信号。

[0053]

类似地,第三选择电路可被配置为根据所存储的外围设备选择信号提供输入/输出接口的数据输入信号作为第一数据输入信号或第二数据输入信号。

[0054]

在各种实施例中,第二子电路还包括被配置为管理正常工作模式和低功率模式的

功率管理电路。具体地,在各种实施例中,功率管理电路被配置为从数字处理单元接收用于激活低功率模式的一个或多个命令。具体地,响应于接收到用于激活低功率模式的一个或多个命令,功率管理电路可设置第二控制信号以指示多个锁存器应保持配置数据,设置第三控制信号以断开通用输入/输出寄存器与多个锁存器的输入的连接,以及设置第一控制信号以关断第一电源电压。

[0055]

相反,为了恢复正常工作模式,功率管理电路可以监测一个或多个唤醒信号以确定唤醒事件。例如,为此目的,功率管理电路可以被配置为接收多个唤醒信号,根据给定配置数据选择唤醒信号的子集,并且监测所选择的唤醒信号的子集,以便确定唤醒事件。具体地,在各种实施例中,响应于确定唤醒事件,功率管理电路设置第一控制信号以接通第一电源电压,从而激活正常工作模式,并设置第三控制信号以将通用输入/输出寄存器连接到多个锁存器的输入。

[0056]

因此,在各种实施例中,功率管理电路不响应于唤醒事件直接设置第二控制信号。事实上,在各种实施例中,功率管理电路被配置为从数字处理单元接收用于重新激活多个锁存器的单独命令。因此,响应于接收到用于重新激活多个锁存器的命令,功率管理电路可以设置第二控制信号以指示多个锁存器应该提供施加到锁存器的输入端子的配置数据。

[0057]

例如,为了管理上述操作,功率管理电路可以包括被配置为经由数字处理单元编程的另一寄存器,其中,另一寄存器包括第一配置数据和第二配置数据。具体地,在各种实施例中,第二控制信号可以根据第一配置数据而被确定,并且第一控制信号和第三控制信号可以根据第二配置数据而被确定。例如,在这种情况下,用于激活低功率模式的一个或多个命令可以包括用于编程第一配置数据的第一命令,从而设置第二控制信号以指示多个锁存器应该保持配置数据。该一个或多个命令还可包括用于编程第二配置数据的第二命令,从而设置第三控制信号以断开通用输入/输出寄存器与多个锁存器的输入的连接,以及设置第一控制信号以关断第一电源电压。相反,用于重新激活多个锁存器的命令可以包括用于编程第一配置数据的第三命令,从而设置第二控制信号以指示多个锁存器应该提供施加到锁存器的输入端子的配置数据。

[0058]

事实上,如前所述,数字处理单元和通用输入/输出寄存器在第一子电路中,并且因此在低功率模式下关断。因此,这些电路在低功率模式期间可能失去它们的配置。例如,在各种实施例中,处理系统还包括振荡器和复位电路,该振荡器和复位电路被配置为当第一电源电压接通时产生第一子电路的复位。例如,在各种实施例中,数字处理单元可以是微处理器,优选地是cpu,包括多个寄存器。在这种情况下,微处理器的多个寄存器和通用输入/输出寄存器可以响应于复位信号而复位。

[0059]

因此,响应于唤醒事件直接设置第二控制信号可能意味着锁存器获取通用输入/输出寄存器中的未编程/复位值。因此,在必须改变焊盘的配置的情况下,由数字处理单元执行的软件指令不仅包括用于激活低功率模式的一个或多个命令,而且在系统启动之后,还包括用于编程通用输入/输出寄存器的指令,以及仅在此之后用于重新激活多个锁存器的命令。

[0060]

因此,在各种实施例中,根据本公开的处理系统可以以以下方式操作。

[0061]

首先,输入电压被提供给电源电路,由此电源电路产生用于第一子电路的第一电源电压和用于第二子电路的第二电源电压。

[0062]

接着,数字处理单元将第一次配置数据编程到通用输入/输出寄存器,并且(例如,在执行给定任务之后)将用于激活低功率模式的一个或多个命令发送到功率管理电路。因此,功率管理电路设置第二控制信号以指示多个锁存器应该保持配置数据,设置第三控制信号以断开通用输入/输出寄存器与多个锁存器的输入的连接,以及设置第一控制信号以关断第一电源电压。

[0063]

接着,功率管理电路监测一个或多个唤醒信号以确定唤醒事件。响应于确定唤醒事件,功率管理电路设置第一控制信号以接通第一电源电压,从而激活正常工作模式,并设置第三控制信号以将通用输入/输出寄存器连接到多个锁存器的输入。

[0064]

因此,电源电路再次向第一子电路提供第一电源电压,并且处理单元和通用输入/输出寄存器被接通。因此,响应于激活正常工作模式,数字处理单元可将第二次(相同或不同)配置数据编程到通用输入/输出寄存器,并且仅在此时将用于重新激活多个锁存器的命令发送到功率管理电路,由此功率管理电路设置第二控制信号以指示多个锁存器应再次提供应用到锁存器的输入端子的配置数据。

[0065]

在必须保持微处理器的寄存器的内容的情况下,第二子电路可包括易失性存储器,并且微处理器/cpu可被配置为执行:

[0066]-在发送用于激活低功率模式的一个或多个命令之前,执行用于将微处理器的寄存器的内容存储到易失性存储器中的给定位置的指令,并且

[0067]-在微处理器复位之后,执行用于读取易失性存储器中的给定位置的内容并将该内容存储到微处理器的寄存器的指令。

附图说明

[0068]

现在将参考所附附图来描述本公开的实施例,所附附图纯粹通过非限制性示例的方式提供,并且其中:

[0069]-图1示出了处理系统的示例;

[0070]-图2示出了包括功率管理电路的处理系统的示例;

[0071]-图3示出了根据本公开的处理系统的实施例;

[0072]-图4示出了图3的处理系统的存储电路的实施例;

[0073]

图5、图6和图7示出了图3的处理系统的选择器电路的实施例;和

[0074]

图8和图9示出了图3的处理系统的功率管理电路的实施例。

具体实施方式

[0075]

在下面的描述中,给出了许多具体细节以提供对实施例的彻底理解。可以在没有一个或几个特定细节的情况下,或者用其他方法、部件、材料等来实践实施例。在其他实例中,未详细示出或描述公知的结构、材料或操作,以避免模糊实施例的方面。

[0076]

在本说明书中对“一个实施例”或“实施例”的引用意味着结合该实施例描述的特定特征、结构或特性包括在至少一个实施例中。因此,短语“在一个实施例中”或“在实施例中”在整个说明书的各个地方的出现不一定都指同一实施例。此外,在一个或多个实施例中,特定特征、结构或特性可以以任何合适的方式组合。

[0077]

本文提供的标题仅是为了方便,并且不解释实施例的范围或含义。

[0078]

在下面的图3至图9中,已经参照图1和图2描述的部件、元件或组件用以前在这些图中使用的相同的参考符号表示;为了不给本详细描述增加负担,在下面将不再重复对这些先前描述的元件的描述。

[0079]

如上文关于图1和图2所述,在许多应用中,数字处理系统10应该能够激活正常模式和低功率模式。优选地,数字处理系统10的未使用组件应该能够在低功率模式下被关闭,而通用输入/输出gpio应该保持它们的配置。

[0080]

图3示出了根据本公开的处理系统10a的实施例。

[0081]

具体地,在所考虑的实施例中,处理系统10a包括:

[0082]-电源电路112a,被配置为产生第一电源电压vdd1和第二电源电压vdd2;

[0083]-复位和振荡器电路114,被配置为产生至少一个时钟信号clk和复位信号rst;

[0084]-由第一电源电压vdd1供电的第一子电路30,其中,第一子电路30包括处理系统的处理单元102,例如微处理器或cpu,以及通用输入/输出控制器gpio;和

[0085]-第二子电路32,由第二电源电压vdd2供电,其中,第二子电路30包括集成电路的多个n个通用输入/输出焊盘pad1、padn。

[0086]

通常,集成电路/soc的管芯的这些焊盘pad1、padn可以连接到集成电路的封装件的各个引脚,或者可以连接(例如,通过引线键合)到pcb。

[0087]

如图3所示,每个焊盘pad1

…

padn(在图3中示出了通用焊盘padx)都具有相关联的可配置输入/输出(i/o)电路130。具体地,输入/输出电路130包括:

[0088]-输出驱动器1300,被配置为根据二进制数据信号dout和输出使能信号oen来设置焊盘padx的逻辑电平;和

[0089]-输入缓冲器1302,被配置为根据焊盘padx处的电压来设置二进制数据信号din的逻辑电平。

[0090]

例如,输出驱动器1300可以被配置为:

[0091]-当信号dout被设置为低电平且信号oen具有第一逻辑电平(通常为高)时,将焊盘padx连接到地,即电源电压vdd1和vdd2的参考电压;

[0092]-当信号dout设置为高且信号oen具有第一逻辑电平时,将焊盘padx连接到电源电压vdd2;并且

[0093]-当信号oen具有第二逻辑电平(通常为低电平)时,禁用输出驱动器1300的输出。

[0094]

因此,在所考虑的实施例中,输出驱动器1300被配置为三状态输出驱动器(0辑电平和1逻辑电平,以及高阻抗状态)。

[0095]

相反,输入缓冲器1302,例如施密特触发器,可以被配置为:

[0096]-当焊盘padx处的电压大于上阈值时,将信号din设置为高;并且

[0097]-当焊盘padx处的电压小于低阈值时,将信号din设置为低。

[0098]

在各种实施例中,信号dout和oen的逻辑电平根据多个位来确定,该多个位可经由处理单元102编程。例如,在所考虑的实施例中,处理单元包括寄存器接口gpio,其中,处理单元102被配置为读取和/或写入接口gpio的寄存器的一个或多个位。例如,在各种实施例中,寄存器gpio在处理单元102的存储器空间中是可寻址的,例如,在微处理器/cpu 102的所谓特殊功能寄存器(sfr)中。例如,如图3中示意性示出的,寄存器接口gpio可以经由总线系统108连接到处理单元102。

[0099]

例如,每个焊盘padx可以具有相关联的:

[0100]-位odr,用于设置信号dout的逻辑电平;以及

[0101]-一个或多个位gpioconfig,用于设置信号oen。

[0102]

因此,通过对接口gpio的位odr和gpioconfig进行编程,处理单元102可以设置焊盘padx的逻辑电平。类似地,信号din可以存储在接口gpio的位idr中。因此,通过读取位idr,处理单元102可以确定/读取焊盘padx的逻辑电平。

[0103]

具体地,如以下将更详细地描述的,在各种实施例中,处理系统10a包括存储电路118,存储电路118被配置为存储由接口gpio提供的配置信号的值,例如gpioconf和odr,并向i/o接口130提供相应的存储值,例如gpioconf'和odr'。

[0104]

如图3所示,信号dout和oen确实可以分别由选择器电路124和126提供。类似地,信号din可以经由选择器电路128提供给多个电路。

[0105]

例如,在处理系统10还包括配置为与输入/输出电路130直接交换数据的一个或多个资源106的情况下,电路124、126和128是有用的。例如,在图3中示出了两个通用资源120和122,例如通信接口。

[0106]

例如,电路120被配置为:

[0107]-产生输出信号p1_out和输出使能信号p1_oen;和/或

[0108]-接收输入信号p1_in。

[0109]

类似地,电路122被配置为:

[0110]-产生输出信号p2_out和输出使能信号p2_oen;和/或

[0111]-接收输入信号p2_in。

[0112]

通常,措辞“和/或”强调电路120和122也可以仅接收数据或仅发送数据。例如,在这种情况下,相应的输出使能信号也可以是硬连线的。

[0113]

因此,在这种情况下,选择器电路124可被配置为通过选择信号odr'(由存储电路118提供)或由资源120和122提供的输出信号之一来产生信号dout。类似地,选择器电路126可被配置为根据配置位gpioconf'中的一个或多个(由存储电路118提供)或由资源120和122提供的输出使能信号中的一个来产生信号oen。最后,电路128可被配置为将信号din提供给存储电路118(经由信号idr',然后将其作为信号idr提供给接口gpio)或资源120和122之一。

[0114]

例如,在各种实施例中,通过寄存器gpio中的一个或多个位persel,以及可选地通过寄存器gpio中的一个或多个位gpioconfig来控制在电路124、126和128内执行的选择。具体地,同样在这种情况下,存储电路118可以接收这些信号并提供信号persel'和可选地提供信号gpioconfig'。

[0115]

在下面,现在将描述控制器寄存器gpio中的每个焊盘padx的位的可能实施例。

[0116]

在各种实施例中,两个位gpioconf[1:0]:用于将相应的padx配置为输入或输出,或者配置为连接到外围设备/资源的焊盘。例如,可以使用以下位映射:

[0117]

00:padx被配置为输入;

[0118]

01:padx被配置为输出;

[0119]

1x:padx被配置为外围i/o,其中“x”表示相应的位可以是1或0。

[0120]

因此,在所考虑的实施例中,每个padx可以根据相应的两个位gpioconf[1:0]的值

被配置为输入、输出或外围i/o。

[0121]

在各种实施例中,给定数目的位用于外围选择位persel。例如,在所考虑的实施例中使用两个可能的外围设备120和122。因此,单个位可以足够,例如:

[0122]

0:padx被配置为外围设备120;并且

[0123]

1:padx被配置为外围设备122。

[0124]

如前所述,寄存器的宽度是一位,因为在实施例中只考虑两个外围设备。例如,对于数量为y的外围设备,信号persel至少应该具有log2(y)位。

[0125]

例如,图5、图6和图7分别示出选择器电路124、126和128的可能实施例。

[0126]

例如,如图5所示,根据信号psel,第一多路复用器1240可用于在由外围设备120和122提供的输出信号p1_out和p2_out中选择输出信号p_out。例如,信号psel可以对应于信号persel'(由存储电路118提供),或者如图5所示,仅当相应位gpioconf'[1](由存储电路118提供)也被设置为高(即,padx被配置为外围i/o)时,信号psel才对应于信号persel',如经由电子开关1242示意性示出的。因此,另一多路复用器1244可用于根据位gpioconf'[1]选择信号odr'(由存储电路118提供)或信号p_out作为信号dout。

[0127]

类似地,如图6所示,选择器电路126可以包括第一多路复用器1260,该第一多路复用器1260被配置为根据信号psel在由外围设备120和122提供的输出使能信号p1_oen和p2_oen中选择输出使能信号p_oen。因此,另一多路复用器1262可用于根据位gpioconf'[1](由存储电路118提供)选择位gpioconf'[0](当padx被配置为输入时设置为0,当padx被配置为输出时设置为1)或信号p_oen作为信号oen。

[0128]

以互补的方式,如图7所示,电路128可以包括解复用器1280,该解复用器1280被配置为根据位gpioconf'[1]提供信号din作为信号idr(位gpioconf'[1]被设置为低)或作为信号p_in(位gpioconf'[1]被设置为高)。此外,第二多路复用器可被配置为根据信号psel,将信号p_on作为信号p1_on或p2_on提供给外围设备120或122之一。

[0129]

通常,基于用于信号din、dout和oen的逻辑电平,当与i/o接口130在电路118、120和122之间交换信号时,可以执行一个或多个信号的逻辑电平的反转。例如,在各种实施例中,多路复用器1264可以不接收信号odr',而是接收由存储电路118提供的信号odr'的反转版本。

[0130]

具体地,如前所述,处理系统10a包括由电压vdd1提供的第一子电路30和由电压vdd2提供的第二子电路32。具体地,也如图3所示:

[0131]-第一子电路30包括微处理器102和寄存器接口gpio;并且

[0132]-第二子电路32包括i/o接口130和块120、122、124、126和128。

[0133]

如图3中示意性示出的,在各种实施例中,处理系统10a包括功率管理电路116a,其可以经由由处理单元102执行的软件指令来配置。具体地,功率管理电路116a位于子电路32中,因此经由电源电压vdd2供电。例如,为了与处理单元102交换数据,功率管理电路116a可以包括一个或多个寄存器,这些寄存器可经由处理单元102编程。例如,在图3中,功率管理电路116a连接到总线系统108。

[0134]

例如,在各种实施例中,功率管理电路116a可以被配置为:

[0135]-一旦处理单元102发送给定命令,例如对功率管理电路116a的寄存器接口的给定位进行编程,就激活低功率模式;并且

[0136]-响应于一个或多个唤醒事件,例如逻辑电平的改变或唤醒信号irq中的触发,恢复正常工作模式。

[0137]

例如,当激活低功率模式时,功率管理电路116a可以设置一个或多个信号poff(例如,高),该信号被提供给电源电路112a以及可选地振荡器和复位电路114,以便执行以下操作中的至少一个:

[0138]-关断子电路30的电源电压vdd1;

[0139]-降低由振荡器电路114产生的时钟信号clk的频率;

[0140]-去激活提供给子电路30的时钟信号。

[0141]

具体地,在各种实施例中,处理系统10a可包括:

[0142]-子电路30中的第一振荡器和复位电路114,并因此经由电源电压vdd1被供电;

[0143]-子电路32中的第二振荡器和复位电路114,并因此经由电源电压vdd2被供电。

[0144]

因此,在这种情况下,当关断电源电压vdd1时,也关断第一振荡器和复位电路114,从而去激活提供给子电路30的时序逻辑电路的时钟信号。相反,子电路32的时序逻辑电路仍然从第二振荡器和复位电路114接收时钟信号。因此,在各种实施例中,第二振荡器和复位电路114的振荡器具有比第一振荡器和复位电路114的振荡器更低的频率。

[0145]

在功率管理电路116a支持多种模式的情况下,功率管理电路116a的寄存器接口可以包括一个或多个位模式,用于选择将在低功率模式中使用的上述模式中的至少一个(也参见图9,其将在下面更详细地描述)。

[0146]

通常,响应于唤醒事件,功率管理电路116a因此可以恢复先前的工作模式,例如:

[0147]-接通子电路30的电源电压vdd1;并且

[0148]-激活提供给子电路30的时钟信号。

[0149]

在各种实施例中,用于恢复正常工作模式的唤醒信号irq可由子电路32内的任何电路产生,例如:

[0150]-功率管理电路116a可被配置为确定由i/o接口130提供的信号din或由电路128提供的信号idr'中的一个或多个是否改变逻辑电平(例如,从高到低,或从低到高);和/或

[0151]-唤醒信号irq可以由外围设备120和122中的一个或多个产生。

[0152]

在功率管理电路116a支持多个唤醒源的情况下,功率管理电路116a的寄存器接口可以包括一个或多个位wen,用于选择确实应该使能哪个唤醒信号以恢复正常工作模式(也参见图9,其将在下面更详细地描述)。

[0153]

因此,在各种实施例中,应该在低功率模式(例如,用于产生用于恢复正常工作模式的唤醒信号irq)中保持接通的外围设备由子电路32中的电源电压vdd2供电。

[0154]

如图3所示,通用输入/输出的寄存器接口gpio在子电路30中,并且因此由电压vdd1提供。因此,当关断电源电压vdd1时,寄存器接口gpio失去其配置。然而,这也意味着由电路gpio提供的各种配置信号,如信号gpioconf、odr和presel将失去它们的值。

[0155]

因此,在各种实施例中,处理系统10a包括前面提到的存储电路118,该存储电路118被配置为存储配置信号的值,例如gpioconf、odr和presel,并将相应的存储值,例如gpioconf'、odr'和presel',提供给i/o接口130和选择电路124、126和128。具体地,在所考虑的实施例中,存储电路118位于子电路32中,因此经由电源电压vdd2供电。

[0156]

例如,图4示出存储电路118的可能实施例。

[0157]

如前所述,寄存器接口gpio可以经由处理单元102被编程。在各种实施例中,寄存器接口gpio也可以直接集成在处理单元102中。例如,如前所述,寄存器接口可包括用于每个焊盘pad1

…

padn的以下位:

[0158]-可写(和可选地可读)位gpioconf,用于设置相应焊盘padx的模式(输入、输出或可选地连接到外围设备);

[0159]-可写(和可选地可读)位persel,用于选择要连接到相应焊盘padx的外围设备120或122;

[0160]-可写(和可选地可读)位odr,当焊盘被配置为输出时,用于设置相应焊盘padx的值(高或低);和

[0161]-可读位idr,指示相应焊盘padx的逻辑电平。

[0162]

在各种实施例中,存储电路118被配置为存储寄存器接口gpio的位,这些位用于配置i/o接口130。例如,在所考虑的实施例中,存储电路118被配置为存储位gpioconf、persel和odr的值,从而提供这些位gpioconf'、persel

‘

和odr的存储版本。

[0163]

具体地,在各种实施例中,存储电路118针对要存储的每个配置位包括相应的存储元件,例如锁存器,例如d型锁存器。具体地,在各种实施例中,存储元件不使用时钟信号,从而避免在寄存器接口gpio中的位的编程和到i/o接口130的传播之间的显著延迟。例如,在图4中示出了用于存储信号gpioconf、persel和odr的位的锁存器l1、l2和l3,并且其中,这些锁存器提供信号gpioconf'、persel'和odr'。在一些实施例中,例如,锁存器l1可包括多个锁存器(例如,用于gpioconf'[0]、gpioconf'[1])。

[0164]

具体地,在所考虑的实施例中,存储元件被配置为:

[0165]-当信号lconf具有第一逻辑电平(例如,高)时,提供施加到相应输入的信号的逻辑电平;并且

[0166]-当信号lconf具有第二逻辑电平(例如,低)时,保持逻辑电平。

[0167]

此外,在各种实施例中,每个配置位经由被配置为当信号iso具有给定逻辑值(例如高)时向相应存储元件(l1

…

l3)提供配置位的相应开关元件/电路被提供到相应存储元件(l1

…

l3)的输入。例如,在所考虑的实施例中,开关元件用隔离单元实现,隔离单元示意性地示出为逻辑与门,即用于存储元件l1、l2和l3的隔离单元a1、a2和a3。隔离单元在本领域中是公知的,并且可以参考例如美国专利us 7,167,017 b2或us 6,977,833 b2,其内容通过引用并入本文。通常,隔离单元也可以用电子开关或传输门来实现。

[0168]

因此,在所考虑的实施例中,每个配置位可以根据以下两个信号选择性地存储在相应存储元件(l1,l2,l3)中:

[0169]-第一信号lconf,选择性地启用或禁用提供给存储元件的输入的信号的存储;以及

[0170]-第二信号iso,选择性地向相应存储元件的输入提供配置位。

[0171]

因此,在一些实施例中,当信号lconf具有第一逻辑电平(例如,高)时,来自隔离单元(例如,a1、a2、a3)的相应逻辑值由相应存储元件(例如,l1、l2、l3)传播到电路124、126和126;当信号lconf具有第二逻辑电平(例如,低)时,存储在锁存器(例如,l1,l2,l3)中的逻辑值保持它们各自的值,并且锁存器(例如,l1,l2,l3)将这些存储值提供给电路124、126和126。在一些实施例中,当信号lconf具有第二逻辑电平(例如,低)时存储在锁存器中的逻辑

值对应于当信号lconf具有第一逻辑电平(例如,高)时在锁存器的相应输入(例如,l1、l2、l3)处的最后逻辑值。

[0172]

如图4所示,由电路128提供的信号idr'可以直接提供给寄存器接口gpio中的相应位idr。

[0173]

因此,在所考虑的实施例中,功率管理电路116a被配置为还产生信号iso和lconf。

[0174]

例如,图8示出功率管理电路116a的可能实施例。

[0175]

具体地,在所考虑的实施例中,并且如前所述,功率管理电路116a经由电源电压vdd2供电,并且包括:

[0176]-可经由处理单元102编程的寄存器接口1162;以及

[0177]-控制电路1164。

[0178]

具体地,在各种实施例中,控制电路1164是时序逻辑电路(例如有限状态机)或优选地是组合逻辑电路,被配置为根据存储到寄存器接口1162的配置数据和一个或多个唤醒信号irq产生:

[0179]-电源电路112a和可选地振荡器和复位电路114的信号poff,以及

[0180]-存储电路118的信号iso和lconf。

[0181]

例如,如图9所示,寄存器接口1162可包括可经由处理单元102编程的以下配置数据中的一个或多个:

[0182]-一个或多个位mode,用于激活低功率模式并可选地选择要激活的低功率模式;

[0183]-一个或多个可选位wen,用于使能用于恢复正常工作模式的唤醒源;

[0184]-位gpioret,指示当激活低功率模式和退出低功率模式时,存储电路118是否应保持寄存器接口gpio的配置数据;

[0185]-可选位gpioretac,指示在恢复正常工作模式时电路118内的锁存器是否应该自动变得透明(通过设置信号lconf)。

[0186]

因此,在各种实施例中,控制电路1164可以被配置为监测位gpioret,并且在正常工作模式下,设置信号iso和lconf,以便例如通过将信号iso和lconf设置为高来提供寄存器接口gpio的配置位。

[0187]

相反,响应于确定配置数据模式指示低功率模式应该被激活,控制电路可以设置信号poff(例如,高)以便激活(所请求的)低功率模式,并且:

[0188]-在信号gpioret被设置的情况下,设置信号iso和lconf,以便保持配置位,并例如通过将信号iso和lconf设置为低来将锁存器l1-l3与接口gpio隔离。

[0189]

通常,在没有设置信号gpioret的情况下,处理系统10a可以被配置为执行其他操作。例如,在各种实施例中,在这种情况下,功率管理电路被配置为设置信号iso和lconf,以便例如通过将信号iso和lconf设置为高,使编程寄存器值从接口gpio传递到padx。然而,在这种情况下,功率管理电路设置信号poff以便仅关断第一子电路30的时钟信号clk,而电源电压vdd1保持接通。例如,此模式可用于调试目的。

[0190]

在各种实施例中,响应于使能的唤醒事件irq,控制电路1164可以设置信号poff(例如,低)以便激活正常工作模式。在这种情况下,控制电路1164还可以:

[0191]-在未设置信号gpioretac的情况下,设置信号iso和lconf,以便保持存储电路118中的配置位,例如,通过将信号iso设置为高且将信号lconf设置为低;或者

[0192]-在信号gpioretac被设置的情况下,例如通过将信号iso设置为高且将信号lconf设置为高来复位存储电路118,由此接口gpio的复位配置由锁存器l1-l3提供。

[0193]

现在将描述处理系统的可能操作。在处理系统启动(激活vin)之后,电源电路112a产生电源电压vdd1和vdd2。通常,在电压vdd1和vdd2对应于电压vin的情况下,电源电路112a也可以经由根据信号poff而驱动的一个或多个电子开关来实现。因此,振荡器和复位电路114被激活,并且产生复位信号rst,从而复位处理系统10a的子电路30。此外,振荡器和复位电路114产生时钟信号clk,由此处理单元102开始执行存储到程序存储器104的各个固件。

[0194]

通常,这样的固件包括用于配置各种焊盘pad1

…

padn,即,i/o接口130的软件指令。为此,固件通常包括用于编程寄存器接口gpio中的配置位的软件指令。

[0195]

此外,这样的固件可以包括用于例如通过编程寄存器接口1162中的配置数据、特别是数据模式来激活低功率模式的软件指令。

[0196]

具体地,在下文中将假定固件包括设置模式数据mode以便指示电源电压vdd1(以及可选地振荡器和复位电路114)应该关断的软件指令,这在下文中将被称为deepstop模式。通常,deepstop模式也可以是唯一支持的模式,并且可以通过设置单个模式位模式来激活deepstop模式。

[0197]

在各种实施例中,固件包括用于设置这些位中的一个或多个的一个或多个软件指令。因此,在下面将假定,在激活低功率模式之前,固件还编程位gpioret。

[0198]

响应于检测到应该激活deepstop模式(通过监测配置位模式),控制电路验证位gpioret,并确定应该存储i/o焊盘的配置数据。

[0199]

因此,在这种情况下,控制电路1164可以被配置为按顺序执行以下操作:

[0200]-设置信号lconf(例如,设置为低)以指示存储元件l1

…

l3应该保持配置数据;

[0201]-设置信号iso(例如,低),以断开寄存器接口gpio与元件l1

…

l3的连接;

[0202]-设置信号poff以便(经由电源电路112a)关断电源电压vdd1。

[0203]

通常,控制电路1164的顺序操作可以经由时序逻辑电路或通过使用包括一系列延迟元件的组合逻辑电路来实现。通常,功率管理电路116a也可以是响应时钟信号clk而操作的时序逻辑电路,时钟信号clk也可以被关断,因为信号poff的设置是最后的操作。

[0204]

此外,由于软件指令序列,操作序列也可以是隐式的,即,处理单元102可以首先编程位gpioret,由此控制电路1164设置信号lconf(例如,为低)以指示存储元件l1

…

l3应该保持配置数据,然后编程位模式,由此控制电路1164设置信号iso(例如,为低)以便断开寄存器接口gpio与元件l1

…

l3的连接。因此,信号lconf和iso可以根据信号gpioret和信号mode而被确定,至少一个或多个相应位指示低功率模式应该开始。例如,该位可以对应于cpu指令wfi(等待中断)。

[0205]

因此,响应于信号poff,电源电路112a切换电压vdd1的,并且可选地,振荡器和时钟电路114关闭时钟信号clk。然而,存储电路118仍然向i/o接口130提供配置数据。

[0206]

例如,如果固件已将寄存器gpioconf(给定焊盘padx的)设置为“01”,并将相应的位odr设置为“1”,则存储电路将提供存储值gpioconf'=“01”和odr'=“1”。因此,选择器电路1244和1262将分别向输出驱动器1300提供信号dout=“1”和oen'=“1”,并且相应的焊盘padx被设置为高,并且在deepstop模式下也将保持其值。在所考虑的实施例中,输入比较器

1302始终接通,由此信号din被设置为“1”,并且选择器电路1280将信号idr'设置为“1”。

[0207]

相反,在固件已将(给定焊盘padx的)寄存器gpioconf设置为“10”或“11”的情况下,选择器电路1244和1262将提供信号dout=p_out和oen'=p_oen,并且选择器电路1240和1260将:

[0208]-根据信号persel和可选地信号gpioconf来选择信号p1_out和p2_out中的一个作为信号p_out;

[0209]-根据信号persel和可选地信号gpioconf,来选择信号p1_oen和p2_oen中的一个作为信号p_oen。

[0210]

此外,选择器电路1280根据信号persel和可选地信号gpioconf将信号din转发给信号p1_in和p2_in中的一个。

[0211]

因此,在这种情况下,所选外围设备120或122可经由焊盘padx交换数据,例如,设置焊盘padx的逻辑值或读取焊盘padx的逻辑值。例如,为了交换数据,这样的外围设备可能需要时钟信号。因此,在各种实施例中,子电路32接收时钟信号,而提供给子电路30的时钟信号可能被关断。例如,为此目的,处理系统10a可包括:

[0212]-两个振荡器和复位电路114;

[0213]-振荡器和包括两个振荡器的复位电路114;或者

[0214]-振荡器和包括振荡器的复位电路114(振荡器优选地具有根据信号poff可设置的时钟频率),其中,时钟信号总是根据信号poff提供给子电路32,并且选择性地根据信号poff提供给子电路30。如前所述,在各种实施例中,时钟和复位电路114的操作可以经由模式数据模式来配置。

[0215]

一旦激活了低功率模式,功率管理电路116a就监测使能的唤醒信号。如前所述,为此目的,固件可以包括用于对配置数据wen进行编程的指令,该配置数据wen指示哪些唤醒源可以重新激活处理系统10a。

[0216]

因此,一旦功率管理电路116a检测到设定了给定的使能唤醒事件/信号irq,则控制电路1164可被配置为执行以下操作,这些操作可并行或按顺序执行:

[0217]-设置信号poff以便(经由电源电路112a)接通电源电压vdd1;

[0218]-设置信号iso(例如,高),以便将寄存器接口gpio连接到存储元件l1

…

l3。

[0219]

因此,在所考虑的实施例中,当恢复正常工作模式时,功率管理电路116a不改变信号lconf的逻辑电平。例如,为此目的,信号lconf可以对应于位gpioret的反转版本。通常,通过使用相反的逻辑电平,对于信号gpioret,信号lconf也可以对应于信号gpioret。

[0220]

因此,在所考虑的实施例中,寄存器接口gpio经由电源电压vdd1被供电,并且不包括保持触发器。因此,当激活deepstop模式时,相应的配置丢失。相反地,存储电路118和功率管理电路116a的寄存器1162在子电路32内,子电路32通过电源电压vdd2保持供电并且因此保持有效。

[0221]

因此,在各种实施例中,由处理单元102执行的固件包括用于重新编程寄存器接口gpio的指令,并且仅包括用于通过编程寄存器接口1162来改变位gpioret的逻辑电平的指令。

[0222]

例如,图3所示的处理电路10a具有处理单元102也不使用保持触发器的优点。

[0223]

例如,响应于恢复正常工作模式,振荡器和复位电路114可产生复位,由此执行处

理单元102的新启动。例如,响应于该重置,固件可以包括用于执行一个或多个任务的指令,例如从传感器读取数据并发送这样的数据,然后再次激活低功率模式。附加地或可选地,固件可包括用于确定已产生哪个中断irq以恢复正常工作模式的指令,然后根据所确定的中断执行一个或多个任务。

[0224]

在必须保持处理单元的给定处理状态的情况下,固件可包括用于将标识处理单元102的状态的数据存储到存储器的指令,该存储器被配置为在电源电压vdd1去激活时保持其配置。例如,为此目的,存储器可以是经由电源电压vdd2供电的可编程非易失性存储器,例如存储器104,或者易失性存储器,例如存储器100。因此,响应于当恢复正常工作模式时由电路114产生的复位,固件可以包括用于从存储器读取标识处理单元102的状态的数据的指令,然后根据读取的数据执行一个或多个任务。

[0225]

在各种实施例中,处理系统10a还可以经由软件指令(经由处理单元102执行的)或经由硬件功率管理电路116a配置为存储处理单元102的完整上下文。通常,术语“上下文(context)”是指处理单元102(在子电路30中)的寄存器的内容。事实上,如前所述,在各种实施例中,存储器100可经由电源电压vdd2供电,并因此保持其数据。因此,响应于恢复正常工作模式,处理系统10a(经由固件或经由硬件功率管理电路116a)可再次从存储器读取上下文。

[0226]

例如,恢复完整上下文还包括恢复寄存器接口gpio的配置。因此,在用户想要改变一个或多个焊盘的配置的情况下,将新的配置数据重新编程到寄存器接口gpio,然后改变配置数据gpioret的逻辑电平就足够了。

[0227]

相反,在所考虑的实施例中,在寄存器接口gpio的配置丢失并且用户希望改变i/o接口的配置的情况下,例如,为了改变焊盘的逻辑电平,固件必须包括用于向寄存器接口gpio提供给定焊盘padx的新配置和其他焊盘padx(保持不变)的配置数据的指令。

[0228]

如前所述,在各种实施例中,配置寄存器1162还可以包括位gpioretac。具体地,当该位被设置时,功率管理电路116a可被配置为在恢复正常工作模式时,例如,通过根据位gpioretac将信号lconf设置为高,使存储电路118透明。例如,在处理系统10a在deepstop期间或从deesptop中唤醒期间由于某些原因而被卡住,并且用户希望再次获得对一个或多个焊盘pad1

…

padn的动态控制,使锁存器再次透明并使用jtag或单线接口进行调试的情况下,该行为可能是有用的。

[0229]

因此,利用本文描述的配置,即使控制器gpio不包括保持触发器,处理系统也能够在低功率模式和退出低功率模式下处理一个或多个通用输入-输出而不丢失它们的配置。具体地,为此目的使用组合解决方案,其包括:

[0230]-存储电路118和功率管理电路116a;和

[0231]-软件指令,用于将配置存储到存储电路118,激活deepstop模式,并且响应于恢复正常工作模式,重新编程i/o配置并再次使存储元件电路118透明。

[0232]

因此,可以减少低功率模式中的功耗,并且可以避免保持触发器所需的面积量。此外,可以避免两个电源电压到这种保持触发器的复杂路由。事实上,在各种实施例中,寄存器接口gpio可以布置在微处理器102附近(甚至在微处理器102内),因此微处理器102可以是现有的集成电路布局,例如ip核,而子电路32可以作为附加的单独的集成电路布局提供。

[0233]

当然,在不影响本发明的原理的情况下,构造和实施例的细节可以相对于本文纯

粹通过示例方式描述和说明的内容有很大的变化,而不因此偏离由所附权利要求所定义的本发明的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。