1.各种实施例一般涉及用于校正振荡器的频率改变的显示驱动电路以及该显示驱动电路的频率校正方法。

背景技术:

2.随着信息化技术的发展,作为用户与信息之间的连接媒介的显示装置的市场不断扩大。因此,诸如有机发光显示器(oled)等的显示装置的使用已经越来越多。

3.显示装置可以包括显示面板和用于驱动显示面板的显示驱动电路。

4.通常,显示驱动电路可以根据扫描速率来操作,并且可以通过显示驱动电路中所包括的振荡器的时钟信号来维持扫描速率。

5.时钟信号的频率可能因环境因素(诸如振荡器的温度变化等)而改变。时钟信号的频率改变可能会导致显示装置中的图像质量劣化。

6.因此,为了快速提高图像质量,显示驱动电路应当定期检查并校正时钟信号的频率改变。

7.显示驱动电路可以从诸如应用处理器(ap)、中央处理单元(cpu)和图形处理单元(gpu)等的主机接收图像数据,并且可以从该主机接收用于在显示面板上显示该图像数据的垂直同步信号、水平同步信号和数据使能信号。

8.在常规技术中,显示驱动电路根据垂直同步信号的周期来校正时钟信号的频率改变。

9.近来,用于改变扫描速率的技术已经应用于显示装置,以降低显示装置的功耗。

10.例如,当显示装置显示运动图像时,扫描速率可以设置为60hz,并且当显示装置显示静止图像时,扫描速率可以改变为1hz或10hz。

11.如果显示装置的扫描速率改变为诸如1hz或10hz等的低扫描速率,则垂直同步信号的周期相应地增加。

12.如果垂直同步信号的周期增加,则在显示驱动电路中校正时钟信号的频率改变所需的时间也增加。因此,无法快速解决由时钟信号的频率改变所引起的图像质量劣化。

技术实现要素:

13.在这样的背景下,在一方面,各种实施例旨在提供一种用于在以低扫描速率驱动显示装置时快速校正时钟信号的频率改变的技术。

14.在一方面,实施例可以提供一种显示驱动电路,包括:振荡器,其被配置为生成振荡器时钟信号;时序控制器,其被配置为通过使用所述振荡器时钟信号来生成脉宽调制同步信号即pwm同步信号;以及频率校正电路,其被配置为通过使用所述pwm同步信号来设置用于测量和校正所述振荡器时钟信号的频率与目标频率之间的频率偏差的校正周期,生成用于基于所述校正周期来校正所述频率偏差的校正信号,并且将所述校正信号输出到所述振荡器。

15.在另一方面,实施例可以提供一种显示驱动电路中的振荡器的频率校正方法,所述方法包括:生成振荡器时钟信号;通过使用所述振荡器时钟信号来生成脉宽调制同步信号即pwm同步信号;以及通过使用所述pwm同步信号来校正所述振荡器时钟信号的频率。

16.从上述描述可以明显看出,根据实施例,显示驱动电路可以通过使用作为内部信号的pwm同步信号来校正振荡器时钟信号的频率改变,该pwm同步信号具有与从外部电路接收到的垂直同步信号相比更短的周期。因此,即使在以低扫描速率驱动显示装置时,也可以快速校正振荡器时钟信号的频率改变。

附图说明

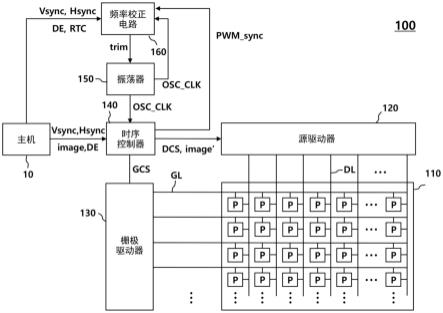

17.图1是根据实施例的显示装置的配置图。

18.图2和图3是用于辅助说明根据实施例的频率校正电路校正振荡器时钟信号的频率的配置的图。

19.图4是示出根据实施例的显示驱动电路校正振荡器时钟信号的处理的流程图。

具体实施方式

20.图1是根据实施例的显示装置的配置图。

21.参考图1,显示装置100可以包括显示面板110和用于驱动显示面板110的显示驱动电路。

22.多个数据线dl和多个栅极线gl可以布置在显示面板110中,并且多个像素p可以布置在显示面板110中。多个像素p可以布置成由多行和多列形成的矩阵形状。

23.用于驱动显示面板110的显示驱动电路可以包括源驱动器120、栅极驱动器130、时序控制器140、振荡器150和频率校正电路160。

24.在显示驱动电路中,栅极驱动器130可以将接通电压或断开电压的扫描信号输出到栅极线gl。在将接通电压的扫描信号供给到像素p时,相应像素p连接到数据线dl,并且在将断开电压的扫描信号供给到像素p时,相应像素p和数据线dl之间的连接被解除。

25.在显示驱动电路中,源驱动器120将数据电压供给到数据线dl。将供给至数据线dl的数据电压传送到根据扫描信号而连接到数据线dl的像素p。

26.在显示驱动电路中,时序控制器140可以从主机10接收垂直同步信号vsync、水平同步信号hsync、数据使能信号de和图像数据image。时序控制器140可以从振荡器150接收振荡器时钟信号osc_clk。垂直同步信号vsync可以是与高扫描速率相对应的垂直同步信号或与低扫描速率相对应的垂直同步信号。

27.换句话说,主机10可以改变显示装置100的扫描速率,并且可以根据显示装置100的扫描速率来调整垂直同步信号vsync的周期。扫描速率和垂直同步信号vsync的周期可以成比例关系。即,与高扫描速率相对应的垂直同步信号vsync的周期可以短于与低扫描速率相对应的垂直同步信号的周期。通常,高扫描速率可以是60hz(赫兹)或更大,并且低扫描速率可以是10hz或更小。

28.时序控制器140可以通过使用垂直同步信号vsync、水平同步信号hsync、数据使能信号de和振荡器时钟信号osc_clk来生成栅极驱动器130的控制信号和源驱动器120的控制信号。

29.首先,时序控制器140可以通过使用垂直同步信号vsync、水平同步信号hsync、数据使能信号de和振荡器时钟信号osc_clk来生成栅极控制信号gcs,并且可以将栅极控制信号gcs输出到栅极驱动器130。栅极控制信号gcs可以包括栅极启动脉冲(gsp)、栅极移位时钟(gsc)、栅极输出使能信号(goe)和栅极调制控制信号。

30.时序控制器140可以将从主机10接收到的图像数据image转换为图像数据image’,以匹配源驱动器120所使用的数据类型。

31.时序控制器140可以将转换后的图像数据image’输出到源驱动器120。

32.时序控制器140可以通过使用垂直同步信号vsync、水平同步信号hsync、数据使能信号de和振荡器时钟信号osc_clk来生成数据控制信号dcs,并且可以将该数据控制信号dcs输出到源驱动器120。

33.数据控制信号dcs可以包括源启动脉冲(ssp)、源移位时钟(ssc)和源输出使能信号(soe)。

34.在实施例中,时序控制器140可以生成脉宽调制(pwm)同步信号pwm_sync作为在调整布置在显示面板110中的像素p的发光时间和亮度其中至少之一时所使用的信号。

35.当栅极驱动器130具有用于调整像素p的发光时间和亮度的功能时,时序控制器140可以将pwm同步信号pwm_sync输出到栅极驱动器130。

36.当显示驱动电路包括用于调整像素p的发光时间和亮度的单独驱动器(未示出)时,时序控制器140可以将pwm同步信号pwm_sync输出到该单独驱动器。

37.时序控制器140可以将pwm同步信号pwm_sync输出到下面将描述的频率校正电路160。

38.pwm同步信号pwm_sync的周期可以短于垂直同步信号vsync的周期。

39.振荡器150可以生成振荡器时钟信号osc_clk,并且可以将该振荡器时钟信号osc_clk输出到时序控制器140和频率校正电路160。

40.振荡器150可以基于从频率校正电路160输出的校正信号trim来调整振荡器时钟信号osc_clk的频率。

41.频率校正电路160可以从振荡器150接收振荡器时钟信号osc_clk。

42.频率校正电路160可以从主机10接收垂直同步信号vsync、水平同步信号hsync、数据使能信号de和实时时钟(rtc)信号,并且可以从时序控制器140接收pwm同步信号pwm_sync。

43.频率校正电路160可以通过使用pwm同步信号pwm_sync来设置用于测量和校正目标频率与振荡器时钟信号osc_clk的频率之间的频率偏差的校正周期。

44.频率校正电路160可以生成用于基于校正周期来校正频率偏差的校正信号trim,并且可以将该校正信号trim输出到振荡器150。

45.对此的详细描述如下。

46.图2和图3是用于辅助说明根据实施例的频率校正电路校正振荡器时钟信号的频率的配置的图。

47.参考图2,频率校正电路160可以计算从时序控制器140接收到的pwm同步信号pwm_sync的周期t。

48.频率校正电路160可以将通过将pwm同步信号pwm_sync的周期t乘以等于或大于2

的自然数所计算出的值设置为校正周期。

49.例如,频率校正电路160可以将通过将pwm同步信号pwm_sync的周期t乘以4所计算出的4t设置为校正周期。

50.通过这样,频率校正电路160可以将pwm同步信号pwm_sync的周期t的每4倍识别为校正周期到达的时间点。

51.如上所述设置校正周期的频率校正电路160可以在每次校正周期到达时计算振荡器时钟信号osc_clk的频率,并且可以进行将预设目标频率与所计算出的频率进行比较的操作meas(参见图2)。

52.如图3所示,频率校正电路160可以对从主机10接收到的rtc信号的一个周期t期间的振荡器时钟信号osc_clk的波数进行累计,并且可以通过使用经累计的波数来计算振荡器时钟信号osc_clk的频率。

53.如图2所示,如果如上所述计算出的振荡器时钟信号osc_clk的频率与目标频率之间存在频率偏差,则频率校正电路160可以在至少两个校正周期中的各周期处(阶段1、阶段2和阶段3(参见图2))生成校正信号trim,并且可以将校正信号trim输出到振荡器150。校正信号可以包括用于根据频率偏差来增加或减少振荡器时钟信号osc_clk的频率的代码。

54.在实施例中,当垂直同步信号vsync是与低扫描速率相对应的垂直同步信号时,如图2所示,频率校正电路160可以在垂直同步信号vsync的一个周期期间至少两次生成校正信号trim。换句话说,由于频率校正电路160可以在一帧的垂直消隐间隔期间校正振荡器时钟信号osc_clk的频率,因此在下一帧中振荡器时钟信号osc_clk的频率可以是稳定的。稳定可以是指振荡器时钟信号osc_clk的频率与目标频率之间的频率偏差为零或低于预定基准的状态。

55.在实施例中,频率校正电路160可以检查从主机10接收到的数据使能信号de的电平,并且当数据使能信号de处于低电平时,在校正周期到达的情况下可以生成校正信号trim。

56.在校正周期在数据使能信号de处于高电平时到达的情况下,频率校正电路160可以跳过校正信号trim的生成(参见图2的点线圆)。

57.换句话说,在校正周期在显示驱动电路将一帧的图像数据输出到显示面板110的帧有效间隔期间到达时,频率校正电路160可以跳过校正信号trim的生成,以实现显示驱动电路的稳定操作。

58.如从以上描述明显看出,显示驱动电路可以通过使用作为内部信号的pwm同步信号pwm_sync来校正振荡器时钟信号osc_clk的频率改变,该pwm同步信号pwm_sync具有与从外部电路接收到的垂直同步信号vsync相比更短的周期。因此,即使在以低扫描速率驱动显示装置100时,也可以快速校正振荡器时钟信号osc_clk的频率改变。

59.在下文中,将描述用于通过使用显示驱动电路来校正振荡器时钟信号osc_clk的频率的处理。

60.图4是示出根据实施例的显示驱动电路校正振荡器时钟信号的处理的流程图。

61.包括源驱动器120、栅极驱动器130、时序控制器140、振荡器150和频率校正电路160的显示驱动电路可以生成振荡器时钟信号(s410)。在步骤s410处,显示驱动电路可以从主机10接收垂直同步信号、水平同步信号、数据使能信号和rtc信号。

62.显示驱动电路可以通过使用振荡器时钟信号来生成pwm同步信号(s420),并且可以通过使用pwm同步信号来校正振荡器时钟信号的频率(s430)。

63.在步骤s420处,显示驱动电路可以通过使用垂直同步信号、水平同步信号和数据使能信号其中至少之一来生成pwm同步信号。

64.在步骤s430处,显示驱动电路可以通过将pwm同步信号的周期乘以等于或大于2的自然数来计算校正周期,并且可以根据该校正周期来校正振荡器时钟信号的频率。

65.具体而言,在步骤s430处,当校正周期到达时,显示驱动电路可以对从主机10接收到的rtc信号的一个周期期间的振荡器时钟信号的波数进行累计。

66.显示驱动电路可以通过使用经累计的波数来计算振荡器时钟信号的频率,并且可以计算振荡器时钟信号的频率与预设目标频率之间的频率偏差。

67.显示驱动电路可以计算一个校正周期期间的频率偏差。当校正周期再次到达时,显示驱动电路可以通过根据该频率偏差增加或减少振荡器时钟信号的频率来生成振荡器时钟信号。然后,显示驱动电路可以再次计算振荡器时钟信号的频率与目标频率之间的频率偏差。

68.显示驱动电路可以在至少两个校正周期中的各周期处重复进行用于在增加或减少振荡器时钟信号的频率之后再次计算频率偏差的处理。通过这样,显示驱动电路可以完美地校正振荡器时钟信号的频率与目标频率之间的频率偏差。

69.在校正周期在校正了频率偏差之后到达时,显示驱动电路可以计算振荡器时钟信号的频率,并且进行将预设目标频率与所计算出的频率进行比较的操作meas(参见图2)。

70.另一方面,在步骤s430处,显示驱动电路可以识别数据使能信号的电平。在校正周期在数据使能信号的电平低时到达的情况下,显示驱动电路可以生成校正信号。在校正周期在数据使能信号的电平高时到达的情况下,显示驱动电路可以跳过校正信号的生成(在图2中用点线圆来标记)。

71.相关申请的交叉引用

72.本技术要求于2020年12月18日提交的韩国专利申请10-2020-0179027的优先权,如同在这里全部阐述一样,其通过引用而被包含于此以用于所有目的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。