1.本实用新型涉及计算机技术领域,尤其涉及一种计算机主板、双路处理器计算机及四路处理器计算机。

背景技术:

2.目前多路服务器系统由于其高扩展,高性能,高可靠性的特点,大规模的应用于商业智能,大规模虚拟化,企业关键业务等场景。在多路服务器的实现过程中,通常会通过设计多路处理器的专用主板来实现,即,在主板上设计多个处理器基座,多个处理器基座之间进行通信连接来实现多路处理器的应用。但是,这种设计方式中,当主板出现一个器件失效而无法修复,就需要更换整块多路服务器主板,造成硬件运维成本大,同时,该设计方式仅能适用于与主板匹配的处理器数量的多路处理器,配置方式不够灵活。

技术实现要素:

3.本实用新型提供的计算机主板、双路处理器计算机及四路处理器计算机,在主板上对第一处理器互连接口进行通信连接,预留第二处理器互连接口和第三处理器互连接口,从而,能够通过第二处理器互连接口和第三处理器互连接口灵活的配置为所需数量的多路处理器。

4.第一方面,本实用新型提供一种计算机主板,包括:

5.两个处理器基座,每个处理器基座具有第一处理器互连接口、第二处理器互连接口和第三处理器互连接口,其中一个处理器基座的第一处理器互连接口与另一个处理器基座的第一处理器互连接口通信连接;

6.第一对外通信接口,与其中一个处理器基座的第二处理器互连接口通信连接;

7.第二对外通信接口,与另一个处理器基座的第二处理器互连接口通信连接;

8.第三对外通信接口,与其中一个处理器基座的第三处理器互连接口通信连接;

9.第四对外通信接口,与另一个处理器基座的第三处理器互连接口通信连接。

10.第二方面,本实用新型提供一种双路处理器计算机,包括上述的计算机主板,其中,所述第一对外通信接口与所述第二对外通信接口通过通信线缆通信连接。

11.第三方面,本实用新型提供一种四路处理器计算机,包括两个上述的计算机主板,其中一个主板的第一对外通信接口与另一个主板的第一对外通信接口采用通信线缆通信连接,其中一个主板的第二对外通信接口与另一个主板的第二对外通信接口采用通信线缆通信连接,其中一个主板的第三对外通信接口与另外一个主板的第四对外通信接口采用通信线缆通信连接,其中一个主板的第四对外通信接口与另外一个主板的第三对外通信接口采用通信线缆通信连接。

12.可选地,所述主板还具有边带信号接口,所述两个主板的边带信号接口通信连接。

13.可选地,所述主板还包括:

14.基板管理控制芯片bmc;

15.复杂可编程逻辑芯片cpld,与所述基板管理控制芯片通信连接,所述复杂可编程逻辑芯片与所述边带信号接口通信连接。

16.可选地,所述边带信号接口包括集成电路总线i2c接口,两个所述主板的bmc通过i2c总线通信连接形成主从连接,两个所述主板的cpld通过i2c总线通信连接;同一主板上的bmc和cpld通过i2c总线通信连接。

17.可选地,所述主板还包括:

18.电源开关,用于发出开机信号,所述电源开关与所述cpld通信连接,以使所述cpld在接收到开机信号后控制主板上电。

19.可选地,所述主板还包括:

20.时钟发生器,所述时钟发生器与所述边带信号接口通信连接;

21.数据选择器,所述数据选择器与所述边带信号接口和所述时钟发生器通信连接,所述数据选择器用于选择边带信号接口和所述时钟发生器的时钟信号。

22.可选地,所述主板还包括温度传感器,所述温度传感器与所述cpld和bmc通过i2c总线通信连接。

23.可选地,所述主从连接中的主机bmc通过简化媒体独立接口和吉比特介质独立接口与交换机通信连接,所述主从连接中的从机bmc通过吉比特介质独立接口与交换机通信连接。

24.在本实用新型实施例中提供的技术方案中,在主板上对处理器基座的第一处理器互连接口进行通信连接,并预留第二处理器互连接口和第三处理器互连接口,在主板的使用过程中,可以通过预留的第二处理器互连接口和第三处理器互连接口与同主板的处理器基座或者不同主板的处理器基座通过通信线缆进行通信连接。通过通信线缆的连接,将同一主板上或者不同主板上安装的处理器连接形成不同的拓扑结构,从而,能够实现对处理器数量的灵活配置。同时,由于本实用新型中的主板上设置的处理器数量较少,单个主板能够单独使用,也能够单独更换,从而,降低了硬件的运维成本。

附图说明

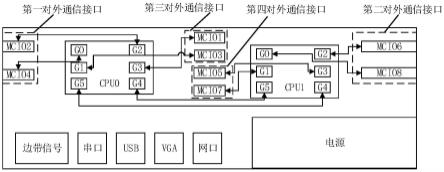

25.图1为本实用新型一实施例计算机主板的示意图;

26.图2为本实用新型另一实施例双路处理器计算机的示意图;

27.图3为本实用新型另一实施例四路处理器计算机的示意图;

28.图4为本实用新型另一实施例四路处理器计算机的bmc连接方式;

29.图5为本实用新型另一实施例四路处理器计算机电源按钮与cpld的拓扑结构;

30.图6为本实用新型另一实施例四路处理器计算机的cpld的拓扑结构;

31.图7为本实用新型另一实施例四路处理器计算机的cpld控制上电的时序图;

32.图8为本实用新型另一实施例四路处理器计算机节点识别示意图;

33.图9为本实用新型另一实施例四路处理器计算机的时钟信号传输示意图。

具体实施方式

34.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描

述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

35.本实用新型实施例提供一种计算机主板,如图1所示,包括:

36.两个处理器基座,每个处理器基座具有第一处理器互连接口、第二处理器互连接口和第三处理器互连接口,其中一个处理器基座的第一处理器互连接口与另一个处理器基座的第一处理器互连接口通信连接;在一些实施例中,处理器基座的第一处理器互连接口、第二处理器互连接口与第三处理器互连接口例如可以为芯片间高速内存接口xhmi接口。如图1所示,以处理器基座的g5和g4接口作为第一处理器互连接口,以处理器基座的g0和g2为第二处理器互连接口,以处理器基座的g1和g3作为第三处理器互连接口。其中,两个处理器的第一处理器互连接口之间通过印刷的线路进行通信连接,以实现固定的通信连接方式。

37.第一对外通信接口,与其中一个处理器基座的第二处理器互连接口通信连接;在一些实施例中,第一对外通信接口设置在基板上的通信接口,第一对外通信接口通过印刷的线路与cpu0对应的处理器基座的第二处理器互连接口通信连接,第一对外通信接口例如可以为迷你高密度、高速度卡缘连接器mcio接口。如图1所示,在主板上,将mcio2和mcio4视为第一对外通信接口。

38.第二对外通信接口,与另一个处理器基座的第二处理器互连接口通信连接;在一些实施例中,第二对外通信接口设置在基板上的通信接口,第二对外通信接口通过印刷的线路与cpu1对应的处理器基座的第二处理器互连接口通信连接,第一对外通信接口例如可以为迷你高密度、高速度卡缘连接器mcio接口。如图1所示,在主板上,将mcio6和mcio8视为第二对外通信接口。

39.第三对外通信接口,与其中一个处理器基座的第三处理器互连接口通信连接;在一些实施例中,第三对外通信接口设置在基板上的通信接口,第三对外通信接口通过印刷的线路与cpu0对应的处理器基座的第三处理器互连接口通信连接,第三对外通信接口例如可以为迷你高密度、高速度卡缘连接器mcio接口。如图1所示,在主板上,将mcio1和mcio3视为第三对外通信接口。

40.第四对外通信接口,与另一个处理器基座的第三处理器互连接口通信连接。在一些实施例中,第四对外通信接口设置在基板上的通信接口,第四对外通信接口通过印刷的线路与cpu1对应的处理器基座的第三处理器互连接口通信连接,第四对外通信接口例如可以为mcio接口。如图1所示,在主板上,将mcio5和mcio7视为第四对外通信接口。

41.在本实用新型实施例中提供的技术方案中,在主板上对处理器基座的第一处理器互连接口进行通信连接,并预留第二处理器互连接口和第三处理器互连接口,在主板的使用过程中,可以通过预留的第二处理器互连接口和第三处理器互连接口与同主板的处理器基座或者不同主板的处理器基座通过通信线缆进行通信连接。通过通信线缆的连接,将同一主板上或者不同主板上安装的处理器连接形成不同的拓扑结构,从而,能够实现对处理器数量的灵活配置。同时,由于本实用新型中的主板上设置的处理器数量较少,单个主板能够单独使用,也能够单独更换,从而,降低了硬件的运维成本。

42.本实用新型实施例还提供一种双路处理器计算机,如图2所示,包括上述的计算机主板,其中,所述第一对外通信接口与所述第二对外通信接口通过通信线缆通信连接。在一

些实施例中,当上述的计算机主板单独进行使用时,在两个cpu基座上安装两个cpu,随后,将第一对外通信接口和第二对外通信接口进行通信连接,从而,使两个处理器形成双路处理器的拓扑结构。而第三对外通信接口和第四对外通信接口则空余备用。

43.在本实用新型实施例中提供的技术方案中,在主板上对处理器基座的第一处理器互连接口进行通信连接,并预留第二处理器互连接口和第三处理器互连接口,在主板的使用过程中,可以通过预留的第二处理器互连接口和第三处理器互连接口与同主板的处理器基座或者不同主板的处理器基座通过通信线缆进行通信连接。通过通信线缆的连接,将同一主板上或者不同主板上安装的处理器连接形成不同的拓扑结构,从而,能够实现对处理器数量的灵活配置。同时,由于本实用新型中的主板上设置的处理器数量较少,单个主板能够单独使用,也能够单独更换,从而,降低了硬件的运维成本。

44.本实用新型提供一种四路处理器计算机,如图3所示,包括两个上述的计算机主板,其中一个主板的第一对外通信接口与另一个主板的第一对外通信接口采用通信线缆通信连接,其中一个主板的第二对外通信接口与另一个主板的第二对外通信接口采用通信线缆通信连接,其中一个主板的第三对外通信接口与另外一个主板的第四对外通信接口采用通信线缆通信连接,其中一个主板的第四对外通信接口与另外一个主板的第三对外通信接口采用通信线缆通信连接。在一些实施例中,按照这种连接方式,将对外通信接口采用线缆进行通信连接,能够使任何一个cpu与其他三个cpu之间都形成通信连接,从而,能够通过上述的连接方式采用两块主板形成四路处理器。

45.在本实用新型实施例中提供的技术方案中,在主板上对处理器基座的第一处理器互连接口进行通信连接,并预留第二处理器互连接口和第三处理器互连接口,在主板的使用过程中,可以通过预留的第二处理器互连接口和第三处理器互连接口与同主板的处理器基座或者不同主板的处理器基座通过通信线缆进行通信连接。通过通信线缆的连接,将同一主板上或者不同主板上安装的处理器连接形成不同的拓扑结构,从而,能够实现对处理器数量的灵活配置。同时,由于本实用新型中的主板上设置的处理器数量较少,单个主板能够单独使用,也能够单独更换,从而,降低了硬件的运维成本。

46.作为一种可选的实施方式,所述主板还具有边带信号接口,所述两个主板的边带信号接口通信连接。为了实现两个主板上的外围设备的统一管理,在本实施方式中,还在主板上设置边带信号接口,并将两个主板的边带信号接口通信连接,以便于实现对两个主板上的外围设备的统一管理。

47.作为一种可选的实施方式,如图4所示,所述主板还包括:

48.基板管理控制芯片bmc;在一些实施例中,bmc是一个独立的管理系统,它不依赖于cpu或内存等硬件来实现对外围设备的监视和控制功能,操作的对象是系统硬件。比如通过监视温度、电压、风扇、电源等等参数,对对应的硬件做相应的调节工作,以保证系统处于健康的状态。同时平台管理还负责记录各种硬件的信息和日志记录,用于提示用户和后续问题的定位。

49.复杂可编程逻辑芯片cpld,与所述基板管理控制芯片通信连接,所述复杂可编程逻辑芯片与所述边带信号接口通信连接。在一些实施例中,复杂可编程逻辑器件与基板管理控制芯片通信连接,并将两个主板的复杂可编程逻辑芯片通过边带信号接口进行通信连接,从而,能够通过其中一个主板的bmc来实现对两个cpld的控制。

50.在本实施方式中,通过基板管理控制芯片和复杂可编程逻辑芯片的通信连接,以及两个复杂可编程逻辑芯片的通信连接,能够实现对两个主板的统一管理和控制。

51.作为一种可选的实施方式,如图4所示,所述边带信号接口包括集成电路总线i2c接口,两个所述主板的bmc通过i2c总线通信连接形成主从连接,两个所述主板的cpld通过i2c总线通信连接;同一主板上的bmc和cpld通过i2c总线通信连接。在一些实施例中,为了实现对两个主板的bmc的统一管理,bmc之间通过i2c接口进行主从通信,主机远程可以通过交换机访问主机bmc之后,可以通过主机bmc i2c轮询读回来的从机bmc地址,进行从机的bmc管理。主机bmc的i2c通过主从cpld级联访问从机的i2c设备。

52.作为一种可选的实施方式,如图5-图8所示,所述主板还包括:

53.电源开关,用于发出开机信号,所述电源开关与所述cpld通信连接,以使所述cpld在接收到开机信号后控制主板上电。在一些实施例中,两个主板的电源按钮的联锁方式以及主从连接方式如图5所示。如图6所示,两个主板的cpld的拓扑中,主机的cpld便可以通过模拟sgpio总线模块的接口扩展通用输入输出接口cpld gpio的功能,sgpio内部传送数据主要包括各个节点各个电源正常的信号,cpu杂线信号cpu misc信号,例如电源层控制挂起到内存信号slp_s3,电源层控制软关机信号slp_s5,cpu的极限温度信号thermaltrip等。以上述的联锁方式以及拓扑方式进行连接后,在为两个主板连接电源之后,上电时序由电源芯片按照图7所示的时序图逐级推动,直至各节点cpld判断s5下的电源正常后输出待机电压信号rsmrst#。在电源开关发出开机信号后,例如当人为按下电源按钮或远程发送开机指令pwrbtn信号时,开机信号经过主从节点的cpld去抖处理后,按图7所示的电源时序正常上电,从机cpld通过sgpio通信模块将各电源ok的信号传送给主机cpld,主机cpld判断所有节点电源正常上电后,例如,如图7所示cpu电源电压识别信号vid正常发出且被电源控制器解析调制电压时,便会释放主从机的复位信号reset_l进入基本输入输出系统自检bios post。下电模式同样由主机cpld控制发出,同时检测从机cpld情况,这里不再赘述。在前述的边带信号接口通信连接之后,需要确定哪一个是主机,哪一个是从机,如图8所示,通过边带管理信号线缆内部是否下拉决定哪一个是主机,哪一个是从机,例如,通过线缆内部参数配置设定主从机,当id1和id2内部全部下拉的一端,例如#1为主机,则另一端例如#2为从机。在一些优选的实施方式中,在对线缆内部的参数进行设定时,可以通过在节点机台上设置开关按钮或者设置触控显示界面来实现。其中,节点机台是指安装有前述的计算机主板、双路处理器计算机或者四路处理器计算机的机台。

54.作为一种可选的实施方式,如图9所示,所述主板还包括:

55.时钟发生器clk_gen,所述时钟发生器与所述边带信号接口通信连接;时钟发生器产生时钟信号,用于向主板上的外围设备提供时钟信号。时钟发生器具有两个输出接口,其中一个输出接口输出时钟发生器对内输出信号clk_gen_in,clk_gen_in能输入至数据选择器mux;另一个输出接口输出时钟发生器对外输出信号clk_gen_out,clk_gen_out能输出至边带管理接口。时钟发生器还具有使能接口,用于接收时钟发生器使能信号gen_en。

56.数据选择器mux,所述数据选择器与所述边带信号接口和所述时钟发生器通信连接,所述数据选择器用于选择边带信号接口和所述时钟发生器的时钟信号。数据选择器用来对输入的信号进行选择,例如,主板通过边带信号接口接收另一个主板的时钟发生器对外输出信号clk_gen_out并作为数据选择器的时钟输入信号clk_in传输给数据选择器,数

据选择器还会接收当前主板的时钟发生器发出的时钟信号,数据选择器依据节点身份设置信号node id sel对两个时钟信号进行选择后生成内部时钟信号intenrnal clk。例如,主机的时钟发生器向从机发送时钟信号,从机的时钟发生器也产生时钟信号,为了使两个主板的时序信号一致,数据选择器选择主机发送的时钟信号作为当前主板的时钟信号进行使用。

57.在本实施方式中,设计了两个主板间的时钟传输方式,以及主板内对时钟信号的选择方式,从而,能够灵活的调整主板的时钟信号的使用方式,使主机和从机能够相互调换,便于对不同设备的时钟同源管理。

58.作为一种可选的实施方式,所述主板还包括温度传感器,所述温度传感器与所述cpld和bmc通过i2c总线通信连接。在一些实施例中,温度是主板工作过程中的关键参数,因此,需要对温度参数进行实时的监控,在一些实施例中,主机bmc可以通过主机cpld向从机cpld发送i2c轮询读取命令,以便于获取从机主板上的温度参数。

59.作为一种可选的实施方式,所述主从连接中的主机bmc通过简化媒体独立接口rmii和吉比特介质独立接口rgmii与交换机通信连接,所述主从连接中的从机bmc通过吉比特介质独立接口与交换机通信连接。在一些实施例中,如4所示,交换机通过简化媒体独立接口获取主机bmc的ip,随后,通过ip地址访问主机bmc,再通过bmc的i2c访问,获取从机bmc的ip地址,再通过从机bmc的ip地址访问从机bmc。

60.在上述的各个实施方式中,同一个主板不同接口之间的通信连接,以及不同主板对应接口之间的通信连接,除采用现有的线缆进行通信连接,还可以通过设计集成线缆来降低外围线缆的安装复杂度,例如,可以采用印刷电路板的形式来形成集成线缆。

61.以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。