1.本发明属于数字抗干扰天线系统数据校准领域,具体涉及一种基于多信道抗干扰天线信号处理的装置、系统及方法。

背景技术:

2.多通道数字抗干扰天线系统通常由天线阵列、滤波器、放大器、变频器、模数变换和信号处理等核心部件组成。这些非理想元件和模块会造成多种误差,这些误差叠加后将会对天线系统造成极大的影响,会导致天线主波束的偏移,降低系统的抗电子干扰能力,影响天线系统输出信噪比,甚至引起系统输出信噪比的严重损失。对于多信道数字抗干扰天线系统来说,误差会直接导致天线主波束的偏移,因此为了能够应付更加复杂的环境,需要提高天线系统自身的抗干扰能力。

技术实现要素:

3.针对现有技术中的上述不足,本发明提供的一种基于多信道抗干扰天线信号处理的装置、系统及方法,解决了传统天线的抗干扰能力差的问题等。

4.为了达到上述发明目的,本发明采用的技术方案为:一种基于多信道抗干扰天线信号处理装置,包括信号处理模块、aiu组件、tr组件和电源模块;

5.其中,所述信号处理模块分别与所述aiu组件和电源模块连接,所述tr组件与所述信号处理模块连接。

6.进一步地:所述信号处理模块包括fpga芯片、flash芯片、eeprom芯片、adc芯片和dac芯片;

7.其中,所述fpga芯片分别与所述flash芯片、eeprom芯片、adc芯片、dac芯片连接;所述adc芯片和dac芯片均与所述aiu组件连接。

8.上述进一步方案的有益效果为:信号处理模块可以对输入的子阵级数据进行抗干扰处理。

9.进一步地:所述fpga芯片包括ram子模块、协方差矩阵计算子模块和滤波子模块;所述ram子模块、协方差矩阵计算子模块和滤波子模块依次连接。

10.上述进一步方案的有益效果为:fpga内部可以实现多通道信号间的信号相位校准。

11.进一步地:所述aiu组件设置有相控阵,其包括160个阵元。

12.上述进一步方案的有益效果为:阵元可以接收信号,并发送给子阵进行合成,提高输入信号的信噪比。

13.进一步地:所述fpga芯片包括调制解调子模块,调制解调子模块用于提取跳频频点信息。

14.一种基于多信道抗干扰天线信号处理的系统,包括如上所述的装置,且所述ram子模块与所述adc芯片连接,所述滤波子模块与所述dac芯片连接;所述aiu组件接收天线发送

的阵元数据,并将其通过adc芯片发送至fpga芯片,fpga芯片从阵元数据中提取子阵输入数据,所述fpga芯片根据子阵输入数据的阵元位置计算出阵元方向向量的相位,并将其发送至ram子模块;所述tr组件接收天线的中频信号,将其发送至调制解调子模块提取跳频频点信息,所述调制解调子模块将跳频频点信息发送至fpga芯片,fpga芯片根据跳频频点信息将子阵输入数据进行幅相校正,得到子阵级数据,将子阵级数据发送至协方差矩阵计算子模块,所述协方差矩阵计算子模块输出协方差矩阵,当协方差矩阵计算子模块输出完成后,根据smi算法得到协方差矩阵的逆矩阵,并根据ram子模块存储的阵元方向向量的相位计算出带约束指向的抗干扰的最优权值,将抗干扰的最优权值发送至滤波子模块,所述滤波子模块对输入的子阵级数据进行滤波,并将滤波后的子阵级数据发送至dac芯片,dac芯片进行模数转换得到天线抗干扰数据,并将天线抗干扰数据通过aiu组件发射出去,完成整个系统的天线信号抗干扰处理。

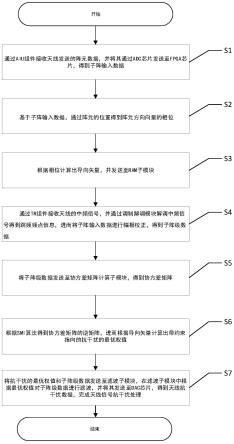

15.一种基于多信道抗干扰天线信号处理方法,包括以下步骤:

16.s1、通过aiu组件接收天线发送的阵元数据,并将其通过adc芯片发送至fpga芯片,得到子阵输入数据;

17.s2、基于子阵输入数据,通过阵元的位置得到阵元方向向量的相位

18.s3、根据相位计算出导向矢量,并发送至ram子模块;

19.s4、通过tr组件接收天线的中频信号,并通过调制解调子模块解调中频信号得到跳频频点信息,进而将子阵输入数据进行幅相校正,得到子阵级数据;

20.s5、将子阵级数据发送至协方差矩阵计算子模块,得到协方差矩阵;

21.s6、根据smi算法(矩阵求逆算法)得到协方差矩阵的逆矩阵,进而根据导向矢量计算出带约束指向的抗干扰的最优权值;

22.s7、将抗干扰的最优权值和子阵级数据发送至滤波子模块,在滤波子模块中根据最优权值对子阵级数据进行滤波,并将其发送至dac芯片,得到天线抗干扰数据,完成天线信号抗干扰处理。

23.进一步地:所述步骤s2中,阵元方向向量的相位的表达式具体为:

[0024][0025]

其中,λ为中心频点对应的波长,θ为阵元方向向量的水平方位角,为阵元方向向量的竖直俯仰角,xm、ym和zm均为阵元m的坐标值(xm,ym,zm),其中m为阵元的序数,m=0,1,

…

,m-1,m-1为阵元总数。

[0026]

上述进一步方案的有益效果为:通过阵元的位置获取的阵元方向向量相位的准确度高。

[0027]

进一步地:所述步骤s3中,导向矢量的表达式具体为:

[0028][0029]

上述进一步方案的有益效果为:通过计算所有阵元方向向量相位得到导向矢量,可用于确定最优权值。

[0030]

进一步地:所述步骤s6中,带约束指向的抗干扰的最优权值w

opt

的表达式具体为:

[0031][0032]

式中,为导向矢量,为协方差矩阵的逆;

[0033]

其中,协方差矩阵r

x

=e[x(t)xh(t)],x(t)为子阵级数据,xh(t)为子阵级数据采样系统,e[

·

]为期望函数。

[0034]

上述进一步方案的有益效果为:抗干扰的最优权值输入滤波子模块,可以完成子阵级数据的滤波,从而在期望信号方向形成增益,干扰方向形成零陷,达到抗干扰的目的。

[0035]

本发明的有益效果为:

[0036]

(1)本发明可以在实现对信号的接收的基础上,有效提高在目标方向上的信号增益,同时能够实现对干扰信号的抑制,该抗干扰采用基于smi算法实现带约束抗干扰算法和基于目标信号方向子阵合成方式的子阵降维抗干扰处理方式,使硬件上可实现的同时又能保证天线的有效增益,对接收目标信号带来有效的增益,从而保证系统的通信。

[0037]

(2)基于目标信号方向子阵合成方式使得基于子阵抗干扰处理后带波束约束的问题变得简单,减少硬件资源上的处理压力。

[0038]

(3)基于smi算法实现带约束的抗干扰算法突破了矩阵求逆工程的不可实现性,从而使得基于抗干扰算法的抗干扰性能达到理论仿真的水平,使得工程计算结果和理论计算结果一致。

附图说明

[0039]

图1为一种基于多信道抗干扰天线信号处理装置的系统结构框图;

[0040]

图2为一种基于多信道抗干扰天线信号处理装置的电源模块框图;

[0041]

图3为一种基于多信道抗干扰天线信号处理方法的流程图;

具体实施方式

[0042]

下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

[0043]

本说明书中所有实施例公开的所有特征,或隐含公开的所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以以任何方式组合和/或扩展、替换。

[0044]

如图1所示,在本发明的一个实施例中,一种基于多信道抗干扰天线信号处理的装置,包括信号处理模块、aiu组件、tr组件和电源模块;

[0045]

其中,所述信号处理模块分别与所述aiu组件和电源模块连接,所述tr组件与所述信号处理模块连接。

[0046]

tr组件用于接收天线产生的中频信号,aiu组件用于接收天线产生的阵元数据;信号处理模块用于提取aiu组件中的子阵输入数据,并对子阵输入数据进行幅相校正和滤波处理。

[0047]

所述信号处理模块包括fpga芯片、flash芯片、eeprom芯片、adc芯片和dac芯片;

[0048]

其中,所述fpga芯片分别与所述flash芯片、eeprom芯片、adc芯片、dac芯片连接;所述adc芯片和dac芯片均与所述aiu组件连接。

[0049]

fpga芯片是信号处理模块的主处理芯片,flash芯片用于存储软件代码,eeprom芯片用于存储抗干扰校准数据天线补相数据等数据,adc芯片用于实现不多于8路中频信号的数模转换,dac芯片用于实现中频信号的模数转换。

[0050]

在本实施例中,adc芯片的型号为gk3128,该芯片是一款采用速率250msps的14bits四通道的模数转换芯片,fpga芯片的型号为jfm7vx690t20,dac芯片的型号为sda9736amg;

[0051]

所述fpga芯片包括ram子模块、协方差矩阵计算子模块、调制解调子模块和滤波子模块;所述ram子模块、协方差矩阵计算子模块和滤波子模块依次连接。调制解调子模块用于提取跳频频点信息。

[0052]

其中,所述ram子模块还与所述adc芯片连接,所述滤波子模块还与所述dac芯片连接。

[0053]

所述aiu组件设置有相控阵,其包括160个阵元。

[0054]

在本实施例中,系统设置有串口通信模块,其包括相互连接的rs485通信接口和rs-485收发器芯片,rs-485收发器芯片的型号为sm3490。

[0055]

相控阵上的160个阵元用于接收信号,经过相控阵上的子阵合成提高输入信号的信噪比,在子阵级数据上进行干扰抑制,并在期望信号方向形成波束。

[0056]

fpga芯片接收到aiu组件传过来的阵元数据,经过波束处理,形成子阵级数据,子阵级数据经过ad量化后发送给fpga芯片,fpga芯片完成干扰抑制后,将数据传给调制解调子模块,完成整个设备的通信功能。

[0057]

在本实施例中,电源模块可以为信号处理模块提供稳定的电源,如图2所示,系统提供数字8v电源输入,在信号处理装置中将其分成三路两路。一路送给dc/dc模块hce4630ml将其转换成d1.0v,待d1.0v_pg使能后驱动第二片dc/dc模块sm4644mpy的d1.5v使能输入引脚;同样,待d1.8v_pg使能后驱动第三片dc/dc模块sm4644mpy的d2.5v使能输入引脚,直至d5.0v电源输出。

[0058]

在数字d2.5v输出后再通过ldo芯片sm74401进一步转换成a1.8v,作为sda9736的模拟1.8v供电电源。另一路d3.3v送给ldo芯片sm74401转换成a1.9v,作为gk3128模拟1.9v的供电电源。d5.0v送给ldo芯片sm74401转换成a3.3v作为sda9736的模拟3.3v供电电源。

[0059]

其中d1.0v作为fpga数字1.0v的供电电源,d1.5v和d1.8v作为fpga和gk3128数字1.8v供电电源,d5.0v作为对外接口电路电源。

[0060]

本发明实施例系统的工作过程为:本发明实施例的aiu组件接收天线发送的阵元数据,并将其通过adc芯片发送至fpga芯片,fpga芯片从阵元数据中提取子阵输入数据,fpga芯片根据子阵输入数据的阵元位置计算出阵元方向向量的相位,并将其发送至ram子模块;tr组件接收天线的中频信号,将其发送至调制解调子模块提取跳频频点信息,调制解调子模块将跳频频点信息发送至fpga芯片,fpga芯片根据跳频频点信息将子阵输入数据进行幅相校正,得到子阵级数据,将子阵级数据发送至协方差矩阵计算子模块,协方差矩阵计算子模块输出协方差矩阵,当协方差矩阵计算子模块输出完成后,根据smi算法得到协方差矩阵的逆矩阵,并根据ram子模块存储的阵元方向向量的相位计算出带约束指向的抗干扰

的最优权值,将抗干扰的最优权值发送至滤波子模块,滤波子模块对输入的子阵级数据进行滤波,并将滤波后的子阵级数据发送至dac芯片,dac芯片进行模数转换得到天线抗干扰数据,并将天线抗干扰数据通过aiu组件发射出去,完成整个系统的天线信号抗干扰处理。

[0061]

在本发明的实施例中,如图3所示,一种基于多信道抗干扰天线信号处理方法,包括以下步骤:

[0062]

s1、通过aiu组件接收天线发送的阵元数据,并将其通过adc芯片发送至fpga芯片,得到子阵输入数据;

[0063]

s2、基于子阵输入数据,通过阵元的位置得到阵元方向向量的相位

[0064]

s3、根据相位计算出导向矢量,并发送至ram子模块;

[0065]

s4、通过tr组件接收天线的中频信号,并通过调制解调子模块解调中频信号得到跳频频点信息,进而将子阵输入数据进行幅相校正,得到子阵级数据;

[0066]

s5、将子阵级数据发送至协方差矩阵计算子模块,得到协方差矩阵;

[0067]

s6、根据smi算法得到协方差矩阵的逆矩阵,进而根据导向矢量计算出带约束指向的抗干扰的最优权值;

[0068]

s7、将抗干扰的最优权值和子阵级数据发送至滤波子模块,在滤波子模块中根据最优权值对子阵级数据进行滤波,并将其发送至dac芯片,得到天线抗干扰数据,完成天线信号抗干扰处理。

[0069]

所述步骤s2中,阵元方向向量的相位的表达式具体为:

[0070][0071]

其中,λ为中心频点对应的波长,θ为阵元方向向量的水平方位角,为阵元方向向量的竖直俯仰角,xm、ym和zm均为阵元m的坐标值(xm,ym,zm),其中m为阵元的序数,m=0,1,

…

,m-1,m-1为阵元总数。

[0072]

所述步骤s3中,导向矢量的表达式具体为:

[0073][0074]

式中,j为复数。

[0075]

所述步骤s6中,带约束指向的抗干扰的最优权值w

opt

的表达式具体为:

[0076][0077]

式中,为导向矢量,为协方差矩阵的逆;

[0078]

其中,协方差矩阵r

x

=e[x(t)xh(t)],x(t)为子阵级数据,xh(t)为子阵级数据采样系统,e[

·

]为期望函数。

[0079]

滤波子模块对输入的子阵级数据进行滤波,从而在期望信号方向形成增益,干扰方向形成零陷,从而完成抗干扰子阵级数据的输出。

[0080]

本发明的有益效果为:本发明可以在实现对信号的接收的基础上,有效提高在目标方向上的信号增益,同时能够实现对干扰信号的抑制,该抗干扰采用基于smi算法实现带

约束抗干扰算法和基于目标信号方向子阵合成方式的子阵降维抗干扰处理方式,使硬件上可实现的同时又能保证天线的有效增益,对接收目标信号带来有效的增益,从而保证系统的通信。

[0081]

基于目标信号方向子阵合成方式使得基于子阵抗干扰处理后带波束约束的问题变得简单,减少硬件资源上的处理压力。

[0082]

基于smi算法实现带约束的抗干扰算法突破了矩阵求逆工程的不可实现性,从而使得基于抗干扰算法的抗干扰性能达到理论仿真的水平,使得工程计算结果和理论计算结果一致。

[0083]

实施例1:一种基于多信道抗干扰天线信号处理的装置,其特征在于,包括信号处理模块、aiu组件、tr组件和电源模块;信号处理模块分别与aiu组件和电源模块连接,tr组件与信号处理模块连接。

[0084]

实施例2:在实施例1的基础上,信号处理模块包括fpga芯片、flash芯片、eeprom芯片、adc芯片和dac芯片;fpga芯片分别与flash芯片、eeprom芯片、adc芯片、dac芯片连接;adc芯片和dac芯片均与aiu组件连接。

[0085]

实施例3:在实施例2的基础上,fpga芯片包括ram子模块、协方差矩阵计算子模块和滤波子模块;ram子模块、协方差矩阵计算子模块和滤波子模块依次连接。

[0086]

实施例4:在实施例1的基础上,aiu组件设置有相控阵,其包括160个阵元。

[0087]

实施例5:在实施例3的基础上,fpga芯片包括调制解调子模块,调制解调子模块用于提取跳频频点信息。

[0088]

实施例6:一种基于多信道抗干扰天线信号处理的系统,在实施例5中的装置的基础上,且ram子模块与adc芯片连接,滤波子模块与dac芯片连接;aiu组件接收天线发送的阵元数据,并将其通过adc芯片发送至fpga芯片,fpga芯片从阵元数据中提取子阵输入数据,fpga芯片根据子阵输入数据的阵元位置计算出阵元方向向量的相位,并将其发送至ram子模块;tr组件接收天线的中频信号,将其发送至调制解调子模块提取跳频频点信息,调制解调子模块将跳频频点信息发送至fpga芯片,fpga芯片根据跳频频点信息将子阵输入数据进行幅相校正,得到子阵级数据,将子阵级数据发送至协方差矩阵计算子模块,协方差矩阵计算子模块输出协方差矩阵,当协方差矩阵计算子模块输出完成后,根据smi算法得到协方差矩阵的逆矩阵,并根据ram子模块存储的阵元方向向量的相位计算出带约束指向的抗干扰的最优权值,将抗干扰的最优权值发送至滤波子模块,滤波子模块对输入的子阵级数据进行滤波,并将滤波后的子阵级数据发送至dac芯片,dac芯片进行模数转换得到天线抗干扰数据,并将天线抗干扰数据通过aiu组件发射出去,完成整个系统的天线信号抗干扰处理。

[0089]

实施例7:一种基于多信道抗干扰天线信号处理方法,包括以下步骤:

[0090]

s1、通过aiu组件接收天线发送的阵元数据,并将其通过adc芯片发送至fpga芯片,得到子阵输入数据;

[0091]

s2、基于子阵输入数据,通过阵元的位置得到阵元方向向量的相位

[0092]

s3、根据相位计算出导向矢量,并发送至ram子模块;

[0093]

s4、通过tr组件接收天线的中频信号,并通过调制解调子模块解调中频信号得到跳频频点信息,进而将子阵输入数据进行幅相校正,得到子阵级数据;

[0094]

s5、将子阵级数据发送至协方差矩阵计算子模块,得到协方差矩阵;

[0095]

s6、根据smi算法得到协方差矩阵的逆矩阵,进而根据导向矢量计算出带约束指向的抗干扰的最优权值;

[0096]

s7、将抗干扰的最优权值和子阵级数据发送至滤波子模块,在滤波子模块中根据最优权值对子阵级数据进行滤波,并将其发送至dac芯片,得到天线抗干扰数据,完成天线信号抗干扰处理。

[0097]

实施例8:在实施例7的基础上,步骤s2中,阵元方向向量的相位的表达式具体为:

[0098][0099]

其中,λ为中心频点对应的波长,θ为阵元方向向量的水平方位角,为阵元方向向量的竖直俯仰角,xm、ym和zm均为阵元m的坐标值(xm,ym,zm),其中m为阵元的序数,m=0,1,

…

,m-1,m-1为阵元总数。

[0100]

实施例9:在实施例8的基础上,步骤s3中,导向矢量的表达式具体为:

[0101][0102]

实施例10:在实施例9的基础上,步骤s6中,带约束指向的抗干扰的最优权值w

opt

的表达式具体为:

[0103][0104]

式中,为导向矢量,为协方差矩阵的逆;

[0105]

其中,协方差矩阵r

x

=e[x(t)xh(t)],x(t)为子阵级数据,xh(t)为子阵级数据采样系统,e[

·

]为期望函数。

[0106]

在本发明的描述中,需要理解的是,术语“中心”、“厚度”、“上”、“下”、“水平”、“顶”、“底”、“内”、“外”、“径向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或隐含指明的技术特征的数量。因此,限定由“第一”、“第二”、“第三”的特征可以明示或隐含地包括一个或者更多个该特征。

[0107]

本发明功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,在一台计算机设备(可以是个人计算机,服务器,或者网络设备等)以及相应的软件中执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、或者光盘等各种可以存储程序代码的介质,进行测试或者实际的数据在程序实现中存在于只读存储器(random access memory,ram)、随机存取存储器(random access memory,ram)等。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。