1.本技术涉及存储设备,尤其涉及一种固态存储设备以及向其写入数据的方法。

背景技术:

2.图1展示了固态存储设备的框图。固态存储设备102同主机相耦合,用于为主机提供存储能力。主机同固态存储设备102之间可通过多种方式相耦合,耦合方式包括但不限于通过例如sata(serial advanced technology attachment,串行高级技术附件)、scsi(small computer system interface,小型计算机系统接口)、sas(serial attached scsi,串行连接scsi)、ide(integrated drive electronics,集成驱动器电子)、usb(universal serial bus,通用串行总线)、pcie(peripheral component interconnect express,pcie,高速外围组件互联)、nvme(nvm express,高速非易失存储)、以太网、光纤通道、无线通信网络等连接主机与固态存储设备102。主机可以是能够通过上述方式同存储设备相通信的信息处理设备,例如,个人计算机、平板电脑、服务器、便携式计算机、网络交换机、路由器、蜂窝电话、个人数字助理等。固态存储设备102包括接口103、控制部件104、一个或多个nvm芯片105以及dram(dynamic random access memory,动态随机访问存储器)110。

3.nand闪存、相变存储器、feram(ferroelectric ram,铁电存储器)、mram(magnetic random access memory,磁阻存储器)、rram(resistive random access memory,阻变存储器)等是常见的nvm。

4.接口103可适配于通过例如sata、ide、usb、pcie、nvme、sas、以太网、光纤通道等方式与主机交换数据。

5.控制部件104用于控制在接口103、nvm芯片105以及dram 110之间的数据传输,还用于存储以及管理主机逻辑地址到闪存物理地址的映射、擦除均衡、坏块管理等。控制部件104可通过软件、硬件、固件或其组合的多种方式实现,例如,控制部件104可以是fpga(field-programmable gate array,现场可编程门阵列)、asic(application specific integrated circuit,应用专用集成电路)或者其组合的形式。控制部件104也可以包括处理器或者控制器,在处理器或控制器中执行软件来操纵控制部件104的硬件来处理io(input/output)命令。控制部件104还可以耦合到dram 110,并可访问dram 110的数据。在dram可存储ftl表和/或缓存的io命令的数据。

6.控制部件104包括闪存接口控制器(或称为介质接口控制器、闪存通道控制器),闪存接口控制器耦合到nvm芯片105,并以遵循nvm芯片105的接口协议的方式向nvm芯片105发出命令,以操作nvm芯片105,并接收从nvm芯片105输出的命令执行结果。已知的nvm芯片接口协议包括“toggle”、“onfi”等。

7.在现有的固态存储设备中,利用ftl(flash translation layer,闪存转换层)来维护从逻辑地址到物理地址的映射信息。逻辑地址构成了操作系统等上层软件所感知到的固态存储设备的存储空间。物理地址是用于访问固态存储设备的物理存储单元的地址。在相关技术中还可利用中间地址形态实施地址映射。例如将逻辑地址映射为中间地址,进而

将中间地址进一步映射为物理地址。

8.存储了从逻辑地址到物理地址的映射信息的表结构被称为ftl表。ftl表是固态存储设备中的重要元数据。通常ftl表的数据项记录了固态存储设备中以数据页为单位的地址映射关系。

9.nvme协议中还定义了刷写(flush)命令。通过flush命令,指示存储设备将先于flush命令接收到的所有命令要写入的数据(及其元数据)都保存到非易失存储介质。

10.固态存储设备使用缓存来提高性能。对于写命令,将写命令指示的数据写入缓存后,即指示写命令处理完成。由于缓存的存在,在处理flush命令时,要将缓存中的数据写入非易失存储介质,这一过程占用了过长的时间。需要降低或避免因flush命令而使主机经历的将缓存中的数据写入非易失存储介质过程引起的性能抖动。

技术实现要素:

11.本技术的固态存储设备以及向其写入数据的方法的解决了因flush命令所引发的固态存储设备写入数据时产生的性能抖动问题。

12.根据本技术的第一方面,本技术提供一种向固态存储设备写入数据的方法,其中,包括如下步骤:响应于接收了刷写命令,获取当前时间以生成关联于所述刷写命令的时间戳;访问缓存描述符;获得缓存描述符中的时间戳数据;将缓存描述符的时间戳早于所述刷写命令的时间戳的缓存描述符所指示的缓存单元的数据写入非易使性存储器。

13.根据本技术的第一方面的一种向固态存储设备写入数据的方法,其中,在时间戳早于所述刷写命令的时间戳的所有缓存描述符所指示的缓存单元的数据都写入非易使性存储器时,指示所述刷写命令处理完成。

14.根据本技术的第一方面的一种向固态存储设备写入数据的方法,其中,所述缓存描述符中包括所分配的缓存单元的索引、指示所分配的缓存单元写入时间的时间戳以及所分配的缓存单元中数据的地址。

15.根据本技术的第一方面的一种向固态存储设备写入数据的方法,其中,其中,所述数据的地址是非易使性存储器的逻辑地址或物理地址。

16.根据本技术的第一方面的一种向固态存储设备写入数据的方法,其中,当接收的是写命令时,为写命令分配动态随机存储器的缓存单元与缓存描述符。

17.根据本技术的第一方面的一种向固态存储设备写入数据的方法,其中,在接收刷写命令之后,设置标记以指示有刷写命令待处理;在刷写命令处理完成后,清除所设置的标记。

18.根据本技术的第二方面,本技术还提供一种向固态存储设备写入数据的方法,其中,包括如下步骤:响应于动态随机存储器的缓存单元被写入数据,轮询缓存描述符;根据缓存描述符,将缓存单元内的数据写入非易使性存储器。

19.根据本技术的第二方面的一种向固态存储设备写入数据的方法,其中,响应于缓存单元内的数据写入非易使性存储器,释放所述缓存单元。

20.根据本技术的第三方面,本技术还提供一种向固态存储设备写入数据的方法,其中,包括如下步骤:响应于接收了写命令,识别所述写命令是否命中了缓存单元;若所述写命令命中了缓存单元,判断所述命中的缓存单元是否受到刷写命令的影响;若被命中的缓

存单元受刷写命令的影响,则临时缓存所述写命令以待所述刷写命令处理完成后再处理所述写命令或者为写命令分配新的不受刷写命令影响的缓存单元。

21.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,若所述写命令未命中缓存单元,则为所述写命令分配空闲的缓存单元,并将写命令对应的数据存储在缓存单元中。

22.根据本技术的第三方面的一种的向固态存储设备写入数据的方法,其中,通过写命令要访问的逻辑地址与缓存描述符所记录的逻辑地址是否一致来识别所述写命令是否命中了缓存单元。

23.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,若被命中的缓存单元不受刷写命令的影响,则将写命令待写入的存储在被命中的缓存单元中,并指示写命令处理完成。

24.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,在当前没有待执行的刷写命令或者当前虽然有待执行的刷写命令,但所述待执行的刷写命令的时间戳小于被命中的缓存单元的时间戳时,判断被命中的缓存单元不受刷写命令的影响。

25.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,在当前有待执行的刷写命令且所述待执行的刷写命令的时间戳不小于被命中的缓存单元的时间戳时,判断被命中的缓存单元受刷写命令的影响。

26.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,在临时缓存所述写命令期间,继续接收命令并进行处理。

27.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,为写命令分配新的不受刷写命令影响的缓存单元是在当前没有待执行的刷写命令时的任意未被占用的缓存单元或者当前虽然有待执行的刷写命令,但所述待执行的刷写命令的时间戳小于缓存单元的时间戳的未被占用的缓存单元。

28.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,为写命令分配新的不受刷写命令影响的缓存单元之后,还为所述新的不受刷写命令影响的缓存单元分配缓存描述符。

29.根据本技术的第三方面的一种向固态存储设备写入数据的方法,其中,所述缓存描述符中包括所分配的缓存单元的索引、指示所分配的缓存单元写入时间的时间戳以及所分配的缓存单元中数据的地址。

30.根据本技术的第三方面的一种所述的向固态存储设备写入数据的方法,其中,在所述写入命令对应的数据存储在缓存单元中后,指示所述写入命令完成。

31.根据本技术的第四方面,本技术还提供一种固态存储设备,包括动态随机存储器、控制器与非易失性存储器,其中,控制器执行如上之一所述的方法。

32.根据本技术的第四方面,本技术还提供一种包含程序代码的程序,当被载入cpu并在cpu中执行时,程序使cpu执行如上所述的之一的方法。

附图说明

33.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本

申请中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

34.图1为现有技术的固态存储设备的结构示意图;

35.图2为根据本技术实施例的固态存储设备的结构示意图;

36.图3为根据本技术实施例的缓存描述符;

37.图4a-4c为根据本技术实施例的处理flush命令的示意图;

38.图5a-5d为根据本技术又一实施例的处理flush命令的示意图;

39.图6为根据本技术实施例的利用缓存处理flush命令的流程图;

40.图7为根据本技术又一实施例的利用缓存处理flush命令的流程图。

具体实施方式

41.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

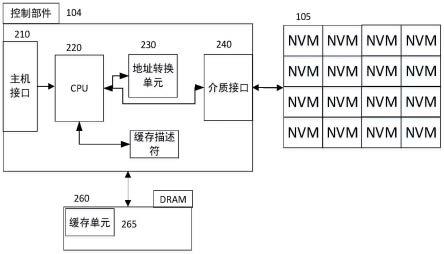

42.图2展示了根据本技术实施例的固态存储设备的框图。固态存储设备的控制部件包括主机接口210、cpu 220、地址转换单元230和用于访问nvm芯片105的介质接口240。控制部件还耦合到外部存储器(例如,dram)260。

43.控制部件的存储器中存储了缓存描述符。缓存描述符的一个或多个记录了对应的缓存单元265在dram260中的地址与占用缓存单元的数据的存储设备地址(例如,存储设备可被主机访问的逻辑地址或物理地址)。

44.主机接口210用于同主机交换命令与数据。例如,主机与存储设备通过nvme/pcie协议通信,主机接口210处理pcie协议数据包,提取出nvme协议命令,并向主机返回nvme协议命令的处理结果。

45.cpu 220耦合到主机接口210,用于接收主机发送给存储设备的io命令,并利用一个或多个缓存单元265来服务所接收的io命令。若主机使用逻辑地址访问存储设备,cpu 220还访问地址转换单元230以将逻辑地址转换为物理地址。cpu 220还将接收的io命令(io命令形态在处理处理过程中可能发生变化,这里为了表达简洁而统称为io命令)发送给介质接口240,由介质接口240根据io命令访问一个或多个nvm芯片。

46.图3展示了根据本技术实施例的缓存描述符。

47.每个缓存描述符用于描述同其对应的一个缓存单元。缓存描述符记录了对应的缓存单元的索引(图3的缓存单元索引)、时间戳与逻辑地址(lba)。缓存单元索引指示缓存单元在dram 260中的位置。时间戳记录缓存单元被分配的时间,逻辑地址(lba)记录该缓存单元被分配给的io命令所访问的逻辑地址。可以理解地,主机使用物理地址访问存储设备时,缓存单元描述符的逻辑地址字段被替换为记录物理地址。

48.图4a-4c展示了根据本技术实施例处理flush命令的示意图。

49.图4a展示了命令队列中按时间顺序收到的io命令。最早在t1时刻收到写命令(iow1),接下来在t2时刻收到写命令(iow2),然后收到flush命令,接下来在t3时刻与t4时刻依次收到写命令(io w3)与写命令(iow4)。图4a中,箭头指示时间流逝的方向。收到flush

命令的时刻在t3时刻与t4时刻之间。

50.图4b展示了处理flush命令之前,缓存单元的状态。根据本技术实施例的存储设备,收到flush命令后,并不停止对其他io命令的接收与处理。因而虽然在写命令(iow3)之前收到了flush命令,对写命令(io w3)与写命令(iow4)依然已经开始处理,为写命令(iow3)分配了缓存单元(由id3指示),并且写命令(iow3)要写入的数据已经被存储在缓存单元中,为写命令(io w4)分配了缓存单元(由id4指示),但写命令(io w4)要写入的数据尚未被写入缓存单元。

51.图4c展示了处理flush命令之后,缓存单元的状态。响应于收到flush命令,将先于接收flush命令而接收的所有io命令(参看图4a,写命令(iow1)与写命令(iow2))的要写入的数据写入到非易失存储介质(例如,nvm芯片105,也参看图2)。接下来可以向主机指示flush命令被处理完成。而此时写命令(iow3)与写命令(iow4)要写入的数据是否被写入非易失存储介质不受该flush命令的语义约束。

52.图5a-5d展示了根据本技术又一实施例处理flush命令的示意图。

53.图5a与图4a相同,展示了命令队列中按时间顺序收到的io命令。最早在t1时刻收到写命令(iow1),接下来在t2时刻收到写命令(iow2),然后收到flush命令,接下来在t3时刻与t4时刻依次收到写命令(io w3)与写命令(iow4)。图5a中,箭头指示时间流逝的方向。收到flush命令的时刻在t3时刻与t4时刻之间。

54.图5b展示了处理flush命令之前,缓存单元的状态。根据本技术实施例的存储设备,收到flush命令后,并不停止对其他io命令的接收与处理。因而虽然在写命令(iow3)之前收到了flush命令,对写命令(io w3)与写命令(iow4)依然已经开始处理,为写命令(iow3)分配了缓存单元(由id3指示),并且写命令(iow3)要写入的数据尚未被存储在缓存单元中。以及在flush命令开始处理前,尚未给写命令(io w4)分配缓存单元。

55.图5c展示了处理flush命令过程中的某时刻,缓存单元的状态。响应于收到flush命令,要将先于接收flush命令而接收的所有io命令(参看图5a,写命令(iow1)与写命令(iow2))的要写入的数据写入到非易失存储介质(例如,nvm芯片105,也参看图2)。在图5c展示的时刻,写命令(iow1)要写入的数据已经被写入非易失存储介质,而写命令(io w2)要写入的数据尚未被写入非易失性存储介质。写命令(io w3)要写入的数据依然尚未被写入缓存单元。以及依然尚未给写命令(io w4)分配缓存单元。

56.图5d展示了处理flush命令之后,缓存单元的状态。先于接收flush命令而接收的所有io命令(参看图5a,写命令(iow1)与写命令(iow2))的要写入的数据已经被写入到非易失存储介质(例如,nvm芯片105,也参看图2)。由于写命令(iow1)被处理完成,其占用的缓存单元被释放,该缓存单元可被分配给其他写命令。写命令(io w2)占用的缓存单元尚未被释放。

57.接下来可以向主机指示flush命令被处理完成。而此时写命令(iow3)与写命令(iow4)要写入的数据是否被写入非易失存储介质不受该flush命令的语义约束。作为举例,参看图5d,写命令(io w3)要写入的数据依然尚未被写入缓存单元。以及为写命令(io w4)分配了缓存单元(id 4)。

58.图6是根据本技术实施例的利用缓存处理flush命令的流程图。

59.根据图6的实施例所展示的处理流程由例如图2的cpu 220控制,并协同控制部件

104的其他部分共同完成。

60.响应于从主机接口获取的io命令(610),识别io命令的类型,以区分io命令是写命令(620),还是flush命令(670)。对于写命令,为写命令分配缓存,例如,分配尚未被使用的缓存单元与缓存描述符。在缓存描述符中记录分配的缓存单元的地址、指示当前时间的时间戳,以及从主机获取写命令要写入的数据,将要写入的数据存储在分配的缓存单元中(630)。至此虽然写命令对应的数据尚未被写入nvm芯片,但可向主机指示该写命令处理完成(640)。

61.在cpu中运行的另一任务,用于将写入缓存单元的数据搬移到nvm芯片(650)。例如,响应于缓存单元被写入数据,即开始将缓存单元的数据搬移到nvm芯片的过程。作为又一个例子,轮询各缓存描述符,以轮流地将被写入了数据的缓存单元的数据搬移到nvm芯片。可选地,响应于缓存单元中的数据被搬移到nvm芯片,释放该缓存单元,从而该缓存单元中的时间戳被更新(或清除),以及该缓存单元可被分配给其他写命令。

62.对于从主机接口获取的io命令,如为flush命令,获取当前时间以生成关联于该flush命令的时间戳(680)。通过访问各缓存描述符,以识别时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据是否都被搬移到了nvm芯片(660)。如果时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据都被搬移到了nvm芯片,则向主机指示该flush命令处理完成(690)。

63.如果时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据并未都被搬移到了nvm芯片,对于该flush命令,则待时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据都被搬移到了nvm芯片(660)后,再向主机指示该flush命令处理完成(690)。可以理解地,在等待时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据都被搬移到了nvm芯片期间,可继续执行图6所示的流程,从主机接口获取io命令并进行处理。

64.作为举例,若收到了flush命令,设置标记以指示有flush命令待处理。并且在每次从主机接口获取了io命令后,若发现指示有flush命令待处理的标记存在,访问各缓存描述符,以识别时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据是否都被搬移到了nvm芯片。若识别出flush命令被处理完成,还清除所设置的标记。

65.参看图6,作为举例,将写入缓存单元的数据搬移到nvm芯片的任务持续不断的执行,而并非响应于识别出时间戳早于该flush命令的时间戳的各缓存描述符所指示的缓存单元的数据并未都被搬移到了nvm芯片而被执行。但是,对flush命令的处理依赖于将缓存单元中的关联于flush命令的缓存单元的数据搬移到nvm芯片。可选地,响应于要处理flush命令,优先处理将关联于flush命令的缓存单元的数据搬移到nvm芯片的任务,以将写入这些缓存单元的数据尽早搬移到nvm芯片。

66.图7是根据本技术又一实施例的利用缓存处理flush命令的流程图。

67.在图6所示的流程图的基础上,根据图7的实施例的流程图进一步处理io写命令命中缓存单元的情形。

68.响应于接收了写命令(720),通过写命令要访问的逻辑地址与缓存描述符记录的逻辑地址是否一致来识别写命令是否命中了缓存单元(730)。

69.若写命令未命中缓存单元,为写命令分配空闲的缓存单元,在该缓存单元对应的

缓存条目中记录指示当前时间的时间戳,并将写命令对应的数据存储在缓存单元(740)。以及向主机指示写命令处理完成(770)。

70.若写命令命中了缓存单元,进一步识别被命中的缓存单元是否是受到flush命令影响而其数据需要被写入nvm芯片的缓存单元(750)。若被命中的缓存单元不受flush命令影响(当前没有待执行的flush命令,或者当前有待执行的flush命令,但待执行flush命令的时间戳小于被命中缓存单元的时间戳),则将写命令待写入的数据存储在被命中的缓存单元(760),并向主机指示写命令处理完成(770)。若被命中的缓存单元受到flush命令影响(当前有待执行的flush命令,且待执行flush命令的时间戳不小于被命中缓存单元的时间戳)(750),则临时缓存该写命令(780)以待flush命令被处理完成后再处理该写命令。在临时缓存该写命令期间,还从主机接口获取其他io命令进行处理,以避免因执行flush命令而造成存储设备的性能抖动。

71.可选地,若被命中的缓存单元受到flush命令影响,为写命令分配新的缓存单元与缓存描述符,在缓存描述符中记录分配的缓存单元的地址、指示当前时间的时间戳,以及从主机获取写命令要写入的数据,将要写入的数据存储在分配的缓存单元中,接下来向主机指示该写命令处理完成。

72.本技术实施例还提供一种包括程序代码的程序,当被载入主机并在主机上执行时,所述程序使主机的处理器执行上面提供的根据本技术实施例的方法之一。

73.应该理解,框图和流程图的每个框以及框图和流程图的框的组合可以分别由包括计算机程序指令的各种装置来实施。这些计算机程序指令可以加载到通用计算机、专用计算机或其他可编程数据控制设备上以产生机器,从而在计算机或其他可编程数据控制设备上执行的指令创建了用于实现一个或多个流程图框中指定的功能的装置。

74.这些计算机程序指令还可以存储在可以引导计算机或其他可编程数据控制设备的计算机可读存储器中从而以特定方式起作用,从而能够利用存储在计算机可读存储器中的指令来制造包括用于实现一个或多个流程图框中所指定功能的计算机可读指令的制品。计算机程序指令还可以加载到计算机或其他可编程数据控制设备上以使得在计算机或其他可编程数据控制设备上执行一系列的操作操作,从而产生计算机实现的过程,进而在计算机或其他可编程数据控制设备上执行的指令提供了用于实现一个或多个流程图框中所指定功能的操作。

75.因而,框图和流程图的框支持用于执行指定功能的装置的组合、用于执行指定功能的操作的组合和用于执行指定功能的程序指令装置的组合。还应该理解,框图和流程图的每个框以及框图和流程图的框的组合可以由执行指定功能或操作的、基于硬件的专用计算机系统实现,或由专用硬件和计算机指令的组合实现。

76.虽然当前发明参考的示例被描述,其只是为了解释的目的而不是对本技术的限制,对实施方式的改变,增加和/或删除可以被做出而不脱离本技术的范围。

77.这些实施方式所涉及的、从上面描述和相关联的附图中呈现的教导获益的领域中的技术人员将认识到这里记载的本技术的很多修改和其他实施方式。因此,应该理解,本技术不限于公开的具体实施方式,旨在将修改和其他实施方式包括在所附权利要求书的范围内。尽管在这里采用了特定的术语,但是仅在一般意义和描述意义上使用它们并且不是为了限制的目的而使用。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。