基于单片机总线复用的多路并行dac配置电路结构

技术领域

1.本公开涉及电子技术领域,尤其涉及一种基于单片机总线复用的多路并行dac配置电路结构。

背景技术:

2.在高等级高可靠的电路设计中,80c32单片机一直广泛应用各子系统和子模块。但是80c32单片机开发设计较早,其i/o口资源极其有限,往往会出现资源不够的情况。这种情况下通用的解决方法是外加一片i/o口拓展芯片,也即串并转换芯片,这种情况会增加额外的体积和重量。这在航空航天领域会提高成本和降低可靠性。

技术实现要素:

3.(一)要解决的技术问题

4.基于上述问题,本公开提供了一种基于单片机总线复用的多路并行 dac配置电路结构,以缓解现有技术中解决单片机芯片i/o口资源有限的问题时会提高成本和见底可靠性等技术问题。

5.(二)技术方案

6.本公开提供一种基于单片机总线复用的多路并行dac配置电路结构,包括:

7.单片机模块,包括一单片机芯片;

8.外部只读存储器;

9.锁存器模块,其输入连接至单片机芯片的一i/o口;

10.逻辑门模块,其一输入端连接至单片机芯片的另一i/o口,另一输入端连接至单片机芯片的写入端管脚;以及

11.dac模块,包括并行的两个dac芯片,所述两个dac芯片的时钟管脚分别连接至所述逻辑门模块的输出端,从而通过单片机芯片的wr管脚来配置并行dac芯片的时钟管脚,实现基于单片机总线复用的多路并行dac配置。

12.根据本公开实施例,所述单片机芯片的型号为80c32。

13.根据本公开实施例,所述并行dac芯片型号为ad9764。

14.根据本公开实施例,还包括外部随机存取存储器。

15.根据本公开实施例,所述的总线复用是指80c32的地址总线复用,复用时的电平配置是基于80c32的外部存取指令来实现。

16.根据本公开实施例,所述单片机芯片的外部存储读取专用管脚也作为控制管脚复用。

17.根据本公开实施例,单片机昔年的wr管脚或者rd管脚被用于dac 刷新控制信号。

18.根据本公开实施例,借助单片机芯片的i/o口和wr管脚的或逻辑输出为dac芯片的clk信号。

19.根据本公开实施例,基于单片机芯片80c32的数据总线复用的多路并行adc读取

时,其最高可读取8位adc的值。

20.(三)有益效果

21.从上述技术方案可以看出,本公开基于单片机总线复用的多路并行 dac配置电路结构至少具有以下有益效果其中之一或其中一部分:

22.(1)结构简洁高效,便于pcb板级集成;

23.(2)巧妙利用了80c32单片机的地址总线复用,可实现单个80c32 单片机挂载多个并行dac芯片并可独立配置的功能;

24.(3)在时序上可靠稳定,可适应于高等级系统中的电路设计;

25.(4)节省了额外的芯片(例如i/o拓展芯片),节约了空间、功耗,具备更好的热学性能。

附图说明

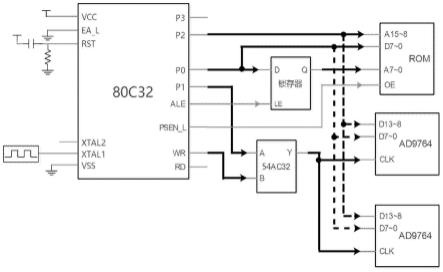

26.图1为本公开实施例基于单片机总线复用的多路并行dac配置电路结构的总体框图。

27.图2为本公开实施例基于单片机总线复用的多路并行dac配置电路结构中单片机芯片和逻辑门芯片配置时序图。

28.图3为本公开实施例基于单片机总线复用的多路并行dac配置电路结构中dac芯片配置时序图。

具体实施方式

29.本公开提供了一种基于单片机总线复用的多路并行dac配置电路结构,基于80c32单片机总线复用的多路并行dac配置电路设计,可实现在只需要片选i/o口资源的情况下对多片并行14位dac的独立配置。

30.虽然随着微电子技术的不断进步,控制器芯片的资源越来越多,但是在高等级,特别是抗辐照等级领域,单片机一直以来都备受国内工程师的青睐。单片机的高等级版本具备抗辐照、抗震、温度范围广等优点,同时由于其资源(i/o口资源)较少,也给工程电路设计添加了难度。本公开主要解决80c32单片机在配置并行dac时遇到的i/o口资源不够的问题,框图如下所示,具体实例以ad9764芯片为例。图1简要示意了80c32单片机在配置外部rom的基础上,通过地址总线复用以及或逻辑门芯片54ac32 实现了对两片ad9764芯片的独立配置。关于配置ad9764的时序,是利用80c32单片机对外部ram进行读取的时序,即巧妙借用了wr管脚来配置ad9764的时钟管脚。具体的ad9764片选使能,则是利用其他i/o 口和wr管脚做或逻辑计算来实现。

31.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。

32.在本公开实施例中,提供一种基于单片机总线复用的多路并行dac 配置电路结构,如图1所示,所述基于单片机总线复用的多路并行dac 配置电路结构,包括:

33.单片机模块,包括一单片机芯片;

34.外部只读存储器;

35.锁存器模块,其输入连接至单片机芯片的一i/o口;

36.逻辑门模块,其一输入端连接至单片机芯片的另一i/o口,另一输入端连接至单片机芯片的写入端管脚;以及

37.dac模块,包括并行的两个dac芯片,所述两个dac芯片的时钟管脚分别连接至所述逻辑门模块的输出端,从而通过单片机芯片的wr管脚来配置并行dac芯片的时钟管脚,实现基于单片机总线复用的多路并行dac配置。

38.如图1所示,基于单片机总线复用的多路并行dac配置电路结构包含80c32单片机的最小系统、基于总线复用的并行dac(以ad9764为例) 数据配置、基于额外i/o口与wr专用管脚的组合逻辑控制dac转化。本公开涉及到的80c32单片机最小系统包括锁存器芯片(54ac573)和外部只读存储器芯片(rom/prom),此外还可以挂载额外的随机存取芯片 (ram)。

39.本公开的实施例可实现80c32独立配置多片14位并行dac,进一步地,也可更换为其他单片机。

40.本公开所提出的基于总线复用的并行dac数据配置和时序控制,以特定情况举例。如图2和图3所示,分别为80c332单片机进行外部内存读取时的时序图和ad9764(一款14位并行dac芯片)的配置时序图。其主要配置过程如下:

41.通过其他i/o口操作,进行dac芯片的片选,如图为p2口管脚的选通,拉低为选通,拉高为失能disable不操作。

42.80c32进行外部数据写入操作,使用软件编程c语言为:

43.xbyte[addr]=data;

[0044]

与图2中的时序对应,其中寻址地址addr为a15-a0,写入数据data 为d7-d0。wr管脚输出的电平逻辑与i/o选通端一起经过或逻辑门输出给ad9764的clk管脚。由图3知ad9764在clk的上升沿进行数模转换,也就是在wr的上升沿做数模转换(中间经过或逻辑门芯片,时沿很小,此处可以忽略)。故addr的低八位即a7-a0与d7-d0相同即可实现对 ad9764的输入端口配置成a13-a0的功能。

[0045]

延时几个时钟周期,待ad9764转化后稳定即可等待下一次操作。

[0046]

进行时序稳定性分析:

[0047]

本公开主要论证ad9764的时序配置是否满足其芯片的时序要求。主要根据图2和图3所示的时序分析。图3为ad9764的配置时序,其主要时序要求有三点:

[0048]

clk时钟上升沿到来之前,输入端数据d13-d0需要保持一段时间,即ts>2ns。

[0049]

clk时钟脉冲宽度需要大于特定值,即t

lpw

>4.5ns。

[0050]

clk时钟上升沿之后,需要保持特定时间到数模转换完成,即t

pd

>6ns。

[0051]

同样地,图2中的时序根据80c32单片机手册可以得到:

[0052]

(1)数据d7-d0相对于wr上升沿的建立时间为t

dl

t

pw

>200ns。故满足上述条件2的要求,t

lpw

=t

dl

t

pw

>200ns>4.5ns。

[0053]

(2)wr上升沿之后的保持时间大于20ns,即同时满足上述条件1 和条件3的要求。

[0054]

根据本公开实施例,总线复用是指80c32的地址总线复用,复用时的电平配置是基于80c32的外部存取指令来实现。进一步地,80c32的外部存储读取专用管脚wr也做为控制管脚复用。多路并行dac配置,其中所有的dac的数据配置是与地址总线复用,而wr管脚或者rd管脚则是dac刷新控制信号。进一步地,要实现对多个dac的独立配置,还需要借助其他i/

o口,摘要附图1中举的例子为借助p1端口和wr管脚的或逻辑输出为ad9764的clk信号。也可以借助同样的方式来实现对多路adc的读取。在此情况下,是基于80c32数据总线复用的多路并行adc 读取,其最高可读取8位adc的值。

[0055]

综上所述,该方案在理论上不会存在时序的问题,非常具备实用性,并且已经成功应用到工程项目中。

[0056]

至此,已经结合附图对本公开实施例进行了详细描述。需要说明的是,在附图或说明书正文中,未绘示或描述的实现方式,均为所属技术领域中普通技术人员所知的形式,并未进行详细说明。此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换。

[0057]

依据以上描述,本领域技术人员应当对本公开基于单片机总线复用的多路并行dac配置电路结构有了清楚的认识。

[0058]

综上所述,本公开提供了一种基于单片机总线复用的多路并行dac 配置电路结构主要针对单片机在配置并行dac芯片时出现的端口资源不够的情况,提出一种基于地址总线复用的方法来配置多路并行dac芯片的解决方案,实现单个单片机挂载多个并行dac芯片并可独立配置的功能,节约了空间、功耗,具备更好的热学性能。

[0059]

还需要说明的是,实施例中提到的方向用语,例如“上”、“下”、“前”、“后”、“左”、“右”等,仅是参考附图的方向,并非用来限制本公开的保护范围。贯穿附图,相同的元素由相同或相近的附图标记来表示。在可能导致对本公开的理解造成混淆时,将省略常规结构或构造。并且图中各部件的形状和尺寸不反映真实大小和比例,而仅示意本公开实施例的内容。

[0060]

说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等的用词,以修饰相应的元件,其本身并不意味着该元件有任何的序数,也不代表某一元件与另一元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一元件得以和另一具有相同命名的元件能做出清楚区分。

[0061]

此外,除非特别描述或必须依序发生的步骤,上述步骤的顺序并无限制于以上所列,且可根据所需设计而变化或重新安排。并且上述实施例可基于设计及可靠度的考虑,彼此混合搭配使用或与其他实施例混合搭配使用,即不同实施例中的技术特征可以自由组合形成更多的实施例。

[0062]

以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。