用于向集成电路的一部分供应功率的装置和方法

1.本技术是国际申请日为2017年04月24日、国际申请号pct/us2017/029186、于2018年11月16日进入中国国家阶段、中国国家申请号201780030700.7、发明名称为“用于经由弱强和仅强开关单元向集成电路的一部分供应功率的装置和方法”的发明专利申请的分案申请。

2.相关申请的交叉引用

3.本技术要求于2016年5月18日在美国专利商标局提交的非临时申请no.15/158,236的优先权和权益,其全部内容通过引用并入本文。

技术领域

4.本公开的各方面总体上涉及功率门控电路,并且具体地,涉及用于使用弱强开关单元和仅强开关单元向集成电路(ic)的一部分供应功率的装置和方法,以及设计功率门控电路的方法。

背景技术:

5.功率门控电路用于将端子电压轨(tvdd)耦合到集成电路(ic)的内部电压轨(vdd)。端子电压轨(tvdd)从电池、调节器或其他类型的源接收外部供应电压。功率门控电路通过将端子电压轨(tvdd)电耦合到内部电压轨(vdd)来将外部供应电压施加到ic的一部分(例如,核或模块)。

6.功率门控电路通常包括用于将端子电压轨(tvdd)单独耦合到内部电压轨(vdd)的开关单元的集合。该开关单元的集合通常包括弱开关单元的子集和强开关单元的子集。为了限制浪涌电流,首先导通弱开关单元以允许内部功率轨(vdd)部分充电。然后,导通强开关单元以将端子电压轨(tvdd)完全耦合到内部电压轨(vdd),使得功率门控电路能够提供ic的一部分(例如,核或模块)对电流(例如,动态电流)的总需求。

7.通常,存在弱开关单元与强开关单元(或总开关单元)的特定比率,其产生最小化的浪涌电流峰值。在功率门控电路的设计阶段,该比率基于ic的该部分(例如,核或模块)的设计来估计。如果估计的比率被证明是不准确的,则需要通过将弱开关单元换成强开关单元或反之亦然来重新设计功率门控电路。这样的单元的交换需要重新路由功率门控电路到ic部分的连接,并且执行ic部分的操作的定时分析。重新设计功率门控电路、重新路由和定时分析之间的这种相互作用使ic的设计复杂化,并且经常导致不能实现弱开关单元与强开关单元(或总开关单元)的最佳比率。

技术实现要素:

8.下面呈现一个或多个实施例的简要概述,以便提供对这样的实施例的基本理解。本“发明内容”不是所有预期实施例的广泛概述,并且既不旨在标识所有实施例的关键或重要元素,也不旨在界定任何或所有实施例的范围。其唯一目的是以简化的形式呈现一个或多个实施例的一些概念,作为稍后呈现的更详细描述的序言。

9.本公开的一方面涉及一种装置,包括:第一类型开关单元的集合,其中每个第一类型开关单元被配置为响应于第一使能信号经由第一相对弱晶体管将第一功率轨耦合到第二功率轨,以及响应于第二使能信号经由第一相对强晶体管将第一功率轨耦合到第二功率轨;以及第二类型开关单元的集合,其中每个第二类型开关单元被配置为响应于第一使能信号经由第二相对弱晶体管和第二相对强晶体管将第一功率轨耦合到第二功率轨。

10.本公开的另一方面涉及一种设计用于向特定电路供应功率的功率门控电路的方法。该方法包括:通过用第一类型开关单元的集合或第二类型开关单元的集合中的至少一个开关单元填充单元槽来生成功率门控电路的第一设计,其中每个第一类型开关单元被配置为响应于第一使能信号将第一功率轨弱耦合到第二功率轨,并且其中每个第一类型开关单元和每个第二类型开关单元被配置为响应于第二使能信号将第一功率轨强耦合到第二功率轨;确定第一类型开关单元与第二类型开关单元的比率;以及通过将至少一个第一类型开关单元换成至少一个第二类型开关单元或者将至少一个第二类型开关单元换成至少一个第一类型开关单元以实现上述比率,来生成功率门控电路的第二设计。

11.本公开的另一方面涉及一种装置,包括:第一部件,用于响应于第一使能信号经由第一相对弱晶体管将第一功率轨耦合到第二功率轨,以及响应于第二使能信号经由第一相对强晶体管将第一功率轨耦合到第二功率轨;以及第二部件,用于响应于第二使能信号经由第二相对弱晶体管和第二相对强晶体管将第一功率轨耦合到第二功率轨。

12.为了实现前述和相关目的,一个或多个实施例包括在下文中充分描述并且在权利要求中特别指出的特征。以下描述和附图详细阐述了一个或多个实施例的某些说明性方面。然而,这些方面仅指示可以采用各种实施例的原理的各种方式中的一些,并且描述实施例旨在包括所有这些方面及其等同物。

附图说明

13.图1a示出了根据本公开的一方面的、对于弱开关与强开关的比率太低的情况、内部轨电压vdd和对应的浪涌电流相对于时间的一对曲线图。

14.图1b示出了根据本公开的另一方面的、对于弱开关与强开关的比率太大的情况、内部轨电压vdd和对应的浪涌电流相对于时间的一对曲线图。

15.图1c示出了根据本公开的另一方面的、对于弱开关与强开关的比率被设置为产生基本上相等的浪涌电流峰值的情况、内部轨电压vdd和对应的浪涌电流相对于电流的一对曲线图。

16.图2示出了根据本公开的另一方面的用于向集成电路(ic)的一部分(例如,核或模块)供应功率的示例性功率门控电路的框图。

17.图3示出了根据本公开的另一方面的示例性弱开关单元的示意图。

18.图4示出了根据本公开的另一方面的示例性强开关单元的示意图。

19.图5示出了根据本公开的另一方面的示例性弱强开关单元的示意图。

20.图6示出了根据本公开的另一方面的示例性仅强开关单元的示意图。

21.图7示出了根据本公开的另一方面的示例性弱强开关单元的覆盖区(布局配置)的俯视图。

22.图8示出了根据本公开的另一方面的示例性仅强开关单元的覆盖区(布局配置)的

俯视图。

23.图9示出了根据本公开的另一方面的用于向集成电路(ic)的一部分(例如,核或模块)供应功率的示例性功率门控电路的框图。

24.图10示出了根据本公开的另一方面的用于向集成电路(ic)的一部分(例如,核或模块)供应功率的另一示例性功率门控电路的框图。

25.图11示出了根据本公开的另一方面的设计功率门控电路的示例性方法的流程图。

具体实施方式

26.以下结合附图阐述的详细描述旨在作为各种配置的描述,而非旨在表示可实践本文中描述的概念的仅有配置。详细描述包括具体细节,以便提供对各种概念的透彻理解。然而,对于本领域技术人员很清楚的是,可以在没有这些具体细节的情况下实践这些概念。在一些实例中,以框图形式示出了公知的结构和部件,以避免模糊这样的概念。

27.在集成电路(ic)的一部分(例如,核或模块)的上电操作期间,端子功率轨(tvdd)上的供应电压经由功率门控电路被施加到内部功率轨(vdd)。功率门控电路通常包括相对弱开关(例如,弱场效应晶体管(fet))和相对强开关(例如,强fet)的混合。

28.如果所有开关在上电操作期间同时导通,则以这种方式配置功率门控电路以防止大的浪涌电流。这种大的浪涌电流可能导致ic复位并且可能由于例如电迁移而对ic造成永久性损坏。

29.在上电操作期间,功率门控电路被配置为首先导通弱开关以将初始浪涌电流的峰值保持在特定阈值以下。一旦初始浪涌电流达到峰值并且然后稳定到远低于阈值的特定水平,则功率门控电路被配置为导通强开关,使得功率门控电路能够满足它向其供应功率的ic部分的总(例如,动态)电流需求。

30.在上电操作期间,观察到浪涌电流的两个峰值。一个峰值响应于弱开关的导通而发生,而另一峰值响应于强开关的导通而发生。通常希望浪涌电流的两个峰值基本上均衡,以实现低于期望的安全阈值的峰值。如下面更详细讨论的,弱开关与强开关的比率确定了相应峰值的大小。

31.图1a示出了对于弱开关与强开关的比率太低的情况(换言之,弱开关的数目不足)、内部轨电压vdd(例如,从0到1.1v)和对应的浪涌电流(例如,从0到20毫安(ma))相对于时间的一对曲线图。在这种情况下,当弱开关导通时,出现小的浪涌电流峰值,其远低于定义的安全阈值。然而,当随后强开关导通时,出现大的浪涌电流峰值,其可能远高于期望的安全阈值。发生大的峰值电流是因为弱开关太少而无法在强开关导通之前对内部功率轨(vdd)充分充电。

32.图1b示出了对于弱开关与强开关的比率太大的情况(换言之,存在太多的弱开关)、内部轨电压vdd和对应的浪涌电流相对于时间的一对类似曲线图。在这种情况下,当弱开关导通时,出现大的浪涌电流峰值,其远高于定义的安全阈值。然而,强开关的随后导通导致浪涌电流峰值远低于定义的安全阈值。

33.图1c示出了对于弱开关与强开关的比率被设置为产生基本上相等的浪涌电流峰值的情况、内部轨电压vdd和对应的浪涌电流的一对类似曲线图。在这种情况下,弱开关的导通导致浪涌电流峰值基本上等于由强开关导通而产生的浪涌电流峰值。在这种情况下,

两个电流峰值可能低于定义的安全阈值,以防止ic的重置和损坏。

34.图2示出了根据本公开的另一方面的用于向ic的一部分(例如,核或模块)210供应功率的示例性功率门控电路200的框图。功率门控电路200包括菊花链链接在一起的弱开关单元的集合(由标有“w”的框表示)。弱开关单元w响应于使能信号wk_en(在下文中称为弱使能信号wk_en,因为它被施加到弱开关单元)而选择性地将端子功率轨(tvdd)耦合到内部功率轨(vdd)。

35.弱使能信号wk_en直接施加到第一弱开关单元w(如图所示的最低的一个)并且沿着菊花链传播到其他弱开关单元。因此,当生成(例如,断言)弱使能信号wk_en时,第一弱开关单元导通,接着是下一弱开关单元,依此类推,直到最后的弱开关单元导通。如本文中进一步详细讨论的,每个弱开关单元w包括缓冲器(例如,一对级联反相器),其产生通过每个弱开关单元w的弱使能信号wk_en的传播延迟。因此,弱开关单元w基于传播的弱使能信号wk_en顺序地将端子功率轨(tvdd)耦合到内部功率轨(vdd)。

36.功率门控电路200还包括菊花链链接在一起的强开关单元的集合(由标有“s”的框表示)。强开关单元s也基于使能信号st_en(在下文中称为强使能信号st_en,因为它被施加到强开关单元)选择性地将端子功率轨tvdd耦合到内部功率轨vdd。

37.强使能信号st_en直接施加到第一强开关s(如图所示在第一列第三行)并且沿菊花链传播到其他强开关单元。因此,在断言的弱使能信号wk_en已经导通所有弱开关单元w并且初始浪涌电流已经达到峰值并且然后稳定到远低于定义的安全阈值之后,生成(例如,断言)强使能信号st_en,其开始强开关单元s的逐步导通。类似地,每个强开关单元s包括缓冲器(例如,一对级联反相器),其产生通过每个强开关单元s的强使能信号st_en的传播延迟。因此,强开关单元s基于传播的强使能信号st_en顺序地将端子功率轨(tvdd)耦合到内部功率轨(vdd)。所有开关单元(弱和强)的导通满足ic的部分210的总(例如,动态)电流需求。

38.图3示出了根据本公开的另一方面的示例性弱开关单元300的示意图。弱开关单元300是先前讨论的功率门控电路200的任何一个弱开关单元w(诸如第i个弱开关单元)的示例性详细实现。

39.具体地,弱开关单元300包括fet m3(例如,p沟道金属氧化物半导体(pmos)),fet m3的源极耦合到端子功率轨(tvdd)并且漏极耦合到内部功率轨(vdd)。fet m3被配置为相对弱晶体管(例如,其导通电阻高于相对强晶体管m4(下面讨论的)的导通电阻)。

40.弱开关单元300还包括第一反相器i

31

,第一反相器i

31

的输入被配置为接收弱使能信号wk_en(i)并且输出耦合到fet m3的栅极。弱开关单元300还包括第二反相器i

32

,第二反相器i

32

的输入耦合到第一反相器i

31

的输出并且输出被配置为重新生成弱使能信号wk_en(i 1)。如果反相器i

31

是菊花链中的第一单元(i=1),则反相器i

31

直接从源(例如,功率门控控制器)接收弱使能信号wk_en(i),或者如果反相器i

31

不是菊花链中的第一单元(如果i≠1),则反相器i

31

接收由先前的弱开关单元输出的弱使能信号wk_en(i)。反相器i

32

为菊花链中的后续弱开关单元重新生成弱使能信号wk_en(i 1),或者如果反相器i

32

是菊花链中的最后的弱开关单元,则可以不使用反相器i

32

。该对级联反相器i

31

和i

32

产生弱使能信号wk_en的传播延迟。

41.图4示出了根据本公开的另一方面的示例性强开关单元400的示意图。强开关单元

400是先前讨论的功率门控电路200的任何一个强开关单元s(诸如第j个强开关单元)的示例性详细实现。

42.具体地,强开关单元400包括fet m4(例如,pmos),fet m4的源极耦合到端子功率轨(tvdd)并且漏极耦合到内部功率轨(vdd)。fet m4被配置为相对强晶体管(例如,其导通电阻低于弱晶体管m3的导通电阻)。

43.强开关单元400还包括第一反相器i

41

,第一反相器i

41

的输入被配置为接收强使能信号st_en(j)并且输出耦合到fet m4的栅极。强开关单元400还包括第二反相器i

42

,第二反相器i

42

的输入耦合到第一反相器i

41

的输出并且输出被配置为重新生成强使能信号st_en(j 1)。如果反相器i

41

是菊花链中的第一单元(j=1),则反相器i

41

直接从源(例如,功率门控控制器)接收强使能信号st_en(j),或者如果反相器i

41

不是菊花链中的第一单元(如果j≠1),则反相器i

41

接收由先前的强开关单元输出的强使能信号st_en(j)。反相器i

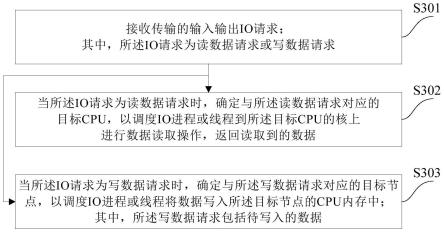

42

为菊花链中的后续强开关单元重新生成强使能信号st_en(j 1),或者如果反相器i

42

是菊花链中的最后的强开关单元,则可以不使用反相器i

42

。该对级联反相器i

41

和i

42

产生强使能信号st_en的传播延迟。

44.功率门控电路200的问题涉及在对应的ic的设计阶段设置弱开关与强开关的适当比率。适当的比率基于功率门控电路200向其供应功率的ic的部分(例如,核或模块)的最终设计。然而,ic部分的最终设计取决于功率门控电路200的最终设计,因为ic部分必须被适当地路由到功率门控电路,并且ic部分操作的定时取决于到功率门控电路的路由。

45.由于这样的依赖性,在过去,弱开关与强开关的比率基于ic部分的预测的最终设计来估计。在设计阶段,所估计的功率门控电路设计然后与所预测的ic部分设计对接,并且进行分析以确定所估计的比率是否导致浪涌电流峰值是可接受的(但是可能不均衡)。如果浪涌电流峰值是可接受的,则最终设计得到批准。

46.然而,如果因为浪涌电流峰值之一超过定义的安全阈值(例如,在需要添加或去除弱开关的情况下)而导致浪涌电流是不可接受的,则需要重新设计功率门控电路。因此,需要重新设计功率门控电路与ic部分之间的路由,并且如果需要,需要重新分析并且重新优化ic部分操作的定时。

47.需要重新设计功率门控电路与ic部分之间的路由的原因在于,弱开关单元300的覆盖区(布局配置)不同于强开关单元400的覆盖区。例如,弱开关单元300包括弱使能信号wk_en传播线,并且强开关单元400包括强使能信号st_en传播线。

48.例如,如果初始比率太小,则需要添加更多弱开关单元,这将使弱使能信号wk_en传播线更长并且强使能信号st_en传播线更短。这会影响ic部分的路由(以及因此影响其定时)。相反,如果初始比率太大,则需要去除一些弱开关单元,这将使弱使能信号wk_en传播线更短并且强使能信号st_en传播线更长。这同样影响ic部分的路由(以及因此影响其定时)。

49.因此,需要一种能够被重新设计或重新配置以设置弱开关与强开关的适当比率、同时不影响最终ic部分设计的路由和定时的功率门控电路。

50.功率门控电路200的另一问题是要求所有弱开关单元w需要在ic的部分210的特定位置中作为一组被菊花链链接。例如,在图2的示例中,弱开关单元w沿着ic部分210的左下区域共同定位。因此,由弱开关单元w导通产生的初始电流必须从左下区域传播并且分散到

整个ic部分210。这导致ic部分210的左下区域中的高浓度电流,这可能导致由于例如电迁移而对ic部分210造成损坏。

51.因此,还需要一种功率门控电路,其包括分布在ic部分的区域上的弱开关(例如,以棋盘图案)。

52.因此,本公开的一个目的是将弱开关单元和强开关单元配置为具有基本上相似的覆盖区(布局配置),以允许在设计阶段热交换强开关单元与弱开关单元(或反之亦然),而不影响ic的要由具有那些单元的功率门控电路向其供应功率的部分的路由和定时。

53.本公开的另一目的是配置弱开关单元和强开关单元,使得它们可以以混合方式菊花链链接在一起。也就是说,菊花链链接在一起的弱开关单元和强开关单元的混合允许在强开关单元之间更灵活地放置弱开关单元;或者,允许在ic区域上更加分布式(例如,棋盘)地放置弱开关单元以减少局部高电流集中;并且因此,降低由于电迁移而损坏ic的可能性。

54.通过弱开关单元的新设计(本文中称为弱强开关单元,因为它能够进行弱耦合和强耦合二者)以及仅强开关单元的新设计来实现上述目的。

55.图5示出了根据本公开的另一方面的示例性弱强开关单元500的示意图。在该示例中,弱强开关单元500可以是功率门控电路的功率开关单元的菊花链中的第k个单元。

56.具体地,弱强开关单元500包括相对强的fet m51(例如,pmos),fet m51的源极耦合到端子功率轨(tvdd)并且漏极耦合到内部功率轨(vdd)。弱强开关单元500包括相对弱的fet m52(例如,pmos),fet m52的源极耦合到端子功率轨(tvdd)并且漏极耦合到内部功率轨(vdd)。

57.弱强开关单元500还包括第一缓冲器510,第一缓冲器510包括第一反相器i

51

,第一反相器i

51

的输入被配置为接收强使能信号st_en(k)并且其输出被耦合到强fet m51的控制端子(栅极)。第一缓冲器510还包括第二反相器i

52

,第二反相器i

52

的输入被耦合到第一反相器i

51

的输出并且输出被配置为重新生成强使能信号st_en(k 1)。

58.如果反相器i

51

是菊花链中的第一单元(k=1),则反相器i

51

直接从源(例如,功率门控控制器)接收强使能信号st_en(k),或者如果反相器i

51

不是菊花链中的第一单元(如果k≠1),则反相器i

51

接收由先前的弱强开关单元或先前的仅强开关单元(取决于紧接在弱强开关单元500之前的单元的类型)输出的强使能信号st_en。反相器i

52

为菊花链中的后续弱强开关单元或后续仅强开关单元重新生成强使能信号st_en(k 1)(取决于紧接在弱强开关单元500之后的单元的类型),或者如果反相器i

52

是菊花链中的最后的单元,则可以不使用反相器i

52

。

59.弱强开关单元500还包括第二缓冲器520,第二缓冲器520包括第三反相器i

53

,第三反相器i

53

的输入被配置为接收弱使能信号wk_en(k)并且其输出被耦合到弱fet m52的控制端子(栅极)。第二缓冲器520还包括第四反相器i

54

,第四反相器i

54

的输入被耦合到弱fet m5的第一反相器i

53

的输出并且输出被配置为重新生成弱使能信号wk_en(k 1)。

60.如果反相器i

53

是菊花链中的第一单元(k=1),则反相器i

53

直接从源(例如,功率门控控制器)接收弱使能信号wk_en(k),或者如果反相器i

53

不是菊花链中的第一单元(如果k≠1),则反相器i

53

接收由先前的弱强开关单元或先前的仅强开关单元(取决于紧接在弱强开关单元500之前的单元的类型)输出的弱使能信号wk_en(k)。反相器i

54

为菊花链中的后续弱强开关单元或后续仅强开关单元重新生成弱使能信号wk_en(k 1)(取决于紧接在弱强开

关单元500之后的单元的类型),或者如果反相器i

54

是菊花链中的最后的弱开关,则可以不使用反相器i

54

。

61.在操作中,当断言的弱使能信号wk_en(k)(例如,处于高逻辑电压电平(例如,tvdd))传播到弱强开关单元500时,断言的弱使能信号wk_en(k)在将功率轨耦合在一起的第一阶段(时间间隔)期间导通弱fet m52以将端子功率轨(tvdd)弱耦合到内部功率轨(vdd),如前所述。当断言的强使能信号st_en(k)(例如,处于高逻辑电压电平(例如,tvdd))随后传播到弱强开关单元500时,断言的强使能信号st_en(k)在将功率轨耦合在一起的第二阶段(时间间隔)期间导通强fet m51以将端子功率轨(tvdd)强耦合到内部功率轨(vdd),如前所述。因此,弱强开关单元500在第一耦合阶段用作弱开关并且在第二耦合阶段用作强开关。

62.图6示出了根据本公开的另一方面的示例性仅强开关单元600的示意图。在该示例中,仅强开关单元600可以是功率门控电路的功率开关单元的菊花链中的第一单元。

63.具体地,仅强开关单元600包括相对强的fet m61(例如,pmos),fet m61的源极被耦合到端子功率轨(tvdd)并且漏极被耦合到内部功率轨(vdd)。仅强开关单元600包括相对弱的fet m62(例如,pmos),fet m62的源极被耦合到端子功率轨(tvdd)并且漏极被耦合到内部功率轨(vdd)。

64.仅强开关单元600还包括第一缓冲器610,第一缓冲器610包括第一反相器i

61

,第一反相器i

61

的输入被配置为接收强使能信号st_en(l)并且其输出被耦合到强fet m61和弱fet m62两者的控制端子(栅极)。第一缓冲器610还包括第二反相器i

62

,第二反相器i

62

的输入被耦合到第一反相器i

61

的输出并且输出被配置为重新生成强使能信号st_en(l 1)。

65.如果反相器i

61

是菊花链中的第一单元(l=1),则反相器i

61

直接从源(例如,功率门控控制器)接收强使能信号st_en(l),或者如果反相器i

61

不是菊花链中的第一单元(如果l≠1),则反相器i

61

接收由先前的弱强开关或先前的仅强开关(取决于紧接在仅强开关单元600之前的单元的类型)输出的强使能信号st_en(l)。反相器i

62

为菊花链中的后续弱强开关单元或后续仅强开关单元重新生成强使能信号st_en(l 1)(取决于紧接在仅强开关单元600之后的单元的类型),或者如果反相器i

62

是菊花链中的最后的单元,则可以不使用反相器i

62

。

66.仅强开关单元600还包括第二缓冲器620,第二缓冲器620包括第三反相器i

63

,第三反相器i

63

的输入被配置为接收弱使能信号wk_en(l)并且其输出被耦合到第四反相器i

64

的输入,第三反相器i

63

的输入也是第二缓冲器620的输入。第四反相器i

64

又包括被配置为重新生成弱使能信号wk_en(l 1)的输出。

67.如果反相器i

63

是菊花链中的第一单元(l=1),则反相器i

63

直接从源(例如,功率门控控制器)接收弱使能信号wk_en(l),或者如果反相器i

63

不是菊花链中的第一单元(如果l≠1),则反相器i

63

接收由先前的弱强开关或先前的仅强开关(取决于紧接在仅强开关单元600之前的单元的类型)输出的弱使能信号wk_en(l)。反相器i

64

为菊花链中的后续弱强开关单元或后续仅强开关单元重新生成弱使能信号wk_en(l 1)(取决于紧接在仅强开关单元600之后的单元的类型),或者如果反相器i

64

是菊花链中的最后的弱开关,则可以不使用反相器i

64

。

68.在操作中,断言的弱使能信号wk_en(例如,处于高逻辑电压电平(例如,tvdd))传

播通过仅强开关单元600而不影响强和弱fet m61和m62的操作。因此,仅强开关单元600仅是弱使能信号wk_en(l)的延迟元件或通路。因此,仅强开关600可以仅用在将端子功率轨(tvdd)耦合到内部功率轨(vdd)的第二阶段中。

69.当断言的强使能信号st_en(l)(例如,处于高逻辑电压电平(例如,tvdd))传播到仅强开关单元600时,断言的强使能信号st_en(l)在将功率轨耦合在一起的第二阶段期间导通强fet m61和弱fet m62两者以将端子功率轨(tvdd)强耦合到内部功率轨(vdd),如前所述。

70.如本文中更详细讨论的,由于弱强开关单元500和仅强开关单元600的配置几乎相同,因此可以使对应的覆盖区(布局配置)基本上相同。也就是说,从输入输出的角度来看,弱强开关单元500与仅强开关单元600相同。例如,单元500和600都包括用于接收强使能信号st_en的第一输入、用于产生重新生成的强使能信号st_en的第一输出、用于耦合到端子功率轨(tvdd)的第二输入和用于耦合到内部功率轨(vdd)的第二输出、以及用于接收弱使能信号wk_en的第三输入和用于产生重新生成的弱使能信号wk_en的第三输出。

71.因此,在功率门控电路的设计阶段,可以将仅强开关单元600“热交换”成弱强开关单元500(或反之亦然),同时设计功率门控电路以实现弱开关与强开关的适当比率,而不需要对ic的要由功率门控电路供应功率的部分(例如,核或模块)进行重新路由和/或定时分析。

72.此外,因为弱强开关单元500和仅强开关单元600具有相同的输入和输出配置,所以弱强开关单元500和仅强开关单元600可以菊花链链接在一起。这允许根据需要以更灵活的方式将弱开关和强开关放置在ic区域上。例如,弱强开关单元500可以以棋盘图案分布在被供应功率的对应的核或模块的整个区域上。

73.图7示出了根据本公开的另一方面的示例性弱强开关单元700的覆盖区(布局配置)的俯视图。弱强开关单元700的布局配置可以是先前讨论的弱强开关单元500的布局配置的示例。

74.如图所示,弱强开关单元700包括用作弱强开关单元700的功率轨(vss)710(例如,地)的顶部和底部水平金属化迹线。经由内部金属化迹线(由虚线表示),功率轨(vss)710可以被耦合到在反相器i

51

、i

52

、i

53

和i

54

中使用的n沟道金属氧化物半导体(nmos)fet(未示出)的源极。

75.弱强开关单元700还包括用作内部功率轨(vdd)的中央水平金属化迹线730。经由内部金属化迹线,内部功率轨(vdd)耦合到弱fet和强fet m51和m52的漏极。而且,经由内部金属化迹线,内部功率轨(vdd)耦合到在i

51

、i

52

、i

53

和i

54

中使用的pmos fet(未示出)的源极。

76.弱强开关单元700还包括用作端子功率轨(tvdd)的一对水平金属化迹线720。该对金属化迹线720中的一个位于顶部功率轨(vss)金属化迹线710与内部功率轨(vdd)金属化迹线730之间。该对金属化迹线720中的另一个位于底部功率轨(vss)金属化迹线710与内部功率轨(vdd)金属化迹线730之间。经由内部金属化迹线,端子功率轨(tvdd)耦合到弱和强fet m51和m52的源极。

77.弱强开关单元700还包括用于接收强使能信号st_en(k)的金属化迹线740和用于产生重新生成的强使能信号st_en(k 1)的金属化迹线750。经由内部金属化迹线,强使能信

号st_en(k)被耦合到反相器i

51

的对应的pmos和nmos的栅极。经由内部金属化迹线,反相器i

51

的pmos和nmos的漏极被耦合到强fet m51的控制端子(栅极)。经由内部金属化迹线,反相器i

52

的pmos和nmos的栅极耦合到反相器i

51

的pmos和nmos的漏极。而且,重新生成的强使能信号st_en(k 1)在反相器i

52

的pmos和nmos的漏极处产生。

78.类似地,弱强开关单元700还包括用于接收弱使能信号wk_en(k)的金属化迹线760和用于产生重新生成的弱使能信号wk_en(k 1)的金属化迹线770。经由内部金属化迹线,弱使能信号wk_en(k)被耦合到反相器i

53

的对应的pmos和nmos的栅极。经由内部金属化迹线,反相器i

53

的pmos和nmos的漏极被耦合到弱fet m52的控制端子(栅极)。经由内部金属化迹线,反相器i

54

的pmos和nmos的栅极被耦合到反相器i

53

的pmos和nmos的漏极。而且,重新生成的弱使能信号wk_en(k 1)在反相器i

54

的pmos和nmos的漏极处产生。

79.图8示出了根据本公开的另一方面的示例性仅强单元800的覆盖区(布局配置)的俯视图。仅强开关单元800的布局配置可以是先前讨论的仅强开关单元600的布局配置的示例。

80.如图所示,仅强开关单元800包括用作仅强开关单元800的功率轨(vss)810(例如,地)的顶部和底部水平金属化迹线。经由内部金属化迹线(由虚线表示),功率轨(vss)810可以被耦合到在反相器i

61

、i

62

、i

63

和i

64

中使用的nmos fet(未示出)的源极。

81.仅强开关单元800还包括用作内部功率轨(vdd)的中央水平金属化迹线830。经由内部金属化迹线,内部功率轨(vdd)被耦合到弱fet和强fet m61和m62的漏极。而且,经由内部金属化迹线,内部功率轨(vdd)被耦合到在i

61

、i

62

、i

63

和i

64

中使用的pmos fet(未示出)的源极。

82.仅强开关单元800还包括用作端子功率轨(tvdd)的一对水平金属化迹线820。该对金属化迹线820中的一个位于顶部功率轨(vss)金属化迹线810与内部功率轨(vdd)金属化迹线830之间。该对金属化迹线820中的另一个位于底部功率轨(vss)金属化迹线810与内部功率轨(vdd)金属化迹线830之间。经由内部金属化迹线,端子功率轨(tvdd)被耦合到弱和强fet m61和m62的源极。

83.仅强开关单元800还包括用于接收强使能信号st_en(l)的金属化迹线840和用于产生重新生成的强使能信号st_en(l 1)的金属化迹线850。经由内部金属化迹线,强使能信号st_en(l)被耦合到反相器i

61

的pmos和nmos的栅极。经由内部金属化迹线,反相器i

61

的pmos和nmos的漏极被耦合到强和弱fet m61和m62的控制端子(栅极)。经由内部金属化迹线,反相器i

62

的pmos和nmos的栅极被耦合到反相器i

61

的pmos和nmos的漏极。而且,重新生成的强使能信号st_en(l 1)在反相器i

62

的pmos和nmos的漏极处产生。

84.类似地,仅强开关单元800还包括用于接收弱使能信号wk_en(l)的金属化迹线860和用于产生重新生成的弱使能信号wk_en(l 1)的金属化迹线870。经由内部金属化迹线,弱使能信号wk_en(l)被耦合到反相器i

63

的pmos和nmos的栅极。经由内部金属化迹线,反相器i

64

的pmos和nmos的栅极被耦合到反相器i

63

的pmos和nmos的漏极。而且,重新生成的弱使能信号wk_en(l 1)在反相器i

64

的pmos和nmos的漏极处产生。

85.弱强开关单元700的覆盖区(布局配置)与仅强开关单元800的覆盖区(布局配置)的比较表明两个单元基本上相同。例如,从输入和输出的角度来看,单元700和800相同。也就是说,单元700和800都包括:用于功率轨(vss)的相同配置的金属化迹线710和810;用于

端子功率轨(tvdd)的相同配置的金属化迹线820;用于内部功率轨(vdd)的相同配置的金属化迹线830;用于接收强使能信号st_en(k)和st_en(l)的相同配置的金属化迹线;用于产生重新生成的强使能信号st_en(k 1)和st_en(l 1)的相同配置的金属化迹线;用于接收弱使能信号wk_en(k)和wk_en(l)的相同配置的金属化迹线;以及用于产生重新生成的弱使能信号wk_en(k 1)和wk_en(l 1)的相同配置的金属化迹线。

86.因此,在功率门控电路的设计阶段中将弱强开关单元700替换(“热交换”)为仅强开关单元800或者反之亦然不会影响功率门控电路与ic的由功率门控电路供应功率的部分之间的路由。

87.此外,弱强开关单元700和仅强开关单元800的大小和布局基本上类似,在它们各自的内部金属化迹线中具有以下微小差异:(1)在弱强开关单元700中,内部金属化迹线分别将反相器i

51

和i

53

的输出电连接到fet m51和m52的栅极;(2)在仅强开关单元800中,内部金属化迹线仅将反相器i

61

的输出电连接到fet m61和m62的栅极(而不是将反相器i

63

的输出电连接到fet m61和m62的栅极)。

88.因为单元700和800的大小和布局基本上相似,所以从单元所连接的ic部分的角度来看,它们表现出基本上相同的寄生电抗。因此,在功率门控电路的设计阶段中将弱强开关单元700替换(“热交换”)为强开关单元800或者反之亦然不会影响ic的由功率门控电路供应功率的部分的定时操作。

89.图9示出了根据本公开的另一方面的用于ic的部分910(例如,核或模块)的示例性功率门控电路900的示意图。功率门控电路900包括具有弱强开关单元ws和仅强开关单元s的混合的菊花链。每个弱强开关单元ws可以被配置为类似于先前讨论的弱强开关单元500和/或700。每个仅强开关单元s可以被配置为类似于先前讨论的仅强开关单元600和/或800。

90.单元ws和s中的每个耦合在端子功率轨(tvdd)与内部功率轨(vdd)之间。每个单元ws和s接收强使能信号st_en和弱使能信号wk_en,如果其为菊花链中的第一单元,则从功率门控控制器920接收,或者如果其不是菊花链中的第一单元,则从前一单元接收。除了菊花链中的最后的开关单元之外,每个单元ws和s将强使能信号st_en和弱使能信号wk_en传递到菊花链中的后续单元。

91.在该示例中,功率门控电路900包括总共100个开关单元s和ws。在100个单元中,有90个仅强开关单元s和10个弱强开关单元ws。选择单元总数(例如,100个单元)以满足ic部分910的总电流需求(例如,动态电流需求)。在该示例中,弱开关与强开关的比率是10%。同样,如所讨论的,选择该比率以基本上均衡由于弱开关的导通然后是强开关的导通而导致的浪涌电流峰值。

92.此外,在该示例中,菊花链中的第一单元是弱强单元ws。因此,强使能信号st_en和wk_en被施加到该第一弱强单元ws。在菊花链中的第一单元之后,在遇到另一弱强开关单元ws之前,存在一系列仅强单元(例如,九(9)个)。该菊花链配置(一(1)个弱强开关单元ws,然后是九(9)个仅强开关单元s)在功率门控电路900中重复10次以实现总共100个开关单元,其中的10个是弱强开关单元ws并且其中的90个是仅强开关单元s。

93.如图所示,弱强开关单元ws基本上分布在ic的部分910的整个区域上。这降低了在所有弱开关单元共同位于特定区域中(诸如在先前讨论的功率门控电路200中)的情况下将

会产生的电流集中。

94.在操作中,响应于接收到对ic的部分910上电的命令,功率门控控制器920生成(例如,断言)弱使能信号(wk_en)(例如,将信号wk_en设置为逻辑高电压电平(例如,tvdd))。断言的弱使能信号wk_en在其传播通过菊花链时遇到每个弱强开关单元ws时逐渐导通弱fet m52。仅强单元s未响应于断言的弱使能信号wk_en而导通,因为仅强单元仅使信号通过。弱强单元ws的导通将端子功率轨(tvdd)逐渐耦合到内部功率轨(vdd),以将浪涌电流峰值限制到低于限定的安全阈值。

95.在弱使能信号wk_en的断言的定义的时间间隔(例如,第一浪涌电流稳定到低于定义的安全阈值的定义水平的足够的时间间隔)之后,功率门控控制器920生成(例如,断言)强使能信号st_en(例如,将信号st_en设置为逻辑高电压电平(例如,tvdd))。断言的强使能信号st_en在其传播通过菊花链时遇到每个弱强开关单元ws时逐渐导通强fet m51,并且在其传播通过菊花链时遇到每个仅强开关单元s时逐渐导通强和弱fet m61和m62。由于已经通过响应于断言的弱使能信号wk_en导通弱强开关单元ws中的弱fet m52而对内部功率轨(vdd)进行了预充电,因此仅强单元s的导通将端子功率轨(tvdd)逐渐且完全地耦合到内部功率轨(vdd),使得第二浪涌电流峰值也低于定义的安全阈值。

96.图10示出了根据本公开的另一方面的用于向ic的部分1010(例如,核或模块)供应功率的示例性功率门控电路1000的示意图。功率门控电路1000包括具有90个仅强开关单元s和10个弱强开关单元ws的混合的菊花链。如图所示,10个弱强开关单元ws以均匀组(左下侧)菊花链链接在一起,并且剩余的仅强开关单元s在弱强开关ws之后以均匀组菊花链链接。这是为了说明可以根据需要在ic的部分1010的整个区域上放置弱强开关单元ws和仅强开关s。

97.上电操作类似于功率门控电路900的上电操作。响应于接收到对ic的部分1010上电的命令,功率门控控制器1020生成(例如,断言)弱使能信号wk_en,这引起弱强开关单元ws的弱fet m52将端子功率轨(tvdd)逐渐地耦合到内部功率轨(vdd)。然后,在弱使能信号wk_en的断言的限定时间间隔之后,功率门控控制器1020生成(例如,断言)强使能信号st_en,这引起弱强开关单元wk和仅强单元的强fet m51和m61(以及仅强开关单元s的弱fet m62)进一步将端子功率轨(tvdd)逐渐地耦合到内部功率轨(vdd)。

98.图11示出了根据本公开的另一方面的设计功率门控电路的示例性方法1100的流程图。方法1100包括确定用于功率门控电路设计的开关单元的总数(框1102)。开关单元的总数可以基于ic的功率门控电路将向其供应功率的部分(例如,核或模块)的总电流需求(例如,动态电流)来确定。

99.另外,方法1100包括确定用于功率门控电路设计的弱开关与强开关的估计的比率(框1104)。如前所述,该比率可以取决于各种因素,包括功率门控电路将向其供应功率的ic部分的大小、电路密度和路由拥塞。可以使用设计工具来确定这样的估计的比率。如前所述,估计弱开关与强开关的比率,以便实现低于限定的安全阈值的基本上均衡的浪涌电流峰值。

100.然后,方法1100还需要通过基于估计的比率用弱强开关单元ws和仅强开关单元s填充单元槽来生成功率门控电路的初步设计(框1106)。例如,如果估计的比率是10%并且在功率门控电路设计中总共有100个开关单元,则用弱强开关单元ws填充10个单元槽,并且

用仅强源开关单元s填充90个单元槽。为了实现在仅强开关单元s之间的弱强开关单元ws的平衡分布,可以用弱强开关单元ws填充每第10个槽。功率门控电路的初步设计可以是用于生成用于制造ic的掩模的格式,诸如全球数据库系统ii(gdsii)格式、oasis等。

101.然后,根据方法1100,完成将由功率门控电路供应功率的ic部分(例如,核或模块)的设计(框1108)。这可能需要设计功率门控电路与ic部分之间的路由以及基于所设计的路由执行定时分析和优化。

102.方法1100还包括通过用仅强开关单元s填充所有单元槽来生成功率门控电路的临时设计(框1110)。然后,根据方法1100,基于ic的部分(例如,核或模块)的最终设计来确定弱开关与强开关的最终比率(框1112)。最终比率可以与在框1104中确定的估计的比率不同。

103.然后,根据方法1100,基于最终比率,将一些仅强开关单元s替换(“热交换”)为弱强开关单元ws(框1114)。例如,如果最终比率是九(9),则为了实现在仅强开关单元s之间的弱强开关单元ws的平衡分布,每第9仅强开关单元被“热交换”为弱强开关单元ws。因为两种类型的开关单元s和ws都是覆盖区兼容的,所以仅强开关单元s与弱强开关单元ws的热交换不会影响ic的部分(例如,核或模块)的路由或定时操作。

104.提供先前对本发明的描述是为了使得所属领域的技术人员能够制作或使用本发明。对于本领域技术人员来说,对本公开的各种修改是很清楚的,并且在不脱离本公开的精神或范围的情况下,本文中定义的一般原理可以应用于其他变型。因此,本公开不旨在限于本文中描述的示例,而是与符合与本文中公开的原理和新颖特征相一致的最宽范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。