交流/直流快充系统及用于其的快充协议芯片

1.本技术是申请日为2020年12月31日、申请号为202023322568.5、且发明名称为“交流/直流快充系统及用于其的快充协议芯片”的专利申请的分案申请。

技术领域

2.本实用新型涉及电路领域,更具体地涉及一种交流/直流快充系统及用于其的快充协议芯片。

背景技术:

3.在交流/直流(ac/dc)快充系统中,由于输出电压的档位多、步进小,为了能输出精确的恒压/恒流(cv/cc),通常在变压器的副边侧进行恒压/恒流(cv/cc)环路补偿。相对于传统的tl431补偿方式,目前更多的做法是将tl431误差放大器集成在快充协议芯片上,并将tl431补偿电路设置在快充协议芯片外部,以节省快充协议芯片的面积。

4.图1示出了传统的ac/dc快充系统100的系统架构的示意图。如图1所示,ac/dc快充系统100包括设置在变压器t1的原边侧的脉宽调制(pwm)控制芯片102、设置在变压器t1的副边侧的同步整流(sr)控制芯片104、以及设置在变压器t1的副边侧的快充协议芯片106,其中:pwm控制芯片102用于控制功率管p1的导通和关断;sr控制芯片104及其控制的场效应晶体管用于代替肖特基二极管实现同步整流功能,可以大大提高ac/dc快充系统100的充电效率;快充协议芯片106集成了快充协议和恒压/恒流环路的误差放大器部分,而恒压/恒流环路的补偿电路设置在快充协议芯片106外部。

5.当图1所示的ac/dc快充系统100工作时,快充协议芯片106通过通讯脚cc1/cc2/dp/dn与被充电设备进行通讯,并且通讯脚cc1/cc2/dp/dn被提供以不同的电压/电流/功率。具体地,快充协议芯片106通过通讯脚cc1/cc2或者dp/dn与被充电设备通讯,告知被充电设备ac/dc快充系统100支持的电压、电流、以及功率等信息,同时可以响应被充电设备要求的电压和电流等控制要求。

6.图2示出了用在图1所示的ac/dc快充系统100中的反激式控制架构的示意图。如图2所示,变压器t1的原边电感np和副边电感nsec为异名端;在功率管p1导通期间,原边电感np储存能量;在功率管p1关断期间,原边电感np将储存的能量传递到副边电感nsec,副边电感nsec退磁并将能量提供给负载ro。

7.图3示出了用在图1所示的ac/dc快充系统100中的快充协议芯片106的内部架构的示意图。如图3所示,快充协议芯片106包括恒压放大器和恒流放大器,它们的工作原理如下:在恒压工作模式下,恒流放大器处于开环状态,恒压放大器将ac/dc快充系统100的输出电压vo经由片外分压电阻rup和rdn分压得到的分压值vo_div(由电压采样脚vfb输入快充协议芯片106)与内部恒压基准电压vref_cv进行比较,将两者的误差通过误差放大器cv_ea的放大后送到漏极开路结构的n型金属-氧化物-半导体(nmos)晶体管nm_cv转换成光耦电流,将信号传递给变压器t1的原边侧的pwm控制芯片102的反馈脚fb从而将ac/dc快充系统100的输出电压vo调节到设定值;在恒流工作模式下,恒压放大器处于开环状态,恒流放大

器将ac/dc快充系统100的输出电流的采样放大值vcs_amp与内部恒流基准电压vref_cc进行比较,将两者的误差通过误差放大器cc_ea的放大后送到漏极开路结构的nmos晶体管nm_cc转换成光耦电流,将信号传递给变压器t1的原边侧的pwm控制芯片102的反馈脚fb从而将ac/dc快充系统100的输出电流调节到设定值。

8.在图1所示的ac/dc快充系统100中,恒流放大器和恒压放大器的补偿电路均设置在快充协议芯片106外部,即恒压放大器的补偿电路跨接在快充协议芯片106的光耦驱动脚opto和电压采样脚vfb之间,恒流放大器的补偿电路跨接在快充协议芯片106的光耦驱动脚opto和电流采样放大脚ifb之间。

9.跨接在快充协议芯片106的光耦驱动脚opto和电压采样脚vfb之间的r1、c1(即,恒压放大器的补偿电路)为恒压环路提供了一个主极点ω

pd1

和一个前馈零点ω

z1

,即:

[0010][0011][0012]

跨接在快充协议芯片106的光耦驱动脚opto和电流采样放大脚ifb之间的r2、c2(即,恒流放大器的补偿电路)为恒流环路提供了一个主极点ω

pd2

和一个前馈零点ω

z2

,即:

[0013][0014][0015]

在上述等式(1)~(4)中,acv、acc分别为恒压放大器和恒流放大器的直流增益,rup和rdn为用于对ac/dc快充系统100的输出电压vo进行分压的片外分压电阻的阻值,rint cc为恒流放大器中的误差放大器cc_ea的输入阻抗,r1和r2为设置在快充协议芯片106外部的补偿电阻的阻值,c1和c2为设置在快充协议芯片106外部的补偿电容的容量。

[0016]

从结合图1至图3的描述可以看出,传统的ac/dc快充系统100存在外围元件多、系统成本高的问题。

技术实现要素:

[0017]

鉴于以上所述的一个或多个问题,本实用新型提供了一种用于交流/直流快充系统的快充协议芯片和交流/直流快充系统。

[0018]

根据本实用新型实施例的用于交流/直流快充系统的快充协议芯片,包括恒压放大器和恒压补偿电路,其中:恒压放大器的第一端子与快充协议芯片中的第一数模转换器的输出端连接,第二端子与恒压补偿电路的第一端子连接,第三端子与恒压补偿电路的第二端子连接,第四端子与快充协议芯片的芯片供电脚连接,第五端子与快充协议芯片的光耦驱动脚连接;恒压补偿电路的第一端子与恒压放大器的第二端子连接,第二端子与恒压放大器的第三端子连接,第三端子与快充协议芯片的电压输入脚连接,第四端子接地。

[0019]

根据本实用新型实施例的用于交流/直流快充系统的快充协议芯片,包括恒流放大器和恒流补偿电路,其中:恒流放大器的第一端子与快充协议芯片中的第二数模转换器的输出端连接,第二端子与快充协议芯片中的电压放大器的输出端和恒流补偿电路的第一

端子连接,第三端子与恒流补偿电路的第二端子连接,第四端子与快充协议芯片的芯片供电脚连接,第五端子与快充协议芯片的光耦驱动脚连接;恒流补偿电路的第一端子与恒流放大器的第二端子连接,第二端子与恒流放大器的第三端子连接。

[0020]

根据本实用新型实施例的快充协议芯片集成了恒压环路和恒流环路中的至少一者。因此,包括根据本实用新型实施例的快充协议芯片的交流/直流快充系统可以输出精确的恒压/恒流,并且印刷电路板布局简单、系统成本低。

[0021]

根据本实用新型实施例的交流/直流快充系统,包括上述快充协议芯片,其中,光耦二极管连接在快充协议芯片的光耦驱动脚和地之间。

[0022]

根据本实用新型实施例的交流/直流快充系统由于采用了光耦到地的运放跨接补偿方式,快充协议芯片中的恒压补偿电路和恒流补偿电路可以跨接在低压域内并且其中的补偿电容无需耐受高压,因此可以提高快充协议芯片的可靠性同时相对地节省其芯片面积。

附图说明

[0023]

从下面结合附图对本实用新型的具体实施方式的描述中可以更好地理解本实用新型,其中:

[0024]

图1示出了传统的ac/dc快充系统的系统架构的示意图;

[0025]

图2示出了用在图1所示的ac/dc快充系统中的反激式控制架构的示意图;

[0026]

图3示出了用在图1所示的ac/dc快充系统中的快充协议芯片的内部架构的示意图;

[0027]

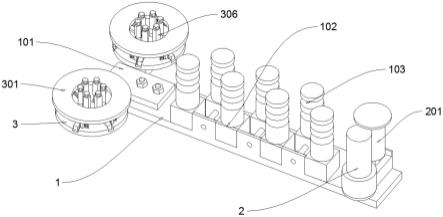

图4示出了根据本实用新型实施例的ac/dc快充系统的示例系统架构的示意图;

[0028]

图5示出了用在图4所示的ac/dc快充系统中的快充协议芯片的示例内部框架的示意图。

具体实施方式

[0029]

下面将详细描述本实用新型的各个方面的特征和示例性实施例。在下面的详细描述中,提出了许多具体细节,以便提供对本实用新型的全面理解。但是,对于本领域技术人员来说很明显的是,本实用新型可以在不需要这些具体细节中的一些细节的情况下实施。下面对实施例的描述仅仅是为了通过示出本实用新型的示例来提供对本实用新型的更好的理解。本实用新型决不限于下面所提出的任何具体配置,而是在不脱离本实用新型的精神的前提下覆盖了元素和部件的任何修改、替换和改进。在附图和下面的描述中,没有示出公知的结构和技术,以便避免对本实用新型造成不必要的模糊。另外,需要说明的是,这里使用的用语“a与b连接”可以表示“a与b直接连接”也可以表示“a与b经由一个或多个其他元件间接连接”。

[0030]

鉴于传统的ac/dc快充系统存在的一个或多个问题,本实用新型提出了一种ac/dc快充系统及用于其的快充协议芯片。

[0031]

图4示出了根据本实用新型实施例的ac/dc快充系统100’的示例系统架构的示意图。如图4所示,ac/dc快充系统100’包括设置在变压器t1的原边侧的脉宽调制(pwm)控制芯片102、设置在变压器t1的副边侧的同步整流(sr)控制芯片104、以及设置在变压器t1的副

边侧的快充协议芯片106’,其中:pwm控制芯片102用于控制功率管p1的导通和关断;sr控制芯片104及其控制的场效应晶体管用于代替肖特基二极管实现同步整流功能,可以大大提高ac/dc快充系统100’的充电效率;快充协议芯片106’集成了快充协议和恒压/恒流环路,用于根据快充协议向被充电设备提供恒压/恒流。

[0032]

相比传统的ac/dc快充系统100,图4示出的ac/dc快充系统100’的不同包括:1)恒压/恒流环路的误差放大器部分和补偿电路均设置在快充协议芯片106’内部,所以省去了连接到快充协议芯片106’的电压采样脚vfb和电流采样放大脚ifb的外围元件;2)光耦二极管连接在快充协议芯片106’的光耦驱动脚opto和地之间,即采用了光耦对地的运放跨接补偿方式。

[0033]

图5示出了用在图4所示的ac/dc快充系统100’中的快充协议芯片106’的示例内部框架的示意图。如图5所示,快充协议芯片106’包括恒压放大器和恒压补偿电路,其中:恒压放大器的第一端子与快充协议芯片106’中的第一数模转换器的输出端连接,第二端子与恒压补偿电路的第一端子连接,第三端子与恒压补偿电路的第二端子连接,第四端子与快充协议芯片106’的芯片供电脚vdd连接,第五端子与快充协议芯片106’的光耦驱动脚opto连接;恒压补偿电路的第一端子与恒压放大器的第二端子连接,第二端子与恒压放大器的第三端子连接,第三端子与快充协议芯片106’的电压输入脚vin连接,第四端子接地。

[0034]

在一些实施例中,如图5所示,快充协议芯片106’可以包括恒流放大器和恒流补偿电路,其中:恒流放大器的第一端子与快充协议芯片106’中的第二数模转换器的输出端连接,第二端子与快充协议芯片106’中的电压放大器的输出端和恒流补偿电路的第一端子连接,第三端子与恒流补偿电路的第二端子连接,第四端子与快充协议芯片106’的芯片供电脚vdd连接,第五端子与快充协议芯片106’的光耦驱动脚opto连接;恒流补偿电路的第一端子与恒流放大器的第二端子连接,第二端子与恒流放大器的第三端子连接。

[0035]

在一些实施例中,如图5所示,恒压放大器包括误差放大器cv_ea、运算放大器op_cv、以及源极跟随结构的nmos晶体管nm_cv,其中:误差放大器cv_ea的第一端子作为恒压放大器的第一端子,第二端子作为恒压放大器的第二端子,第三端子作为恒压放大器的第三端子;运算放大器op_cv的第一端子与快充协议芯片106’中的第一基准电压vcm_cv连接,第二端子与误差放大器cv_ea的第三端子连接,第三端子与源极跟随结构的nmos晶体管nm_cv的第一端子连接;源极跟随结构的nmos晶体管nm_cv的第一端子与运算放大器op_cv的第三端子连接,第二端子作为恒压放大器的第四端子,第三端子作为恒压放大器的第五端子。

[0036]

在一些实施例中,如图5所示,恒压补偿电路包括第一电阻-电容电路(即,由补偿电阻r1’和补偿电容c1’串联而成的rc电路)和分压电路(即,由分压电阻rup’和rdn’串联而成的分压电路),其中:第一电阻-电容电路的第一端子与分压电路的第一端子连接并且作为恒压补偿电路的第一端子,第二端子作为恒压补偿电路的第二端子;分压电路的第一端子与第一电阻-电容电路的第一端子连接并且作为恒压补偿电路的第一端子,第二端子作为恒压补偿电路的第三端子,第三端子作为恒压补偿电路的第四端子。

[0037]

在一些实施例中,如图5所示,恒流放大器包括误差放大器cc_ea、运算放大器op_cc、以及源极跟随结构的nmos晶体管nm_cc,其中:误差放大器cc_ea的第一端子作为恒流放大器的第一端子,第二端子作为恒流放大器的第二端子,第三端子作为恒流放大器的第三端子;运算放大器op_cc的第一端子与快充协议芯片106’中的第二基准电压vcm_cc连接,第

二端子与误差放大器cc_ea的第三端子连接,第三端子与源极跟随结构的nmos晶体管nm_cc的第一端子连接;源极跟随结构的nmos晶体管nm_cc的第一端子与运算放大器op_cc的第三端子连接,第二端子作为恒流放大器的第四端子,第三端子作为恒流放大器的第五端子。

[0038]

在一些实施例中,如图5所示,恒流补偿电路包括第二电阻-电容电路(即,由补偿电阻r2’和补偿电容c2’串联而成的rc电路),其中:第二电阻-电容电路的第一端子作为恒流补偿电路的第一端子,第二端子作为恒流补偿电路的第二端子。

[0039]

结合图1、图3、图4、以及图5可以看出,在传统的ac/dc快充系统100中设置在快充协议芯片106外围的补偿电阻r1和r2、补偿电容c1和c2、以及分压电阻rup和rdn已经转换为图5中的补偿电阻r1’和r2’、补偿电容c1’和c2’、以及分压电阻rup’和rdn’。由于相比传统的ac/dc快充系统100,图5中仍然采用了运放跨接补偿架构,所以图5所示的补偿电路的主极点和前馈零点与等式(1)~(4)表示的相应主极点和前馈零点类似。

[0040]

补偿电阻r1’和补偿电容c1’为恒压环路提供了一个主极点ω

pd1

‘

和一个前馈零点ω

z1

‘

,即:

[0041][0042][0043]

补偿电阻r2’和补偿电容c2’为恒流环路提供了一个主极点ω

pd2

‘

和一个前馈零点ω

z2’,即:

[0044][0045][0046]

在上述等式(5)~(8)中,acv、acc分别为恒压放大器和恒流放大器的直流增益,rup’和rdn’为恒压补偿电路中的分压电阻的阻值,rintcc’为恒流放大器中的误差放大器cc_ea的输入阻抗,r1’和r2’分别为恒压补偿电路和恒流补偿电路中的补偿电阻的阻值,c1’和c2’分别为恒压补偿电路和恒流补偿电容中的补偿电容的容量。等式(5)~(8)中的主极点和前馈零点与等式(1)~(4)中的相应主极点和前馈零点是相等的。

[0047]

如图5所示,在快充协议芯片106’中,在误差放大器cv_ea和源极跟随结构的nmos晶体管nm_cv之间增加了运算放大器op_cv作为第一信号反相级,在误差放大器cc_ea和源极跟随结构的nmos晶体管nm_cc之间增加了运算放大器op_cc作为第二信号反相级,并且分别使用源极跟随结构的nmos晶体管nm_cv和源极跟随结构的nmos晶体管nm_cc进行输出,这使得恒压环路和恒流环路的控制互不影响、平滑切换。

[0048]

另外,如图4和图5所示,由于光耦二极管连接在快充协议芯片106’的光耦驱动脚opto和地之间,恒压补偿电路和恒流补偿电路均跨接在低压域内,补偿电容c1’和c2’无需耐受高压,因此可以提高快充协议芯片106’的可靠性同时相对地节省其芯片面积(相比补偿电容需要耐受高压的情况)。

[0049]

图5所示的恒压环路和恒流环路的工作原理如下:在恒压工作模式下,源极跟随结构的nmos晶体管nm_cc截止,恒流放大器处于开环状态,ac/dc快充系统100’的输出电压vo’经由分压电阻rup’和rdn’的分压得到的分压值vo_div被送到误差放大器cv_ea的负端(即,

第一误差放大器的第二端子),cv基准电压vref_cv被送到误差放大器cv_ea的正端(即,第一误差放大器的第二端子),它们二者的差值通过误差放大器cv_ea放大后被送到运算放大器op_cv进行电平移位和反相放大,再通过源极跟随结构的nmos晶体管nm_cv转换成下光耦电流,将信号传递给变压器t1的原边侧的pwm控制芯片102的fb脚,来将ac/dc快充系统100’的输出电压vo’调节到设定值;在恒流工作模式下,源极跟随结构的nmos晶体管nm_cv截止,恒压放大器处于开环状态,ac/dc快充系统100’的输出电流的采样放大值vcs_amp’通过电阻rint_cc’被送到误差放大器cc_ea的负端(即,第二误差放大器的第二端子),cc基准电压vref_cc被送到误差放大器cc_ea的正端(即,第二误差放大器的第一端子),它们二者之间的差值通过误差放大器cc_ea放大后被送到运算放大器op_cc进行电平移位和反相放大,再通过源极跟随结构的nmos晶体管nm_cc转换成下光耦电流,将信号传递给变压器t1的原边侧的pwm控制芯片102的fb脚,来将ac/dc快充系统100’的输出电流调节到设定值。

[0050]

这里,运算放大器op_cv和运算放大器op_cc将输入和输出共模电平分别设置在vcm_cv和vcm_cc,在补偿网络中它们除了提供信号反相外,还提供额外直流增益,可以表示如下:

[0051][0052][0053]

实际上,可以针对环路稳定性,系统动态特性,和op_cv、op_cc的输入/输出共模范围进行折中,来合理选择vcm_cv,rf_cv,ri_cv,vcm_cc,rf_cc和ri_cc以达到最优性能。

[0054]

根据本实用新型实施例的快充协议芯片集成了恒压环路和恒流环路中的至少一者。因此,包括根据本实用新型实施例的快充协议芯片的交流/直流快充系统可以输出精确的恒压/恒流,并且印刷电路板布局简单、系统成本低。另外,光耦对地的运放跨接补偿方式使得快充协议芯片中的补偿电容无需耐受高压,因此在不增加芯片面积的基础上,解决了补偿电容的耐压问题,提升了快充协议芯片的可靠性。

[0055]

本实用新型可以以其他的具体形式实现,而不脱离其精神和本质特征。因此,当前的实施例在所有方面都被看作是示例性的而非限定性的,本实用新型的范围由所附权利要求而非上述描述定义,并且,落入权利要求的含义和等同物的范围内的全部改变从而都被包括在本实用新型的范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。