基于并联sic mosfet动静态参数影响下的电流测量系统

技术领域

1.本发明涉及功率半导体器件测试技术领域,具体的说是一种测量并联sic mosfet动静态参数影响电流分布的系统。

背景技术:

2.随着大功率应用以及高精度设备的普及,si mosfet已经不能满足这种需求,sic mosfet器件具有临界击穿场强高、热传导性好、导通电阻小、电子饱和速度更高等优点,因此在电力电子领域中越来越备受瞩目,然而,为了满足大功率应用,单芯片sic mosfet器件不能满足其需求,而大电流的功率半导体模块通常造价更高,因此,一般通过并联sic mosfet来扩大电流容量以达到设计要求。但由于sic mosfet器件的静态参数具有分散性,功率回路、驱动电路以及封装结构的寄生参数具有不对称性,会导致并联器件之间的电流出现不平衡现象,因此,研究动静态参数对并联mosfet电流分布影响,从而进行改进设计来减少电流的不均衡度十分有必要。

技术实现要素:

3.本发明是为了解决上述现有技术存在的不足之处,提出一种基于并联sic mosfet动静态参数影响下的电流测量系统,以期能达到减少并联器件之间出现的电流不平衡现象,从而能通过并联sic mosfet来扩大电流容量以达到设计要求。

4.本发明为达到上述发明目的,采用如下技术方案:

5.本发明一种基于并联sic mosfet动静态参数影响下的电流测量系统,其特征是,所述测量系统包括:功率电路、驱动电路和驱动供电电路;

6.所述功率电路由直流母线侧电路和测量器件电路组成;

7.所述直流母线侧电路包括:直流电源接口、支撑电容以及去耦电容;

8.所述直流电源接口的正极dc 和负极dc-之间并联有所述支撑电容以及去耦电容;其中,支撑电容和去耦电容分别由n1个电容和n2个电容并联而成;

9.所述测量器件电路是由两条相互对称的支路a和支路b并联成的半桥电路,并与所述直流母线侧电路并联;

10.所述支路a和支路b均由上、下半桥串联组成,其中,支路a和支路b的上半桥分别由金属-氧化物半导体场效应晶体管mosfet1和金属-氧化物半导体场效应晶体管mosfet3组成;

11.支路a的下半桥由金属-氧化物半导体场效应晶体管mosfet2和第一电流测量电路串联而组成;

12.所述第一电流测量电路由n个相互并联且阻值相同的电阻r1~rn以及与所述电阻r1~rn并联的mmcx接口rf1组成;

13.所述支路a中的金属-氧化物半导体场效应晶体管mosfet1的漏极与所述正极dc 相连,金属-氧化物半导体场效应晶体管mosfet1的源极和金属-氧化物半导体场效应晶体

管mosfet2的漏极相连;金属-氧化物半导体场效应晶体管mosfet2的源极与所述第一电流测量电路的一端相连;所述第一电流测量电路的另一端与所述负极dc-相连;

14.支路a的金属-氧化物半导体场效应晶体管mosfet1的门极、漏极和源极分别预留有无源器件插口soc1-soc3;支路a的金属-氧化物半导体场效应晶体管mosfet2的门极、漏极和源极分别预留有无源器件插口soc7-soc9;

15.支路b的下半桥由金属-氧化物半导体场效应晶体管mosfet4和第二电流测量电路组成;

16.所述第二电流测量电路由n个相互并联且阻值相同的电阻以及与所述电阻并联的mmcx接口rf2组成;

17.所述支路b中的金属-氧化物半导体场效应晶体管mosfet3的漏极与所述正极dc 相连,金属-氧化物半导体场效应晶体管mosfet3的源极和金属-氧化物半导体场效应晶体管mosfet4的漏极相连;金属-氧化物半导体场效应晶体管mosfet4的源极与所述第二电流测量电路的一端相连;所述第二电流测量电路的另一端与所述负极dc-相连;

18.支路b的金属-氧化物半导体场效应晶体管mosfet3的门极、漏极和源极分别预留有无源器件插口soc4-soc6;支路b的金属-氧化物半导体场效应晶体管mosfet4的门极、漏极和源极分别预留有无源器件插口soc10-soc12,所述无源器件插口用来测量无源器件的不均衡性对并联mosfet电流的影响;

19.所述金属-氧化物半导体场效应晶体管mosfet1~金属-氧化物半导体场效应晶体管mofet4的门极和源极分别与驱动电路相连;

20.所述驱动电路为功率电路中的四个金属-氧化物半导体场效应晶体管提供驱动信号,用于驱动所述功率电路中的四个金属-氧化物半导体场效应晶体管的开通和关断,其中,功率电路的支路a和支路b上、下半桥的金属-氧化物半导体场效应晶体管分别用两个完全相同的驱动电路驱动,所述驱动电路分为两部分完全相同的上半桥驱动电路和下半桥驱动电路,分别驱动功率电路中支路a或支路b上、下半桥的金属-氧化物半导体场效应晶体管;

21.任意一个上半桥驱动电路或下半桥驱动电路是由四部分组成,分别为:信号输入侧、延迟环节、隔离型门极驱动器和输出侧;

22.所述信号输入侧用于将信号pwm输入电路中;

23.所述隔离型门极驱动器由隔离型门极驱动芯片u1d构成,所述隔离型门极驱动芯片u1d左侧从上到下引脚依次为vcc1、gnd1、in1、in2;隔离型门极驱动芯片u1d右侧从上到下引脚依次为vcc2、vee2、out1、out2;

24.所述延迟环节是由肖特基二极管d1、电容c1d与可变电阻器r1组成的rc电路;所述rc电路的可变电阻器r1连接所述隔离型门极驱动芯片u1d的in1引脚;肖特基二极管d1和电容c1d串联后,再与可变电阻器r1并联连接所述隔离型门极驱动芯片u1d的gnd1引脚,所述gnd1引脚连接地;

25.信号输入侧与所述rc电路相连接,其中,电源vd连接所述隔离型门极驱动芯片u1d的vcc 1引脚;电源gnd_top和电容c2d并联后再与电源vcc_top并联连接所述隔离型门极驱动芯片u1d的vcc2引脚;电源gnd_top(s_hs)和电容c3d并联后再与电源vee_top并联连接所述隔离型门极驱动芯片u1d的vee2引脚;由所述驱动供电电路供电;

26.所述输出侧与n3个驱动电阻相并联;n3个驱动电阻分为两部分电阻后分别连接所述隔离型门极驱动芯片u1d的out1引脚和out2引脚;

27.所述驱动供电电路由电压vd发生电路和驱动供电主电路组成;

28.所述电压vd发生电路由外接直流电源vext、稳压器芯片u1s、n4个电容并联的输入侧、n5个电容并联的输出侧组成;

29.所述稳压器芯片u1s的左、右引脚分别为in和out,底部引脚为gnd;

30.所述n4个电容并联的输入侧与外接直流电源vext连接后,再与所述稳压器芯片u1s的左引脚in相连;

31.所述n5个电容并联的输出侧与电压vd连接后,再与所述稳压器芯片u1s的右引脚out相连;in和out引脚并联后与底部引脚gnd连接;

32.所述驱动供电主电路由主电路输入侧、施密特触发器u2s、驱动芯片u3s、变压器tr1与共模电感、肖特基整流二极管和主电路输出侧组成;

33.所述主电路输入侧由电压vd、所述施密特触发器u2s、电阻r3s、电容c8s以及滑动变阻器r2s和电阻r4s构成;

34.所述施密特触发器供电u2s的左侧从上到下引脚分别为vcc、in1、in2;右侧从上到下引脚分别为gnd、out1、out2;

35.所述电压vd与底盘的施密特触发器u2s的左侧引脚vcc连接;电阻r3s的一端与电压vd连接,另一端与所述电容c8s的一端串联后,再与所述施密特触发器u2s的左侧引脚in1连接;所述电容c8s的另一端接地;

36.所述滑动变阻器r2s和电阻r4s串联后的结构与所述电阻r3s和电容c8s串联后的结构并联,构成信号输入部分再连接所述施密特触发器u2s的左侧引脚in2;

37.所述驱动芯片u3s由直流电源vext、电容c9s、电容c10s和变压器tr1组成;

38.所述驱动芯片u3s的输入引脚从上到下引脚分别为vdd、in1、in2;输出引脚从上到下引脚分别为gnd、out1、out2;

39.所述直流电源vext与所述驱动芯片u3s的输入引脚vdd连接;

40.所述电容c9s的一端与直流电源vext连接,另一端接地;

41.所述驱动芯片u3s的输入引脚in2与所述施密特触发器u2s的输出引脚out2连接;

42.所述驱动芯片u3s的输入引脚in1与所述信号输入部分连接;

43.所述驱动芯片u2s的输出引脚out1依次与电容c10s、变压器tr1串联后,再与所述驱动芯片u2s的输出引脚out2连接;

44.所述变压器tr1的副边分为两部分,上半部分是由共模电感l1s、二极管d1s和二极管d2s组成的第一整流器所构成,且上半部分连接驱动电路的下半桥驱动电路的输出侧;下半部分是由共模电感l2s、二极管d3s和二极管d4s组成的第二整流器所构成,且下半部分连接上半桥驱动电路的输出侧;

45.所述驱动供电主电路的主电路输出侧由上下两部分组成,上半部分给驱动电路的上半桥驱动电路供电,下半部分给驱动电路的下半桥驱动电路供电。

46.相对于现有技术,本发明的有益效果为:

47.1、本发明通过完全对称的电路设计可以量化分析在并联sic mosfet电路中,因sic mosfet的跨导、导通电阻、阈值电压等自身参数差异,电路布局或者封装布局等因素引

起的寄生电感不匹配,以及驱动电路的延迟时间、电流的上升斜率等动静态参数对并联器件中电流分布的影响,从而降低了并联器件之间的电流出现不平衡现象,对改善电流分布情况具有重大意义。

48.2、本发明在功率电路中,设计了一种电流测量电路,通过并联电阻和与mmcx同轴转换器相连接的示波器测量电压来间接得到mosfet的电流,从而避免了电流探头的低带宽对测量结果产生影响的情况。

49.3、本发明在驱动电路中可以通过调节延时环节中的滑动变阻器来改变驱动信号的延迟时间,从而能准确分析信号延迟对并联mosfet中动态电流分布的影响。

50.4、本发明在驱动供电电路中,可以通过调节施密特触发器前的滑动变阻器来改变占空比,并且通过改变vext电源的大小,从而分别控制正负门级驱动电压的大小,并实现了无级调节,达到调节任意电压大小的目的。

附图说明

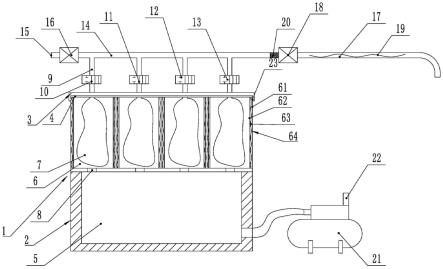

51.图1是本发明实施例的功率电路;

52.图2是本发明实施例中的驱动电路;

53.图3是本发明实施例中的驱动供电电路;

54.图4是本发明实施例中的系统电路连接图;

55.图中标号:1直流电源接口;2去耦电容;3a第一电流测量电路;3b第二电流测量电路;4支撑电容;5延迟环节;6驱动电阻。

具体实施方式

56.下面将结合附图对本发明的技术方案进行清楚、完整的描述。

57.本实施例中,一种基于并联sic mosfet动静态参数影响下的电流测量系统包括:功率电路、驱动电路和驱动供电电路;

58.图1是本发明实施例中的功率电路图,功率电路由直流母线侧电路和测量器件电路组成;

59.直流母线侧电路包括:直流电源接口1、支撑电容4以及去耦电容2;

60.直流电源接口1的正极dc 和负极dc-之间并联有支撑电容4以及去耦电容2;其中,支撑电容4和去耦电容2分别由n1个电容和n2个电容并联而成;

61.测量器件电路是由两条相互对称的支路a和支路b并联成的半桥电路,并与直流母线侧电路并联;

62.如图1所示,采用一个支撑电容、四个去耦电容相互并联,测量电路由五个电阻相互并联,系统中提到的电源均需要接上电容,从而起到稳压的作用,电源所需的稳压电容均为一个,而上述并联电阻和去耦电容均选择低寄生电感的型号,如贴片式陶瓷电容。系统中需要的芯片都可根据不同电压等级以及不同电路需求来进行更改,从而满足实验的不同测量要求。

63.直流电源插口1用来连接直流电压源,为功率电路提供直流母线电压,测量器件电路由两条相互对称的支路a和支路b组成半桥电路,需注意:在设计电路布局时,必须使支路a和b的布局保持严格对称,以使两条支路的寄生参数一致。支路a和支路b都由上下半桥组

成,支路a和支路b的中线处留有接口mid,可用于做双脉冲实验时接大电感;

64.支路a和支路b均由上、下半桥串联组成,其中,支路a和支路b的上半桥分别由金属-氧化物半导体场效应晶体管mosfet1和金属-氧化物半导体场效应晶体管mosfet3组成;

65.支路a的下半桥由金属-氧化物半导体场效应晶体管mosfet2和第一电流测量电路3a串联而组成;

66.第一电流测量电路3a由n个相互并联且阻值相同的电阻r1~rn以及与电阻r1~rn并联的mmcx接口rf1组成;在本实施例中选用五个阻值相同的电阻相互并联;

67.支路a中的金属-氧化物半导体场效应晶体管mosfet1的漏极与正极dc 相连,金属-氧化物半导体场效应晶体管mosfet1的源极和金属-氧化物半导体场效应晶体管mosfet2的漏极相连;金属-氧化物半导体场效应晶体管mosfet2的源极与第一电流测量电路3a的一端相连;第一电流测量电路3a的另一端与负极dc-相连;

68.支路a的金属-氧化物半导体场效应晶体管mosfet1的门极、漏极和源极分别预留有无源器件插口soc1-soc3;支路a的金属-氧化物半导体场效应晶体管mosfet2的门极、漏极和源极分别预留有无源器件插口soc7-soc9;

69.支路b的下半桥由金属-氧化物半导体场效应晶体管mosfet4和第二电流测量电路3b组成;

70.第二电流测量电路3b由n个相互并联且阻值相同的电阻以及与电阻并联的mmcx接口rf2组成;在本实施例中选用五个阻值相同的电阻相互并联,电流测量电路中的同轴转换器通过bnc转接头连接到示波器,将测量到的电压的波形衰减五个并联电阻阻值的倍数来得到电流的波形,可以避免因电流探头带宽不够而造成的影响;

71.支路b中的金属-氧化物半导体场效应晶体管mosfet3的漏极与正极dc 相连,金属-氧化物半导体场效应晶体管mosfet3的源极和金属-氧化物半导体场效应晶体管mosfet4的漏极相连;金属-氧化物半导体场效应晶体管mosfet4的源极与第二电流测量电路3b的一端相连;第二电流测量电路3b的另一端与负极dc-相连;

72.支路b的金属-氧化物半导体场效应晶体管mosfet3的门极、漏极和源极分别预留有无源器件插口soc4-soc6;支路b的金属-氧化物半导体场效应晶体管mosfet4的门极、漏极和源极分别预留有无源器件插口soc10-soc12,无源器件插口用来测量无源器件的不均衡性对并联mosfet电流的影响;无源器件插口可以连接数值不同的电阻、电感、电容,用来测量门极、漏极和源极寄生电感、电阻、电容等无源器件不均衡对并联mosfet电流的影响。

73.金属-氧化物半导体场效应晶体管mosfet1~金属-氧化物半导体场效应晶体管mofet4的门极和源极分别与驱动电路相连;一个驱动电路为支路a的上下半桥的mosfet1和mosfet2的门极和源极提供驱动信号,一个驱动电路为支路b的上下半桥的mosfet3和mosfet4的门极和源极提供驱动信号,支路a的mosfet1和mosfet2的驱动信号连接处分别为g_hs1、s_hs1和g_ls1、s_ls1,支路b的mosfet3和mosfet4的驱动信号连接处分别为g_hs2、s_hs2和g_ls2、s_ls2。

74.图2是本发明实施例中的驱动电路图,驱动电路为功率电路中的四个金属-氧化物半导体场效应晶体管提供驱动信号,用于驱动功率电路中的四个金属-氧化物半导体场效应晶体管的开通和关断,其中,功率电路的支路a和支路b上、下半桥的金属-氧化物半导体场效应晶体管分别用两个完全相同的驱动电路驱动,驱动电路分为两部分完全相同的上半

桥驱动电路和下半桥驱动电路,分别驱动功率电路中支路a或支路b上、下半桥的金属-氧化物半导体场效应晶体管;

75.任意一个上半桥驱动电路或下半桥驱动电路是由四部分组成,分别为:信号输入侧、延迟环节5、隔离型门极驱动器和输出侧;

76.信号输入侧用于将信号pwm输入电路中;

77.隔离型门极驱动器由隔离型门极驱动芯片u1d构成,隔离型门极驱动芯片u1d左侧从上到下引脚依次为vcc1、gnd1、in1、in2;隔离型门极驱动芯片u1d右侧从上到下引脚依次为vcc2、vee2、out1、out2;

78.延迟环节5是由肖特基二极管d1、电容c1d与可变电阻器r1组成的rc电路;rc电路的可变电阻器r1连接隔离型门极驱动芯片u1d的in1引脚;肖特基二极管d1和电容c1d串联后,再与可变电阻器r1并联连接隔离型门极驱动芯片u1d的gnd1引脚,gnd1引脚连接地;延迟环节可以改变驱动信号的延迟时间,可以通过调节延迟环节中的滑动变阻器来验证延迟时间对并联金属-氧化物半导体场效应晶体管mosfet电流分布的影响,

79.信号输入侧与rc电路相连接,其中,电源vd连接隔离型门极驱动芯片u1d的vcc1引脚;电源gnd_top和电容c2d并联后再与电源vcc_top并联连接隔离型门极驱动芯片u1d的vcc2引脚;电源gnd_top(s_hs)和电容c3d并联后再与电源vee_top并联连接隔离型门极驱动芯片u1d的vee2引脚;由驱动供电电路供电;

80.输出侧与n3个驱动电阻6相并联;n3个驱动电阻6分为两部分电阻后分别连接隔离型门极驱动芯片u1d的out1引脚和out2引脚;在本实施例中,采用两个驱动电阻6,驱动电路为功率电路中的四个mosfet提供驱动信号,驱动电阻6的输出端连接功率电路支路a上半桥的g_hs1,gnd_top连接功率电路支路a上半桥的s_hs1,支路a下半桥驱动电路与上半桥驱动电路相同,输出侧连接功率电路a下半桥的g_ls1、s_ls1,另一个相同的驱动电路连接功率电路支路b上下半桥的g_hs2、s_hs2和g_ls2、s_ls2,同时,改变驱动电阻的大小可以改变mosfet开关速度。

81.图3是本发明实施例中的驱动供电电路图,驱动供电电路由电压vd发生电路和驱动供电主电路组成;

82.电压vd发生电路由外接直流电源vext、稳压器芯片u1s、n4个电容并联的输入侧、n5个电容并联的输出侧组成;

83.稳压器芯片u1s的左、右引脚分别为in和out,底部引脚为gnd;

84.n4个电容并联的输入侧与外接直流电源vext连接后,再与稳压器芯片u1s的左引脚in相连;

85.n5个电容并联的输出侧与电压vd连接后,再与稳压器芯片u1s的右引脚out相连;in和out引脚并联后与底部引脚gnd连接;

86.驱动供电主电路由主电路输入侧、施密特触发器u2s、驱动芯片u3s、变压器tr1与共模电感、肖特基整流二极管和主电路输出侧组成;

87.主电路输入侧由电压vd、施密特触发器u2s、电阻r3s、电容c8s以及滑动变阻器r2s和电阻r4s构成;

88.施密特触发器供电u2s的左侧从上到下引脚分别为vcc、in1、in2;右侧从上到下引脚分别为gnd、out1、out2;

89.电压vd与底盘的施密特触发器u2s的左侧引脚vcc连接;电阻r3s的一端与电压vd连接,另一端与电容c8s的一端串联后,再与施密特触发器u2s的左侧引脚in1连接;电容c8s的另一端接地;

90.滑动变阻器r2s和电阻r4s串联后的结构与电阻r3s和电容c8s串联后的结构并联,构成信号输入部分再连接施密特触发器u2s的左侧引脚in2;驱动芯片u2s由外接直流电源vext供电、与驱动芯片u2s输出引脚与电容c13s和变压器tr1连接,驱动芯片可以加强施密特触发器u1s输出的信号,同时可以通过调节滑动变阻器r2s和r4s来调节占空比,进而控制外接直流电源vext的电压分配,从而达到调节驱动电压的效果,实现驱动电压的无级调节。

91.驱动芯片u3s由直流电源vext、电容c9s、电容c10s和变压器tr1组成;

92.驱动芯片u3s的输入引脚从上到下引脚分别为vdd、in1、in2;输出引脚从上到下引脚分别为gnd、out1、out2;

93.直流电源vext与驱动芯片u3s的输入引脚vdd连接;

94.电容c9s的一端与直流电源vext连接,另一端接地;

95.驱动芯片u3s的输入引脚in2与施密特触发器u2s的输出引脚out2连接;

96.驱动芯片u3s的输入引脚in1与信号输入部分连接;

97.驱动芯片u2s的输出引脚out1依次与电容c10s、变压器tr1串联后,再与驱动芯片u2s的输出引脚out2连接;

98.变压器tr1的副边分为两部分,上半部分是由共模电感l1s、二极管d1s和二极管d2s组成的第一整流器所构成,且上半部分连接驱动电路的下半桥驱动电路的输出侧;下半部分是由共模电感l2s、二极管d3s和二极管d4s组成的第二整流器所构成,且下半部分连接上半桥驱动电路的输出侧;

99.驱动供电主电路的主电路输出侧由上下两部分组成,上半部分给驱动电路的上半桥驱动电路供电,下半部分给驱动电路的下半桥驱动电路供电。

100.图4是本发明实施例中的系统电路连接图,由图4可知,整个系统共包括一个功率电路、两个驱动电路和两个驱动供电电路,两个驱动电路分别驱动功率电路中支路a和支路b上下半桥的mosfet,两个驱动供电电路分别给驱动电路供电。

101.通过上述实施例可见,本系统可以测量延迟时间来测量对并联mosfet电流分布的影响。

102.操作方式

103.步骤a、将功率电路、驱动电路和驱动供电电路设计成pcb电路板,在设计pcb电路板时,保证功率电路板的并联部分一致,目的是使得两个并联支路寄生参数一致;

104.步骤b、利用电焊技术将功率电路板、驱动电路板、驱动供电板上的器件焊接完成;

105.步骤c、将功率电路板、驱动电路板、驱动供电板通过排针排母相连接;

106.步骤d、测量中可以根据实际电路应用来设置相应的电压、电阻等电路参数的大小。功率板连接0~1200v的直流母线电压,因此需要选取相应电压等级金属-氧化物半导体场效应晶体管mosfet,来测量相应的器件参数。功率电路板上并联支路分别连接shunt电阻和mmcx接口,mmcx接口可直接与示波器相连,通过设置示波器的衰减比和电流信号类型可直接读取每个支路的电流大小;

107.步骤e、驱动电路板通过排针排母插在功率板上金属-氧化物半导体场效应晶体管

mosfet附近,其上方是通过排针排母连接的驱动供电板。驱动供电路板连接0-20v左右的直流电压,可通过调节驱动供电板上滑动变阻器的阻值来调节施密特触发器的占空比,最终达到调节驱动电压的目的。驱动板上连接双脉冲信号,此信号可由信号发生器提供,也可以由dsp提供,并且通过调节驱动板上滑动变阻器阻值大小来调节信号的延时时间,同时,可以改变驱动板上驱动电阻的阻值大小来控制金属-氧化物半导体场效应晶体管mosfet开关速度;

108.步骤f、功率板上在mosfet的门极、漏极和源极端分别留有寄生参数接口,可根据实际应用分别加上电感电阻电容来探究对sic mosfet并联均流的影响。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。