一种基于fpga的高速数据sata接口新型验证模组及方法

技术领域

1.本发明涉及芯片验证技术领域,具体涉及一种基于fpga的高速数据sata接口新型验证模组及方法。

背景技术:

2.鉴于芯片设计的复杂度提升,成功设计一个芯片所牵扯的步骤与过程也愈加复杂,所需花费的资金与时间周期也成倍增加,在芯片制造出来之前,很多精力会花费在rtl代码验证工作上,另外软件的相关开发工作,也会在得到芯片前开始,这两方面都需要借助fpga原型来模拟芯片的行为,帮助硬件开发和软件开发者,共同提升工作效率。

3.fpga原型验证已是当前原型验证的主流且成熟的芯片验证方法——它通过将rtl移植到现场可编程门阵列(fpga)来验证asic的功能,并在芯片的基本功能验证通过后就可以开始驱动的开发,一直到芯片tape out并回片后都可以进行驱动和应用的开发。

4.由于软件通常占设计工作量的一半以上,所以socrtl的fpga实现也可以用作软件开发,硬件/软件协同验证和软件验证的基础,所有这些都在最终硅芯片可用之前完成。

5.所有这些因素都有助于降低设计成本并缩短上市时间,降低重新调整的风险。例如,已经在fpga原型上得到广泛验证的软件应该更容易与来自晶圆厂的第一块硅相结合。fpga原型也可用于设置任何可能的硅后调试路径。

6.但是,fpga也是芯片产品,所以内部的信号无法直接观测。通常需要借助于fpga的debug工具在生成bit文件前选取要观察的信号。例如对sata、pcie等高速接口进行fpga板级验证时,需要使用fpga某些ip替换项目中高速接口的物理层,若验证出现问题很难去快速定位,这就导致每次替换ip后验证需要花费大量时间。

技术实现要素:

7.针对现有技术的不足,本发明提供了一种基于fpga的高速数据sata接口新型验证模组及方法,以解决当使用fpga某些ip替换项目中高速接口的物理层时出现问题无法快速定位的问题,降低增效,降低单独设计或单独购买ip的成本。为了解决这一问题,对高速接口的fpga验证提出了一种“验证 检测”的新型验证方法,方便验证人员发现问题时能够快速定位,缩短了验证时间,提高了ip验证的复用率,降低了验证成本。

8.本发明通过以下技术方案予以实现:

9.一种基于fpga的高速数据sata接口新型验证模组,包括:高速数据sata接口控制模块、时钟转换模块、复位模块、k码检测模块以及pma模块;

10.所述高速数据sata接口控制模块主要用于加载以及解析高速数据协议,且与所述pma模块进行数据交互相连;

11.在发送通路中,所述时钟转换模块将发送时钟发送到所述高速数据sata接口控制模块,所述高速数据sata接口控制模块将复位信号发送给所述pma模块使其初始化,所述复位模块将pma复位信号处理后发送给所述高速数据sata接口控制模块,所述高速数据sata

接口控制模块将并行数据发送至所述k码检测模块进行信号检测,所述k码检测模块再将并行数据发送给所述pma模块进行串行化,最后将串行化数据传输到pma的serdes发送tx差分通路上;

12.在接收通路中,所述时钟转换模块将接收时钟发送到所述高速数据sata接口控制模块,所述高速数据sata接口控制模块将复位信号发送给pma模块使其初始化,所述复位模块将pma复位信号处理后发送给所述高速数据sata接口控制模块,所述pma模块将serdes接收rx差分通路上的串行数据解串后,发送给所述k码检测模块进行信号检测,所述k码检测模块再将并行数据发送给所述高速数据sata接口控制模块。

13.优选的,所述时钟转换模块将参考时钟进行分频、处理,驱动所述高速数据sata接口控制模块和所述pma模块。

14.优选的,所述的差分参考时钟首先经过ibuf_ds差分转单端后再进入bufg_gt,输出一个gtrefclk作为所述pma模块的参考时钟,另外一个输出经过锁相环二分频后输出发送时钟phy_clk_asic和接收时钟phy_clk_rbc,发送给所述高速数据sata接口控制模块。

15.优选的,所述复位模块用于等所述pma模块tx侧、rx侧均复位完成后,再将复位完成信号发送给所述高速数据sata接口控制模块。

16.优选的,当同时检测到所述pma模块tx侧初始化完成信号txresetdone为1、且rx侧初始化完成信号rxresetdone为1时,将1赋值给gth_rst并发送给所述高速数据sata接口控制模块,否则将0赋值给gth_rst并发送给所述高速数据sata接口控制模块。

17.优选的,所述k码检测模块分别检测所述高速数据sata接口控制模块发送的并行数据和所述pma模块发送的并行数据中是否有k码,最后将检测信号输出。

18.优选的,所述高速数据sata接口控制模块将数据tx_data传输到所述k码检测模块,所述k码检测模块对所述数据tx_datatx-data进行检测;

19.所述数据tx_data包括:comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm以及r_ok;

20.上述原语均由k码组成,其中comreset、cominit、comwake为oob序列,由align加上一段空闲信号组成;

21.sync原语的值为{d21.5,d21.5,d21.4,k28.3};

22.align原语的值为{d27.3,d10.2,d10.2,k28.5};

23.x_rdy原语的值为{d23.2,d23.2,d21.5,d28.3};

24.r_rdy原语的值为{d10.2,d10.2,d21.4,d28.3};

25.r_ip原语的值为{d21.2,d21.2,d21.5,k28.3};

26.wtrm原语的值为{d24.2,d24.2,d21.5,k28.3};

27.r_ok原语的值为{d21.1,d21.1,d21.5,k28.3}。

28.优选的:

29.tx_k_det为10位的数据,复位值为10’b0,0到9位分别对应comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok;

30.若检测到tx_data中有comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok信号,则tx_k_det对应位置1,否则不变;之后再将tx_data的值赋给phy_tx_data,在发送时钟phy_clk_asic同步下发送给所述pma模块;

31.反之,所述pma模块将并行数据phy_rx_data传输到所述k码检测模块进行数据检测;

32.rx_k_det为10位数据,复位值为10’b0,0到9位分别对应comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok;

33.若检测到phy_rx_data中有k码,则rx_k_det对应位置1,否则不变;之后再将phy_rx_data的值赋给rx_data,在接收时钟phy_clk_rbc同步下发送给所述高速数据sata接口控制模块。

34.本发明还提供了另一种技术方案:一种基于fpga的高速数据sata接口的新型验证方法,所述验证方法采用上述所述的基于fpga的高速数据sata接口新型验证模组设计搭建,包括如下步骤:

35.步骤s1:高速数据sata接口控制模块的发送时钟由时钟转换模块将参考时钟二分频后得到,高速数据sata接口控制模块的数据在发送时钟同步下传输到k码检测模块;

36.步骤s2:k码检测模块包含发送通路k码信号检测和接收通路k码信号检测,在发送通路下,k码检测模块会检测发送数据中的k码并将其输出,再将数据发送给pma模块;

37.步骤s3:高速数据sata接口控制模块的接收时钟由时钟转换模块将参考时钟二分频后得到,k码检测模块检测pma模块传输过来的数据;

38.步骤s4:在接收通路下,k码检测模块将数据在接收时钟同步下传输到高速数据sata接口控制模块。

39.本发明的有益效果为:

40.本发明的一种基于fpga的高速数据sata接口新型验证模组及方法将验证和检测相结合,解决了高速数据sata接口替换物理媒体层ip后的验证过程中,无法快速定位错误的问题;方便验证人员发现问题时能够快速定位,缩短了验证时间,提高了ip验证的复用率,降低了验证成本。

附图说明

41.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

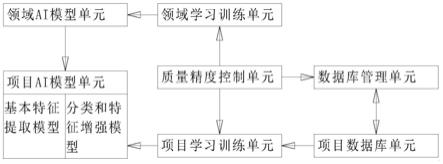

42.图1是本发明提供的基于fpga的高速数据sata接口新型验证方法原理框图;

43.图2是本发明的时钟转换模块的原理框图;

44.图3是本发明的k码检测模块的原理框图;

45.图4是本发明的复位模块的原理框图。

具体实施方式

46.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

47.实施例1:

48.请参阅图1所示,本发明的技术方案提供了一种高速数据sata接口新型验证模组的实施例,包括高速数据sata接口控制模块、时钟转换模块、复位模块、k码检测模块以及pma(物理介质接入)模块。

49.进一步地,如图1所述基于fpga的高速数据sata接口新型验证方法原理框图,高速数据sata接口控制模块主要是加载以及解析高速数据协议,且与pma模块进行数据交互相连。在发送通路中,时钟转换模块将参考时钟进行分频、处理,将发送时钟phy_clk_asic发送给高速数据sata接口控制模块,再将参考时钟gtrefclk发送给pma模块;高速数据sata接口控制模块将复位信号发送给pma模块,等到pma模块的tx侧、rx侧均初始化稳定后,复位模块将pma模块复位完成信号gth_rst发送给高速数据sata接口控制模块,sata接口控制模块再将发送数据tx_data发送到k码检测模块;k码检测模块检测tx_data中的k码并将其输出,再将发送数据phy_tx_data发送到pma模块进行串行化处理,最后将串行的数据传输到pma的serdes发送tx差分通路上;在接收通路中,时钟转换模块将参考时钟进行分频、处理,将接收时钟phy_clk_rbc发送给高速数据sata接口控制模块,再将参考时钟gtrefclk发送给pma模块;高速数据sata接口控制模块将复位信号发送给pma模块,等到pma模块的tx侧、rx侧均初始化稳定后,复位模块将pma模块复位完成信号gth_rst发送给高速数据sata接口控制模块,pma模块将serdes接收rx差分通路上的串行数据解串后,将数据发送给k码检测模块进行信号检测,k码检测模块再将并行数据发送给高速数据sata接口控制模块。pma模块将serdes接收rx差分通路上的串行数据解串后,发送给k码检测模块进行信号检测,k码检测模块再将并行数据发送给高速数据sata接口控制模块。

50.进一步地,如图2所述时钟转换模块原理框图。差分参考时钟首先经过ibuf_ds差分转单端后再进入bufg_gt,输出一个gtrefclk作为pma模块的参考时钟,另外一个输出经过锁相环二分频后输出发送时钟phy_clk_asic和接收时钟phy_clk_rbc发送给高速数据sata接口控制模块。

51.进一步地,如图3所述k码检测模块原理框图,k码检测模块主要作用是分析8b/10b编码之后、解码之前的数据。高速数据sata接口控制模块将数据tx_data传输到k码检测模块,k码检测模块对tx-data进行检测,包括comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok。这些原语均由k码组成,其中comreset、cominit、comwake为oob序列,由align加上一段空闲信号组成;sync的值为{d21.5,d21.5,d21.4,k28.3},align原语的值为{d27.3,d10.2,d10.2,k28.5},x_rdy的值为{d23.2,d23.2,d21.5,d28.3},r_rdy的值为{d10.2,d10.2,d21.4,d28.3},r_ip的值为{d21.2,d21.2,d21.5,k28.3},wtrm的值为{d24.2,d24.2,d21.5,k28.3},r_ok的值为{d21.1,d21.1,d21.5,k28.3}。tx_k_det为10位的数据,复位值为10’b0,0到9位分别对应comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok,若检测到tx-data中有comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok信号,则tx_k_det对应位置1,否则不变,之后再将tx-data的值赋给phy_tx_data,在发送时钟phy_clk_asic同步下发送给pma模块。反之,pma模块将并行数据phy_rx_data传输到k码检测模块进行数据检测。rx_k_det为10位数据,复位值为10’b0,0到9位分别对应comreset、cominit、comwake、sync、align、x_rdy、r_rdy、r_ip、wtrm、r_ok,若检测到phy_rx_data中有k码,则rx_k_det对应位置1,否则不变,之后再将

phy_rx_data的值赋给rx_data,在接收时钟phy_clk_rbc同步下发送给高速数据sata接口控制模块。

52.进一步地,如图4所述复位模块原理框图。当同时检测到pma模块tx侧初始化完成信号txresetdone为1且rx侧初始化完成信号rxresetdone为1时,将1赋值给gth_rst并发送给高速数据sata接口控制模块,否则将0赋值给gth_rst并发送给高速数据sata接口控制模块。

53.实施例2:

54.本发明的技术方案还提供了另一种实施例:一种基于fpga的高速数据sata接口的新型验证方法,包括如下步骤:

55.步骤s1:高速数据sata接口控制模块的发送时钟由时钟转换模块将参考时钟二分频后得到,高速数据sata接口控制模块的数据在发送时钟同步下传输到k码检测模块;

56.步骤s2:k码检测模块包含发送通路k码信号检测和接收通路k码信号检测,在发送通路下,k码检测模块会检测发送数据中的k码并将其输出,再将数据发送给pma模块;

57.步骤s3:高速数据sata接口控制模块的接收时钟由时钟转换模块将参考时钟二分频后得到,k码检测模块检测pma模块传输过来的数据;

58.步骤s4:在接收通路下,k码检测模块将数据在接收时钟同步下传输到高速数据sata接口控制模块。

59.本发明的一种基于fpga的高速数据sata接口新型验证模组及方法将验证和检测相结合,解决了高速数据sata接口替换物理媒体层ip后的验证过程中,无法快速定位错误的问题。

60.以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。