一种基于负反馈改善伪静态回路的动态d触发器

技术领域

1.本发明涉及一种基于负反馈改善伪静态回路的动态d触发器。

背景技术:

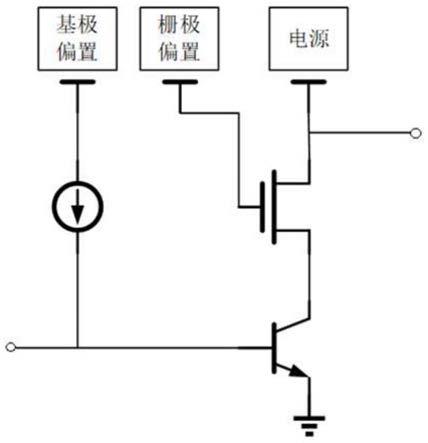

2.传统cmos动态d触发器与cmos静态d触发器不同,cmos静态d触发器需要4个反相器与4个传输门,而动态d触发器通过增加输入级电容存储电荷来保持数据。但是若下一拍时钟输入的数据与存储数据不同,则很有可能对输入级电容充放电,导致误码。为解决其存储电荷不稳定的问题,传统方法通过伪静态回路的加入来保持电荷。如图1所示,通过加入一个小尺寸的反相器与动态d触发器中的反相器构成一个寄存器结构。伪静态回路的设计使得存储节点的抗噪声性能大幅提升,其本质通过正反馈回路强制存储节点锁定在0或1上。图1中,第一传输门tg1,一端接输入信号d,另一端与第一电荷存储电容c1和第一反相器inv1的输入端相连;第一电荷存储电容c1另一端接地,第一传输门tg1中nmos栅端接第一正向时钟clk,pmos栅端接第一反相器inv1与第一反馈反相器sinv1的输入输出首尾相连,构成正反馈的寄存器结构。第一反相器inv1的输出端接第二传输门tg2的输入端,第二传输门tg2的输出端接第二电荷存储电容c2和第二反相器inv2;第二电荷存储电容从c2另一端接地,第二传输门tg2中nmos栅端接第二反向时钟pmos栅端接第一正向时钟clk。第二反相器inv2与第二反馈反相器sinv2的输入输出首尾相连,构成正反馈的寄存器结构。第二反相器inv2的输出即为动态d触发器的输出q级。

3.然而伪静态回路的加入也会带来相应的问题。其一、伪静态回路会增加d触发器的建立时间,从而增加数据传输的延时。动态d触发器的优势就在于其结构简单,延时远远小于其他类型d触发器,从而可以广泛应用在高频率时钟的数字集成电路当中。如果伪静态回路设计不合理反而会增加延时。其二,伪静态回路会使得局部形成正反馈闭环。每次上一级写入不同的数据均需打破局部的正反馈回路,刷新存储节点的电荷。如果伪静态回路的尺寸过大,则不同的数据无法写入到d触发器中,从而使d触发器的功能失效。

技术实现要素:

4.本发明为解决动态d触发器伪静态回路的问题,提出了一种基于时序控制和负反馈控制的结构。所发明的结构如图2所示。

5.图2中,第一传输门tg1,一端接输入信号d,另一端与第一电荷存储电容c1和第一反相器inv1的输入端相连;第一电荷存储电容c1另一端接地,第一传输门tg1中nmos栅端接第一正向时钟clk,pmos栅端接第二反向时钟第一反相器inv1输入端与第一晶体管mos1的源级相连,第一晶体管mos1的漏极与第三反相器inv3的输出相连;第一反相器inv1的输出端与第二晶体管mos2的漏极相连,第二晶体管mos2的源级与第三反相器inv3的输入相连。第三反相器inv3的输入与第三晶体管mos3的漏极相连,第三反相器inv3的输出端与第三晶体管mos3的源级相连。第一晶体管mos1的栅极和第二晶体管mos2的栅极接第二反向时钟第三晶体管mos3的栅极接第一正向时钟clk。

6.第一反相器inv1的输出端接第二传输门tg2的输入端,第二传输门tg2的输出端接第二电荷存储电容c2和第二反相器inv2;第二电荷存储电容从c2另一端接地,第二传输门tg2中nmos栅端接第二反向时钟pmos栅端接第一正向时钟clk。第二反相器inv2输入端与第四晶体管mos4的源级相连,第四晶体管mos4的漏极与第四反相器inv4的输出相连;第二反相器inv2的输出端与第五晶体管mos5的漏极相连,第五晶体管mos5的源级与第四反相器inv4的输入相连。第四反相器inv4的输入与第六晶体管mos6的漏极相连,第四反相器inv4的输出端与第六晶体管mos6的源级相连。第四晶体管mos4的栅极和第五晶体管mos5的栅极接第一正向时钟clk,第六晶体管mos6的栅极接第二反向时钟第二反相器inv2的输出即为改善后的动态d触发器的输出级q。图2中的箭头代表着信号传递的方向,“ ”和

“‑”

分别代表正反馈和负反馈。

7.所述基于负反馈控制的动态d触发器工作过程描述如下。

8.步骤1:当数据传送至动态d触发器的输入d端,且第一正向时钟clk为高电平时,第二反向时钟为低电平,第一传输门tg1导通,将d端数据传输进入动态d触发器。第一晶体管mos1和第二晶体管mos2关断,输出级写入只需要对第一电荷存储电容c1充电即可,而不必打破第一反相器inv1和第三反相器inv3构成的闭环正反馈,在工作过程中,inv1采用较大的宽长比,nmos晶体管的宽长比约为250μm比0.18μm,pmos晶体管的宽长比约为500μm比0.18μm,c1为其寄生电容,其大小约为十飞法至一百飞法内,所以并不需要额外的版图面积。此时,第三晶体管mos3导通,原理上相当于将第三反相器inv3输入输出短接,形成自放电或者自充电的负反馈结构,使得第三反相器inv3的输入输出的电压值稳定在二分之一电源电压处,电压信号的传递如图2中的标有

“‑”

箭头所示。

9.步骤2:当第一正向时钟clk为低电平时,第二反向时钟为高电平,第一传输门tg1断开,第一晶体管mos1和第二晶体管mos2导通,第三晶体管mos3关断。此时第三晶体管mos3的闭环负反馈被终止,第三反相器inv3的输入输出与第一反相器inv1的输出输入短接,形成闭环正反馈的寄存器结构,从而稳定第一电荷存储电容c1的电荷。电压信号的传递如图2中标有“ ”箭头所示。此阶段,当写入的数据发生跳变时,第一反相器inv1仅需将第三反相器inv3的输入端从二分之一电源电压上拉至电源或者下拉至地段,而不用从电源下拉至地,或从地上拉至电源,减小了一半的充放电时间,从而降低了数据传输的延时。

10.步骤3:当第一正向时钟clk为低电平时,第二反向时钟为高电平,第二传输门tg2导通,信号传递至第二传输门tg2导通。此时,第六晶体管mos6导通,将第四反相器inv4输入输出短接,形成自放电或者自充电的负反馈结构,使得第四反相器inv4的输入输出的电压值稳定在电源电压的二分之一处,通过自充电或者自放电减小写入数据的压力。

11.步骤4:当第一正向时钟clk为高电平时,第二反向时钟为低电平时,第二传输门tg2断开,数据传输至动态d触发器的输出端q。第四晶体管mos4和第五晶体管mos5导通,第六晶体管mos6关断。此时第六晶体管mos6的闭环负反馈被终止,第四反相器inv4的输入输出与第二反相器inv2的输出输入短接,形成闭环正反馈的寄存器结构,从而稳定第二电荷存储电容c2的电荷。电压信号的传递如图2中标有“ ”箭头所示。此阶段,当写入的数据发生跳变时,第二反相器inv2仅需将第四反相器inv4的输入端从二分之一电源电压上拉至电源电压或者下拉至地端0电位处,而不用从电源下拉至地,或从地上拉至电源,减小了一半

的充放电时间,从而降低了数据传输的延时。

12.有益效果

13.本发明提出了一种基于时序控制和负反馈控制的动态d触发器结构,其本质在于大幅优化了伪静态回路,既保障伪静态回路的功能,也改善了伪静态回路的延时和数据写入的问题。与传统的动态d触发器相比,具有以下有益效果。

14.1.所述改善的伪静态回路基于时序控制,在保障数据稳定的基础上,从原理上避免了写入数据时遭遇处于正反馈回路的寄存器结构。传统d触发器结构为了保证数据稳定,增加了小尺寸的反相器构成伪静态回路。但是两个反相器的首尾相接构成的寄存器结构将会给写入数据增加困难,因为其输入负载不再是纯电容,还包括一个电阻,从而提高对上一级负载能力的要求并增加了相应的延时。本发明通过时序开关的控制在数据写入阶段,断开伪静态回路与主路的连接,从而降低了对写入能力的要求,保障了动态d触发器的高速优势。

15.2.所述改善的伪静态回路基于负反馈控制,进一步降低了写入能力的要求。下面以第一晶体管mos1为例,并简称mos1。从物理上分析,mos管构成开关本质是通过栅压控制其等效电阻。当写入的数据发生变化时,比如从“0”变为“1”,栅压为低电平的mos1处于高阻态,从而断开inv1的输入与inv3的输出。但实际上还有微小的电流通过mos1。但是通过mos3的负反馈结构,inv3的输出端迅速变为二分之一电源电压,通过的电流可由下式(1)和(2)描述。r

off

为mos1断开时的等效电阻,i为未加入负反馈控制流经mos1的电流,i

′

为加入负反馈控制流过mos1的电流,vdd为电源电压。

[0016][0017][0018]

由公式(1)和公式(2)知,在原理上,负反馈控制可使得mos1断开时的等效电阻提升两倍。从而进一步减小对写入能力的要求。

[0019]

3.所述改善的伪静态回路基于负反馈控制,降低了数据传输的延时。下面以第二传输门tg2为例,并简称tg2。当tg2导通时,数据从第一反相器inv1经过第二反相器inv2输出至q端。主要的延时体现在给tg2两端的电容充放电的时间上。对于第二电荷存储电容c2来说,保持强“1”和强“0”意味着保持数据稳定,而第三反相器inv3的输入端的寄生电容则带来不必要的延时。在tg2导通的前一个时钟周期,负反馈回路使得第三反相器inv3的输入输出端保持在二分之一电源电压。在tg2导通时,也是第二晶体管mos2导通时,以tg2处数据从“0”变为“1”为例,第一反相器inv1不需要将第三反相器inv3的扇入电容从0充电至vdd,而是从充电至vdd,减小了一半的充电时间,从而降低了数据传输的延时。

[0020]

4.所述改善的伪静态回路基于时序控制和负反馈控制,降低了对伪静态回路的尺寸要求,从而降低了设计难度。在图1中,第一反馈反相器sinv1和第二反馈反相器sinv2的尺寸选取是个两难问题,若是反馈反相器的尺寸选取过大则会等导致形成强大正反馈的寄存器结构,外界很难改变其状态。若是反馈反相器的尺寸过小,则会导致电荷存储电容的电

荷不稳定,从而降低了数据的稳定性。而基于图2中的架构,对于第一反相器inv1来说存在两种工作状态,一是数据写入状态,此时第一晶体管mos1和第二晶体管mos2不导通,inv3处于负反馈状态降低写入能力的要求和数据传输的延时。二是数据保持状态,此时第一晶体管mos1和第二晶体管mos2导通,第一反相器inv1和第三反相器inv3构成正反馈的寄存器结构,保持数据的稳定。对于设计者来说,第一反相器inv1和第三反相器inv3包括其他晶体管,可以采取相同的尺寸,以保证版图布局的匹配性;亦可以灵活设计尺寸,以满足不同应用场景下的需要。

附图说明

[0021]

图1为传统动态d触发器和传统伪静态回路

[0022]

图2为本发明提出的基于负反馈伪静态回路改善的动态d触发器内部结构

[0023]

图3为利用本发明提出的动态d触发器构成的4bit伪随机序列发生器

[0024]

图4为利用本发明提出的动态d触发器构成的除二分频器

[0025]

图5为伪随机序列发生器在4.95ghz的时钟信号下的时域波形

[0026]

图6为伪随机序列发生器在0.5hz的时钟信号下的时域波形

[0027]

图7为除二分频器在5ghz的时钟信号下的时域波形

[0028]

图8为除二分频器在0.5hz的时钟信号下的时域波形

[0029]

图9为去除伪静态回路的动态d触发器构成的分频器在0.5hz的时钟信号下的时域波形,以验证本发明对低频特性的改善。

具体实施方式

[0030]

将本发明提出的基于负反馈控制的伪静态回路改善的动态电路结构,即图2中所示电路结构封装成一个动态d触发器,为实施例1。而将此动态d触发器分别应用在实施例2中的4bit伪随机序列发生器和实施例3中的除二分频器。实施例采用台积电tsmc180nm工艺库进行实际设计和仿真验证。

[0031]

具体实施例1

[0032]

以下结合图2说明本发明的具体电路连接和实施方式以及器件参数。

[0033]

本发明所述为解决动态d触发器伪静态回路问题,提出的一种基于时序控制和负反馈控制的电路。整个电路由传输门、电荷存储器、反相器和mos晶体管组成。图2中第一存储电荷c1和第二存储电荷c2,由第一反相器inv1和第二inv2输入级中栅极的寄生电容代替。利用寄生电容充当存储电荷的电容一方面可以减少写入数据时间,另一方面可以减小版图面积。

[0034]

具体实施例1的连接关系如下:第一传输门tg1,一端接输入信号d,另一端与第一反相器inv1的输入端相连;第一传输门tg1中nmos栅端接第一正向时钟clk,pmos栅端接第二反向时钟第一反相器inv1输入端与第一晶体管mos1的源级相连,第一晶体管mos1的漏极与第三反相器inv3的输出相连;第一反相器inv1的输出端与第二晶体管mos2的漏极相连,第二晶体管mos2的源级与第三反相器inv3的输入相连。第三反相器inv3的输入与第三晶体管mos3的漏极相连,第三反相器inv3的输出端与第三晶体管mos3的源级相连。第一晶体管mos1的栅极和第二晶体管mos2的栅极接第二反向时钟第三晶体管mos3的栅极

接第一正向时钟clk。

[0035]

第一反相器inv1的输出端接第二传输门tg2的输入端,第二传输门tg2的输出端接第二反相器inv2;第二传输门tg2中nmos栅端接第二反向时钟pmos栅端接第一正向时钟clk。第二反相器inv2输入端与第四晶体管mos4的源级相连,第四晶体管mos4的漏极与第四反相器inv4的输出相连;第二反相器inv2的输出端与第五晶体管mos5的漏极相连,第五晶体管mos5的源级与第四反相器inv4的输入相连。第四反相器inv4的输入与第六晶体管mos6的漏极相连,第四反相器inv4的输出端与第六晶体管mos6的源级相连。第四晶体管mos4的栅极和第五晶体管mos5的栅极接第一正向时钟clk,第六晶体管mos6的栅极接第二反向时钟第二反相器inv2的输出即为改善后的动态d触发器的输出级q。

[0036]

电路中的反相器inv1、inv2和传输门tg1、tg2都由一个pmos和一个noms晶体管组成。其中反相器inv3和inv4是单独设计的,它们的nmos和pmos的长度均为220.0nm,宽度均为180.0nm。反相器inv1、inv2的nmos和pmos晶体管的长度为1.95μm,宽度为180.0nm。传输门tg1、tg2的nmos和pmos晶体管的长度均为1.9μm,宽度均为180.0nm。其余mos晶体管的长度和宽度均相同,其长度为220.0nm,宽度为180.0nm。各个器件的详细参数如表1所示。

[0037]

表1.各器件参数表

[0038]

[0039][0040]

负反馈时动态d触发器反馈的工作描述如下。

[0041]

步骤1:当数据传送至动态d触发器的输入d端,且第一正向时钟clk为高电平时,第二反向时钟为低电平,第一传输门tg1导通,将d端数据传输进入动态d触发器。第一晶体管mos1和第二晶体管mos2关断,输出级写入只需要对第一电荷存储电容c1充电即可,而不必打破第一反相器inv1和第三反相器inv3构成的闭环正反馈,在工作过程中,inv1采用较大的宽长比,nmos晶体管的宽长比约为250μm比0.18μm,pmos晶体管的宽长比约为500μm比0.18μm,c1为其寄生电容,其大小约为十飞法至一百飞法内,所以并不需要额外的版图面积。此时,第三晶体管mos3导通,原理上相当于将第三反相器inv3输入输出短接,形成自放电或者自充电的负反馈结构,使得第三反相器inv3的输入输出的电压值稳定在二分之一电源电压处,电压信号的传递如图2中的标有

“‑”

箭头所示。

[0042]

步骤2:当第一正向时钟clk为低电平时,第二反向时钟为高电平,第一传输门tg1断开,第一晶体管mos1和第二晶体管mos2导通,第三晶体管mos3关断。此时第三晶体管mos3的闭环负反馈被终止,第三反相器inv3的输入输出与第一反相器inv1的输出输入短接,形成闭环正反馈的寄存器结构,从而稳定第一电荷存储电容c1的电荷。电压信号的传递如图2中标有“ ”箭头所示。此阶段,当写入的数据发生跳变时,第一反相器inv1仅需将第三反相器inv3的输入端从二分之一电源电压上拉至电源或者下拉至地段,而不用从电源下拉至地,或从地上拉至电源,减小了一半的充放电时间,从而降低了数据传输的延时。

[0043]

步骤3:当第一正向时钟clk为低电平时,第二反向时钟为高电平,第二传输门tg2导通,信号传递至第二传输门tg2导通。此时,第六晶体管mos6导通,将第四反相器inv4输入输出短接,形成自放电或者自充电的负反馈结构,使得第四反相器inv4的输入输出的电压值稳定在电源电压的二分之一处,通过自充电或者自放电减小写入数据的压力。

[0044]

步骤4:当第一正向时钟clk为高电平时,第二反向时钟为低电平时,第二传输门tg2断开,数据传输至动态d触发器的输出端q。第四晶体管mos4和第五晶体管mos5导通,第六晶体管mos6关断。此时第六晶体管mos6的闭环负反馈被终止,第四反相器inv4的输入输出与第二反相器inv2的输出输入短接,形成闭环正反馈的寄存器结构,从而稳定第二电荷存储电容c2的电荷。电压信号的传递如图2中标有“ ”箭头所示。此阶段,当写入的数据发生跳变时,第二反相器inv2仅需将第四反相器inv4的输入端从二分之一电源电压上拉至电源电压或者下拉至地端0电位处,而不用从电源下拉至地,或从地上拉至电源,减小了一半的充放电时间,从而降低了数据传输的延时。

[0045]

实施例2

[0046]

图3中为伪随机序列发生的逻辑结构图,其中第一d触发器dff1、第二d触发器dff2、第三d触发器dff3、第四d触发器dff4的输入d端和输出q端进行级联,即第一d触发器dff1的输出q1端与第二d触发器dff2的输入d2端相连,第二d触发器dff2的输出q2端与第三d触发器dff3的输入d3端相连,第三d触发器dff3的输出q3端与第四d触发器dff4的输入d4端相连,第三d触发器dff1的输出q3端和第四触发器dff4的输出q4端接入图中异或门xor的输入端,进行异或运算,异或门xor的输出端接第一触发器dff1的输入端。第一d触发器dff1、第二d触发器dff2、第三d触发器dff3、第四d触发器dff4的时钟端接相同频率的第一正向时钟clk,四者的输出端q1、q2、q3、q4,为伪随机序列的信号输出端。

[0047]

本发明最大的优点是通过时钟控制和负反馈控制大大拓宽了动态d触发器的频率适用范围。动态d触发器的工作频率主要指时钟信号控制d触发器内部的开关的工作频率。图5展示了基于本发明构成的4bit伪随机序列发生器在时钟周期202ps,即时钟频率4.95ghz的时域波形,由仿真结果可知在接近5g的较高开关频率下,伪随机序列发生器仍可正常工作。图6展示本发明构成的4bit伪随机序列发生在时钟周期2s,及时钟频率0.5hz的时域波形,由仿真结果可知在0.5hz低频的情况下,伪静态回路正常工作并保证动态d触发器的数据稳定。由图5和图6可知利用本发明基于负反馈伪静态回路改善的动态d触发器,具有较高的频率适应性,在低频或者高频的情况皆可正常工作。

[0048]

实施例3

[0049]

图4中为利用本发明的动态d触发器构成的二分频器。第一d触发器dff1的时钟端接入第一正向时钟clk,输出q1端接第一反相器inv1的输入端和第二反相器inv2的输入端,第一反相器inv1的输出端接第一d触发器的输入d1端,第二反相器inv2的输出端为输出第一正向时钟clk的二分频信号out。

[0050]

第二反相器inv2的分频的缓冲级,提高分频的驱动能力。图7展示了基于负反馈伪静态回路改善的动态d触发器结构构成二分频器的时域波形。输入高频5ghz的时钟信号,输出为2.5ghz的二分频信号。图8展示了输入0.5hz的时钟信号,输出为0.25hz的二分频信号。将图2中的第一晶体管mos1、第二晶体管mos2、第三晶体管mos3、第四晶体管mos4、第五晶体管mos5、第六晶体管mo6、第三反相器inv3和第四反相器inv4除去,即除去伪静态回路,回归为传统的动态d触发器,并将其封装应用在图4所示的除二分频器中,得到如图9所示的波形,输入0.5hz的时钟信号,但输出的是错误波形。这说明在低频情况下,传统动态d触发器由于存储电荷流失导致数据丢失,从而丧失触发功能。结合图8和图9可知,本发明的可以明显改善动态d触发器的低频特性,具有较高的频率适用范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。