1.本公开涉及半导体封装技术领域,具体而言,涉及一种半导体存储装置及其标识方法。

背景技术:

2.dram(dynamic random access memory,动态随机存取存储器)是一种半导体存储器,由于其存储单元结构简单、集成度高,且具有大容量化、高速化以及低功率化等特点,现被广泛应用于各个领域。

3.在上述存储器的制造过程中,在芯片进行封装测试后,会在芯片的表面进行芯片相关信息的记录,通常会在芯片封装后将芯片置于激光标识机中,通过镭射刻字的方法将芯片的信息刻印在芯片表面,但通过激光标记芯片的方式需要把芯片从封测机器中移至激光标刻机中才能进行标识,导致效率低,且由于激光镭射刻字的当量控制问题会导致芯片的损坏,降低了产能。

4.需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现要素:

5.本公开的目的在于克服上述现有技术的不足,提供了一种半导体存储装置及其标识方法。

6.本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本公开的实践而习得。

7.根据本公开的一个方面,提供了一种半导体装置的标识方法,该方法包括:提供包括外围区的半导体存储装置,在所述外围区上设置有外装构件,所述外装构件上具有封装面;

8.在所述封装面上形成记录层,并将所述封装面划分为多个像素区域;

9.所述外围区还设置有控制器和预设的像素电路,通过所述控制器控制所述预设的像素电路中的像素电阻通电,使与通电后的像素电阻对应的像素区域显色,以在所述记录层上形成具有特定形状的标识。

10.在本公开的一些实施例中,基于前述方案,所述在所述封装面形成记录层,包括:将显色剂和染料剂混合制成记录层,并将所述记录层涂布在所述封装面上。

11.在本公开的一些实施例中,基于前述方案,所述在所述封装面上形成记录层后,包括:在所述记录层上形成保护层,所述保护层包括用于防止所述记录层上的标识发生衰退的抗氧化剂。

12.在本公开的一些实施例中,基于前述方案,所述方法还包括:

13.所述外围区上还设置有译码器,通过所述译码器对所述控制器传输的编程命令进行译码,控制所述像素电阻的通电。

14.在本公开的一些实施例中,基于前述方案,所述方法还包括:

15.所述像素电路还包括多个第一晶体管,将所述第一晶体管的源极连接于电源电压线,将所述第一晶体管的栅极连接于所述译码器的输出引脚上。

16.在本公开的一些实施例中,基于前述方案,所述方法还包括:

17.所述像素电路还包括多个第二晶体管,将所述第二晶体管的源极与所述第一晶体管的漏极连接,将所述第二晶体管的栅极与所述译码器的输出端引脚连接,将所述第二晶体管的漏极与所述像素电阻连接。

18.在本公开的一些实施例中,基于前述方案,所述方法还包括:

19.将每个所述第一晶体管和与所述第一晶体管对应的第二晶体管串联。

20.根据本公开的另一个方面,提供了一种半导体存储装置,该装置包括:设置于外围区的外装构件上的封装面,在所述封装面上设置有记录层,所述封装面上具有多个像素区域,每个所述像素区域均具有对应的像素电阻;

21.设置于外围区的控制器和像素电路,所述像素电路包括多个像素电阻,所述控制器通过控制所述像素电阻进行通电,通过所述像素电阻对所述像素区域进行加热,使所述记录层显色,以在所述记录层上形成具有特定形状的标识。

22.在本公开的一些实施例中,基于前述方案,所述像素电路还包括译码器,所述译码器包括行译码器和列译码器,所述行译码器和所述列译码器分别通过各自的输出端引脚与所述控制器连接,所述行译码器和所述列译码器通过信号共同控制所述像素电阻进行通电。

23.在本公开的一些实施例中,基于前述方案,所述像素电路还包括多个第一晶体管,所述第一晶体管的源极与电源电压线连接,所述第一晶体管的栅极与所述列译码器的输出引脚连接。

24.在本公开的一些实施例中,基于前述方案,多个所述第一晶体管之间呈并联连接。

25.在本公开的一些实施例中,基于前述方案,所述像素电路还包括多个第二晶体管,所述第二晶体管的源极与所述第一晶体管的漏极连接,所述第二晶体管的栅极与所述行译码器的输出引脚连接,所述第二晶体管的漏极与所述像素电阻连接。

26.在本公开的一些实施例中,基于前述方案,多个所述第二晶体管之间呈并联连接。

27.在本公开的一些实施例中,基于前述方案,每个所述第一晶体管和与所述第一晶体管对应的第二晶体管之间呈串联连接。

28.在本公开的一些实施例中,基于前述方案,所述半导体存储装置还包括电压提供器,所述电压提供器与所述电源电压线连接,所述电压提供器为所述像素电路提供电压。

29.本公开提供的半导体存储装置的标识方法,通过将半导体存储装置中需要进行标识的单元与装置外围区设置的像素电路和控制器连接,通过控制器控制需标识单元的封面的特定区域对应的像素电路中的像素电阻进行通电发热,在需标识单元的封装面上热敏材料,通过像素电阻的发热使得热敏材料变色,从而形成了封装面上的特定标识,此种方法可使用于半导体存储装置的测试过程中,无需将需标识单元转移到激光机中进行刻印,避免了激光对需标识单元的损坏,同时提高了标识效率,进而提高了产能。

30.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

31.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1为本公开示例性实施例中的一种半导体存储装置的标识方法的流程图。

33.图2为本公开示例性实施例中的一种半导体存储装置中封装面结构爆炸图。

34.图3为本公开示例性实施例中的一种半导体存储装置的俯视示意图。

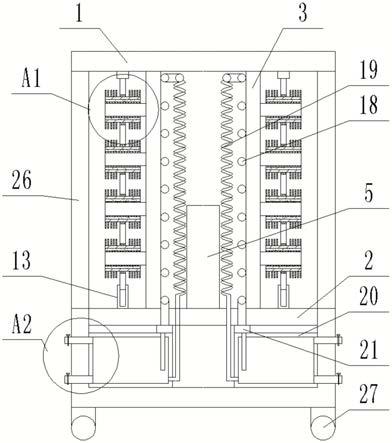

35.图4为本公开示例性实施例中的一种半导体存储装置的结构组成示意图。

36.图5为本公开示例性实施例中的一种译码器的构造和连接关系示意图。

37.图6为本公开示例性实施例中的一种译码器的电路结构示意图。

38.图7为本公开示例性实施例中的一种译码器的内部逻辑关系真值表图。

39.图8为本公开示例性实施例中的一种预设像素电路的连接关系示意图。

40.图9为本公开示例性实施例中图7的一种预设像素电路的部分连接关系示意图。

41.图10本公开示例性实施例中的一种半导体存储装置的封装面标识示意图。

42.其中,附图标记说明如下:

43.1:芯片颗粒;2:外装构件;3:存储器件;

44.10:封装面;20:记录层;30:保护层;100:像素区域;

45.101:控制器;102:译码器;103:电压提供器;

46.1021:行译码器;1022:列译码器;

47.104(q4~q11):第一晶体管;1041:第一晶体管的源极;

48.1042:第一晶体管的栅极;1043:第一晶体管的漏极;

49.105(q1~q3、q12~q72):第二晶体管;

50.1051:第二晶体管的源极;1052:第二晶体管的栅极;

51.1053:第二晶体管的漏极;106:第三晶体管;

52.a1、a2、a3:选择信号控制开关;en:使能信号控制开关;

53.y1~y8:输出端引脚;r1~r64:像素电阻。

具体实施方式

54.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本公开将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。此外,附图仅为本公开的示意性图解,并非一定是按比例绘制。

55.用语“一个”、“一”、“该”、“所述”和“至少一个”用以表示存在一个或多个要素/组成部分/等;用语“包括”和“具有”用以表示开放式的包括在内的意思并且是指除了列出的要素/组成部分/等之外还可存在另外的要素/组成部分/等;用语“第一”、“第二”和“第三”等仅作为标记使用,不是对其对象的数量限制。

56.半导体器件在生产制造过程中,一般会经过晶圆切割、芯片粘接、银浆固化、引线

焊接、注塑、固化、退火、电性测试等步骤后,需要将芯片的相关标识信息记录在芯片的表面,以便后续半导体器件在使用过程中出现故障时进行芯片故障的源头追溯,通常情况下标识信息包括厂家标志、芯片id(identity document,身份标识号码)、生产日期、生产批号等信息,现阶段芯片标识信息的标记通常会采用激光进行镭射刻字,这样就需要在器件封测完毕后,将器件有封测设备移至激光刻印设备上,通过激光的镭射刻字作用,在器件的芯片封装的表面上进行镭射刻字。

57.上述芯片标识信息的标识方法会导致芯片的生产效率降低,与此同时,由于激光标识设备中激光当量的控制不当会导致器件芯片表面甚至芯片内部的损坏,降低了产品的良率以及产能。因此,针对上述激光刻印设备标识半导体器件中芯片的标识信息的缺点,本公开提供了一种半导体存储装置的标识方法,改善了需要将器件移动至激光刻印设备中进行标识信息的刻印导致的产能低的问题。

58.本公开实施方式提供了一种半导体存储装置的标识方法,如图1所示,该标识方法包括:

59.s10:提供包括外围区的半导体存储装置,在外围区上设置有外装构件,外装构件上具有封装面;

60.s20:在封装面上形成记录层,并将封装面划分为多个像素区域;

61.s30:外围区还设置有控制器和预设的像素电路,通过控制器控制预设的像素电路中的像素电阻通电,使与通电后的像素电阻对应的像素区域显色,以在记录层上形成具有特定形状的标识。

62.其中,在步骤s10中,提供包括外围区的半导体存储装置,在外围区上设置有外装构件2,外装构件2上具有封装面。

63.本公开提供的半导体存储装置包括半导体领域中的所有半导体存储装置,如图2和图3所示,在半导体存储装置上可划分出外围区,其中在半导体存储装置包括至少一个芯片颗粒1,每个芯片颗粒1可以包括阵列区和外围区。阵列区可以包括多个存储器件3,存储器件3例如为电容结构,阵列区用于存储数据,例如通过存储器件3存储数据。外围区内包括电路结构,该电路结构用于控制阵列区内的存储器件3的读写操作。半导体存储装置的外围区还包括预设的像素电路,该预设的像素电路可以通过控制像素电阻进行通电,从而将像素电阻的电能转换为热能,使得芯片颗粒1上涂覆的热敏材料变色,显示特定形状的标识。在一些实施例中,该像素电路还可以连接外围区上的电路结构,从而可以同时对该芯片颗粒1进行测试和标识测试,从而提高测试效率。

64.此外,在半导体存储装置上还设置有对芯片颗粒1具有保护、支撑和封装作用的外装构件2,且外装构件2上均具有封装面10,封装面10的表面可用于对芯片颗粒1进行标记。在一些实施例中,外装构件2还可以同时覆盖阵列区和外围区。

65.需要说明的是,本公开对外装构件2的结构不做具体限定,外装构件2可为芯片颗粒1提供保护,还可以为封装面10的形成提供支撑作用,外装构件2的具体结构可根据实际使用需求设计,包括但不限于具有上述作用的构件。

66.其中,在步骤s20中,在封装面上形成记录层,并将封装面划分为多个像素区域。

67.本公开提供的半导体存储装置的标记方法,不同于现有的激光标记方法,是通过在半导体存储装置的芯片颗粒1的封装面10的外表面上形成记录层20,该记录层20是由热

敏材料组成,将热敏材料涂覆在芯片颗粒1封装面10的表面。

68.如图2和图3所示,在封装表面形成记录层20包括将显色剂和染色剂混合制成记录层20,将记录层20涂布在封装面10上,其中,显色剂和染色剂均为热敏材料,显色剂在高温条件下与染色剂受体作用,使染色剂的分子结构发生变化,从而使得染色剂由无色装态转变为有色状态,形成有色化合物,例如,显色剂可选用亚甲基双苯酚,染色剂可选用内酞胺环类染料,使用此种方法标记芯片颗粒1表面,显色温度远低于激光标识过程中产生的瞬时温度,有利于保护半导体存储装置中原有的电路,避免由于温度过高导致电路的损坏。

69.本公开中提供的显色剂和染色剂的初始状态均为无色状态,在受热后会有无色装状态转变为有色状态。

70.此外,在本步骤中,在封装面10上形成记录层20的同时,需要将封装面10划分多个像素区域100,像素区域100的数量可与像素电阻的数量相对应,每一个像素区域100对应像素电路中的一个像素电阻,由于封装面10上涂覆有记录层20,通过控制特定位置的像素区域100对应的像素电阻进行发热,可以使得对应像素区域100上的记录层20受热变色,从而在封装面10上显示特定的形状标识。

71.在本公开中,为了防止热敏材料变色后形成的封装面10标识发生衰退可以在记录层20上形成保护层30,保护层30可以由抗氧化剂组成,例如,miximao-30(高效化合酚),保护层30的形成可以防止芯片颗粒1上形成的标识发生衰退,保持标识的完整度。

72.需要说明的是,本公开中的记录层20和保护层30可为分别形成于芯片颗粒1的封装面10上,也可以直接将保护层30作为抗氧化剂直接添加在保护层30中形成热敏材料,具体的形成过程可以根据实际情况进行适当的调整,本公开不做具体限定。

73.其中,在步骤s30中,外围区还设置有控制器和预设的像素电路,通过控制器控制预设的像素电路中的像素电阻通电,使与通电后的像素电阻对应的像素区域显色,以在记录层上形成具有特定形状的标识。

74.在本公开中,需要在半导体存储装置的外围区内设置有控制器101和预设的像素电路,控制器101连接于像素电阻上,以芯片颗粒1在测试机台中进行标记为例,将控制器101的一端连接于测试机台上,通过测试机台的有效pin脚与像素电路中的像素电阻进行连接,控制器101控制像素电阻的通电状态,使得与通电后的像素电阻对应的像素区域100上的记录层显色,以在记录层上形成具有特定形状的标识,例如,在芯片颗粒1的封装面10上标识字母“c”,根据在封装面10上划分的像素区域100,选定可以形成“c”的多个像素区域100,通过对控制器下发编码指令,使得选定的多个像素区域100对应的多个像素电阻通电,通过像素电阻通电后发热,可以使得选定的像素区域100上的记录层显色,以达到在封装面10上显示出字母“c”的目的。

75.在本公开中,如图4所示,像素电路中还设置有译码器102,译码器102的输入端与控制器101的输出端连接,通过对控制器101发出的编程命令进行译码,以控制像素电阻的通电状态,本公开对译码器102的类型不做具体限定,需达到与控制器101配合进行译码的作用即可。

76.此外,上述外围区设置的控制器101和像素电路中的译码器102,还可以通过对控制器101进行不同的编程,以实现不同的作用,例如,通过控制器101编程命令的不同,可用于检查芯片颗粒1的表面是否被损坏。本公开提供的控制器101和电路除了用于控制像素电

阻发热以外,还可以通过其他不同的编程命令实现不同的功能,控制器101并不限于本技术的像素电阻发热作用,本公开不做具体限定。

77.此外,本公开通过像素电阻的通电后发热对像素区域进行加热后显色,根据焦耳定律和热平衡公式q=pt=mc(t2-t1)/p,可计算的出像素电阻的理想加热温度,使得像素电阻在对像素区域100加热的同时并不会超出自身的电阻极限,发生不可逆的损伤,保证像素电阻的完整性以及使用安全。

78.另外,本公开提供的像素电阻的电阻值可为8ω-12ω,可以为10ω,本公开对像素电阻的具体电阻值不做特别要求,在满足像素电阻通电后的发热值可以使得记录层显色即可,可以根据实际使用需要确定像素电阻的电阻值。

79.本公开提供的半导体存储装置的标识方法,还包括对外围区设置的像素电路,对于像素电路的连接关系如图8所示:

80.像素电路包括有多个第一晶体管104(图8中的q4~q11)和多个第二晶体管104(图8中的q1~q3、q12~q72),其中,第一晶体管的源极1041与电源电压线(vdd)连接,第一晶体管的栅极1042与列译码器102的输出端引脚连接,第一晶体管的漏极1043与第二晶体管的源极1051连接;第二晶体管的栅极1052与行译码器1021的输出端引脚连接,第二晶体管的漏极1053与像素电阻(图8中的r1~r64)连接;像素电阻(r1~r64)的另一端接地。

81.其中,在图8中,对于分别与列译码器1022的输出端引脚连接的第一晶体管104,如图8中第一晶体管q4的栅极连接于列译码器1022的输出端引脚y1,第一晶体管q5的栅极连接于列译码器1022的输出端引脚y2,以此类推,多个第一晶体管104的栅极1041分别与列译码器1022的输出端引脚y1~y8连接,且多个第一晶体管104呈并联连接,这样可以保证每个第一晶体管104的控制过程及工作过程相对与其它第一晶体管104是相互独立,互不影响的。

82.其中,在图8中,对于分别与行译码器1021的输出端引脚连接的第二晶体管105,如图8中第二晶体管q1~q3、第二晶体管q12~q16的栅极并联于行译码1021的输出端引脚y1,第二晶体管q17~q24的栅极并联于行译码器1021的输出端引脚y2,以此类推,此外,连接于行译码器1021的每一个输出端引脚上的多个第二晶体管105呈并联连接,即如图8中的行译码器1021连接的第二晶体管105在每一行和每一列中皆呈现并联连接。

83.其中,在图8中,每个第一晶体管104和与之对应的第二晶体管105呈串联连接,即行译码器1021连接的每一列第二晶体管的源极1051与对应的列译码器1022中的每一个第一晶体管的漏极1043连接,像素电路可以通过多个第一晶体管104和多个第二晶体管105的共同作用控制第二晶体管105的漏极连接的像素电阻的通电状态。

84.需要说明的是,本公开提供的行译码器1021、列译码器1022和多个第一晶体管104、多个第二晶体管105、像素电阻(r1~r64)的数量,以及排列方式和顺序,不仅限于图8中提供的结构形式,本公开仅以图8作为示例性实施例进行说明,对于上述结构的数量和排列方式等可根据具体的像素电路的需要进行确定,本公开不做具体限定。

85.下面以像素电路的结构为例进行像素电路的工作过程的说明,结合图8和图9:

86.在控制器101接收到信号后,将编程命令传输至行译码器1021和列译码器1022中,行译码器1021和列译码器1022经过对控制器101传输的编程命令进行译码,使编程命令译码为二进制编码,其中,多个第一晶体管的源极1041连接于电源电压线(vdd),vdd为多个第

一晶体管104提供工作电压,列译码器1022的每一个输出端引脚与一个第一晶体管的栅极1042连接,行译码器1021的每一个输出端引脚与多个第二晶体管的栅极1052连接,在编程命令的控制下,多个第一晶体管104中的一个或多个处于导通状态,以及多个第二晶体管105中的一个或多个处于导通状态,通过第一晶体管104和第二晶体管105的共同控制作用控制像素电阻的通电状态。

87.以图8中像素电阻r4的通电状态为例,通过列译码器1022译码的编程命令控制第一晶体管q7导通,此时,与第一晶体管q7相连的第二晶体管105所在的列处于导通状态,而后,通过行译码器1021译码的编程命令控制此列第二晶体管q12导通,此时,由于第一晶体管q7和第二晶体管q14同时处于导通状态,与第二晶体管q14的漏极1053连接的像素电阻r4处于通电状态,可以进行发热,从而对像素电阻r4对应的封装面10上的像素区域进行加热,使得此像素区域显色;若第一晶体管q7或者第二晶体管q14中的任一一个处于非导通状态,那么像素电阻r4均处于断电状态。以此类推,若需要任一像素电阻进行通电,需要同时控制此像素电阻对应的第一晶体管和第二晶体管处于导通装状态,即第一晶体管和第二晶体管同时控制像素电阻的通电状态。

88.本公开提供的半导体存储装置的标识方法,通过在半导体存储装置的芯片颗粒封装面形成记录层,通过控制装置中像素电阻的通电状态,使得像素电阻对应的像素区域的记录层显色,以达到对芯片颗粒进行标识的作用,通过本公开的方法对芯片颗粒进行标识,可以在测试机台中测试的同时实现芯片颗粒标识,无需将芯片颗粒从测试机台转移到激光标识机台中,节省了时间,提高了芯片颗粒的标识效率,从而提高了产能;此外,通过本方法标识芯片颗粒,可以避免由于激光当量过大导致的芯片颗粒损坏现象的发生,可以有效保护芯片颗粒。

89.需要说明的是,尽管在附图中以特定顺序描述了本公开中半导体存储装置的标识方法的各个步骤,但是,这并非要求或者暗示必须按照该特定顺序来执行这些步骤,或是必须执行全部所示的步骤才能实现期望的结果。附加的或备选的,可以省略某些步骤,将多个步骤合并为一个步骤执行,以及/或者将一个步骤分解为多个步骤执行等。

90.本公开实施方式还提供了一种半导体存储装置,该半导体存储装置包括:设置于外围区的外装构件上的封装面以及设置于外围区的控制器和像素电路。

91.如图4所示,本公开提供的半导体存储装置包括控制器101、译码器102,译码器102设置在半导体存储装置的外围区的像素电路中,译码器102具有输出端引脚,译码器102通过信号控制半导体存储装置的像素电阻进行通电;控制器101,控制器101配置成响应于编程命令,译码器102通过输出端引脚与控制器101连接,控制器101通过执行编程命令控制译码器102的信号。

92.其中,像素电路包括有多个第一晶体管104和多个第二晶体管105,其中,第一晶体管的源极1041与电源电压线(vdd)连接,第一晶体管的栅极1042与列译码器1022的输出端引脚连接,第一晶体管的漏极1043与第二晶体管的源极1051连接;第二晶体管的栅极1052与行译码器1021的输出端引脚连接,第二晶体的漏极1053与像素电阻连接;像素电阻的另一端接地;多个第一晶体管104呈并联,多个第二晶体管105之间呈并联,而每个第一晶体管104和与之对应的第二晶体管105之间呈串联连接。像素电路的结构及工作过程已在上文中进行了详细的说明,此处不再赘述。

93.其中,译码器102包括行译码器1021和列译码器1022,行译码器1021和列译码器1022分别具有输出端引脚,行译码器1021和列译码器1022通过各自的输出端引脚与控制器101连接,并且行译码器1021和列译码器1022通过信号共同控制像素电阻进行通电状态。

94.行译码器1021包括使能信号控制开关(en)和多个选择信号控制开关(a1~a3),控制器101端可通过控制行译码器1021中的使能信号控制开关(en)的通断来控制行译码器1021的通断,即使能信号控制开关(en)作为行译码器1021的信号输入端的总开关,若使能信号控制开关(en)处于关闭状态,则没有任何信号可以输入至行译码器1021,行译码器1021不能输出任何信号,只有在使能信号控制开关(en)处于打开状态时,控制器输出的编程命令才能通过行译码器1021进行译码和执行,行译码器1021的多个选择信号控制开关(a1~a3)用于信号选择,通过选择信号控制输出端的输出信号,同样的,列译码器1022也包括使能信号控制开关(en)和多个选择信号控制开关(a1~a3),其工作原理和结构与行译码器1021相同,此处不再赘述,通过行译码器1021和列译码器1022的共同信号控制作用,使得输出端每次输出时仅有一个选择输出端引脚为激活状态,控制器101的通电信号通过激活的引脚传输至像素电阻端,使得像素电阻通电发热,与像素电阻对应的像素区域上的记录层因发热而显色。

95.如图5所示,以行译码器1021和列译码器1022均具有一个使能信号控制开关(en)和3个选择控制信号开关(a1~a3)、具有8个输出端引脚(y1~y8)为例,行译码器1021和列译码器1022可共同控制64个单元,行译码器1021和列译码器1022可控制2

×

3个输出信号,每次输出时仅有一个引脚为激活状态。如图6所示,图6为一种列译码器的结构,如图7所示,为一种列译码器对应的真值表,结合图6和图7说明译码器102的工作原理及过程如下:

96.列译码器1022具有一个使能信号控制开关en和三个选择信号控制开关a1、a2、a3,八个输出端引脚为y1~y8,在控制器101发出控制信号,列译码器1022接收到控制信号,若控制信号中包含的信号使得en=0,那么列译码器1022就不会接收后续的控制信号,在真值表(图7)中即为前八行的数值,无论对选择控制信号开关输入任何控制信号,在列译码器1022的输出端均为0,即列译码器输出端的引脚均为不激活状态;若控制信号中包含的信号使得en=1,那么列译码器1022就会接收后续的控制信号,在真值表中即为后八行(图7)的数值,通过控制信号控制选择信号控制开关可以选择激活相应的引脚,例如,en=1时,a1=0、a2=0、a3=0,由于y1=en*bar(a1a2a3),en=1,a1=0、a2=0、a3=0,三个零取反值为1,而由于en为1,那么1和1取值为1,所以,yi输出为1,即y1=1,y2=en*a3*bar(a1a2),此时a3=0,所以y2输出为0,即y2=0,同理,可得到y3~y8的输出均为0,因此,在en=1时,a1=0、a2=0、a3=0时,列译码器1022的输出端的输出为y1=1、y2~y8=0,即仅有y1引脚为激活状态,而列译码器1022的输入信号为1000,输出信号为10000000,此时与y1引脚对应的像素电阻通电;en=1时,a1=1、a2=0、a3=0,那么,y5=1、y1~y4=0、y6~y8=0,即仅有y5引脚为激活状态,而列译码器1022的输入信号为1100,输出信号为00001000,此时与y5引脚对应的像素电阻通电;en=1时,a1=1、a2=1、a3=1,那么,y8=1、y1~y7=0,即仅有y8引脚为激活状态,而列译码器1022的输入信号为1111,输出信号为00000001,此时与y8对应的像素电阻通电;其余的输出信号和输出信号均与上述相同,此外,行译码器1021具有与列译码器1022相同的结构和原理,对于控制信号的输入和输出与列译码器1022相同,此处不再赘述。

97.需要说明的是,本公开提供的行译码器1021和列译码器1022的选择信号控制开关以及输出引脚的数量不限于上述实施例中所述的数量,可以根据像素电阻的数量选择数量对应的输出引脚,以控制像素电阻的通电状态,举例来讲,若将芯片颗粒1的封装面10划分为64个区域,对应的像素电阻为64个,此时可选用均有8个输出引脚的行译码器1021和列译码器1022,而具体的译码器102的结构形式的选择可以根据实际使用需求选用,本公开不做具体限定。

98.本公开中的译码器102的结构中,在译码器102(包括行译码器1021和列译码器1022)的输入端和输出端之间还连接有第三晶体管106,通过第三晶体管106可以控制译码器102内部电路的导通,可选地,第三晶体管106可以为场效应管,由于场效应管为电压控制器件,在控制译码器102内部电压的同时还可以控制译码器102内部电路的导通;在译码器102和像素电阻之间设置有第一晶体管104和第二晶体管105,通过第一晶体管104和第二晶体管105控制像素电阻所在的电路的通断,可选地,第一晶体管104和第二晶体管105可以为三极管或nmos管,由于三极管是电流控制器件,可以把微弱信号放大为幅度值较大的电信号的同时可以作为无触点开关,控制电流及电信号由译码器102至像素电阻的单向导通。

99.本公开中的第一晶体管104和第二晶体管105、第三晶体管106的类型并不限于上述的晶体管类型,可以是其它具有类似功能和作用的晶体管,本公开不做具体限定。

100.此外,本公开中的半导体存储装置中还包括电压提供器103,电压提供器103与电源电压线连接,电压提供器103可以为像素电路提供电压。

101.下面结合图8和图9、图10对本公开的具体实施例进行说明:

102.如打印字母“c”,将芯片颗粒1的封装面10划分多个像素区域100,本实施例以像素区域100包含64个小区域,封装面10的像素区域100划分如图10所示,相对应的64个小区域对应64个像素电阻,在图8中以符号r表示像素电阻,每个像素电阻分别与译码器102的输出端引脚连接,选用的译码器102包括行译码器1021和列译码器1022,其中行译码器1021具有一个使能信号控制开关en和三个选择信号控制开关a1、a2、a3,以及8个输出端引脚y1~y8,其中输出端引脚y1~y8与像素电阻连接,列译码器1022与行译码器1021具有相同的结构,以同样的符号表示,此处不再赘述。

103.以打印上述字母“c”的第一行(其中行方向为图10中箭头所示)为例,字母“c”的第一行需标识的像素区域分别对应于图8中像素电阻r4、像素电阻r5、像素电阻r6、像素电阻r7,通过控制器101输出编程命令,此编程命令通过译码器102进行译码后,通过译码器102的输出端(输出端引脚)输出,使特定位置的像素电阻通电,其中,在像素电阻r4需要通电时,行译码器1021的使能信号控制开关en打开,即en=1,行译码器1021的选择信号控制开关a1=0、a2=0、a3=0,其输出端(输出端引脚)y1~y8为10000000,此时,像素区域的第一行的第一晶体管104(q4~q11)全部打开,列译码器1022的使能信号控制开关en打开,即en=1,列译码器1022的选择信号控制开关a1=0、a2=1、a3=1,其输出端(输出端引脚)y1~y8为00010000,此时第二晶体管q12打开,电流流经第一晶体管q7、第二晶体管q12后到达像素电阻r4,像素电阻r4通电,对像素电阻r4对应的像素区域进行加热;在像素电阻r5需要通电时,行译码器1021的使能信号控制开关en打开,即en=1,行译码器1021的选择信号控制开关a1=0、a2=0、a3=0,其输出端(输出端引脚)y1~y8为10000000,此时,像素区域的第一行的第一晶体管104(q4~q11)全部打开,列译码器1022的使能信号控制开关en打开,即

en=1,列译码器1022的选择信号控制开关a1=1、a2=0、a3=0,其输出端(输出端引脚)y1~y8为00001000,此时第二晶体管q13打开,电流流经第一晶体管q8、第二晶体管q13后到达像素电阻r5,像素电阻r5通电,对像素电阻r5对应的像素区域进行加热;依次类推,对于像素电阻r6和像素电阻r7的通电方法同上述方法相同,当像素电阻r4、像素电阻r5、像素电阻r6、像素电阻r7同时通电后,加热相对应的像素区域,使得像素区域的记录层20受热显色,完成了对芯片颗粒1封装面10的字母“c”的第一行的标识。同理,可以根据字母“c”在芯片颗粒1封装面10上划分的像素区域的行和列的具体位置,将字母“c”的整体标识在芯片颗粒1封装面10上。

104.上述实施例仅为代表性示意,在具体的半导体装存储装置的标识过程中,可以灵活的根据实际标识需要进行适当的调整,例如,可以同时对多个像素电阻进行通电操作,也可以对不同的像素区域对应的像素电阻分别进行通电操作,本公开对此不做具体限定。

105.此外,本公开提供的半导体存储装置可以在加工测试过程中,在测试机台中测试的同时完成对芯片颗粒的标识,在装置测试过程中,可预先进行编程,当装置测试完毕后可根据预先编程的需求,在装置不同的芯片颗粒上通过输入不同的编程命令,使芯片颗粒的封装面呈现不同的顶部标识,无需将装置转移到特定的标识装置中进行标识操作,提高了生产效率。

106.虽然本说明书中使用相对性的用语,例如“上”“下”来描述图标的一个组件对于另一组件的相对关系,但是这些术语用于本说明书中仅出于方便,例如根据附图中所述的示例的方向。能理解的是,如果将图标的装置翻转使其上下颠倒,则所叙述在“上”的组件将会成为在“下”的组件。当某结构在其它结构“上”时,有可能是指某结构一体形成于其它结构上,或指某结构“直接”设置在其它结构上,或指某结构通过另一结构“间接”设置在其它结构上。

107.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和精神由所附的权利要求指出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。