1.本发明涉及一种除错系统,特别是涉及一种具有除错保护电路的除错系统。

背景技术:

2.在开发芯片的过程中,为能够有效掌握芯片的操作以进行除错(debug),常会在芯片中预留除错用的信道,例如序列除错(serial wire debug,swd)接口或联合测试工作组(joint test action group,jtag)所规范的信道。如此一来,程序开发者就可以通过这些除错信道存取芯片中内存的内容以追踪芯片的操作过程,并定位出程序异常的位置以进行除错。然而,在完成开发之后,芯片中的除错信道就可能会造成信息安全的隐患。举例来说,黑客可能会通过除错信道取得芯片内部的机密信息,甚至对芯片进行窜改,造成产品损坏或利用产品执行未授权的功能。

技术实现要素:

3.本发明的一实施例涉及一种除错系统。除错系统包括待测芯片除错控制器。待测芯片包括待测电路、除错接口、除错存取电路及除错保护电路。

4.待测电路执行特定功能。除错存取电路耦接于待测电路及除错接口。除错保护电路耦接于第一待测电路及除错存取电路。在保护功能未被启动时,除错保护电路开通除错存取电路及第一待测电路之间的通信,而在保护功能被启动时,除错保护电路阻断除错存取电路及第一待测电路之间的通信,并根据除错存取电路所传来的写入信息判断是否停止保护功能。

5.除错控制器选择性地耦接于除错接口。在保护功能被启动时,除错控制器通过除错存取电路将写入信息传送至除错保护电路,而在保护功能未被启动时,除错控制器通过除错存取电路存取待测电路的数据以对待测电路进行除错。

6.本发明的另一实施例涉及一种操作除错系统的方法。操作除错系统包括待测芯片及除错控制器,待测芯片包括除错接口、除错存取电路及除错保护电路。除错接口耦接于除错控制器及除错存取电路,除错存取电路耦接于待测芯片,除错保护电路耦接于待测芯片及除错存取电路。

7.操作除错系统的方法包括在保护功能未被启动时,除错保护电路开通除错存取电路及待测电路之间的通信,及除错控制器通过除错存取电路存取待测电路的数据以对待测电路进行除错。在保护功能被启动时,除错保护电路阻断除错存取电路及待测电路之间的通信,除错控制器通过除错存取电路将写入信息传送至除错保护电路,及除错保护电路根据除错存取电路所传来的写入信息判断是否停止保护功能。

附图说明

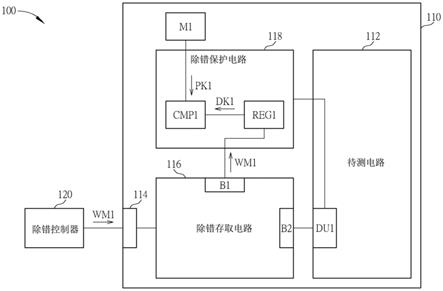

8.图1是本发明一实施例的除错系统的示意图。

9.图2是本发明另一实施例的除错系统的示意图。

10.图3是本发明一实施例的图1的除错系统的操作方法流程图。

具体实施方式

11.图1是本发明一实施例的除错系统100的示意图。除错系统100可包括待测芯片110及除错控制器120。待测芯片110可包括待测电路112、除错接口114、除错存取电路116及除错保护电路118。在一些实施例中,待测芯片110可以是开发中的芯片,而待测电路112则可以是用来执行开发中功能的区块。除错控制器120可选择性的耦接至除错接口114,例如(但不限于)通过探针(probe)耦接至除错接口114,以对待测芯片110中的待测电路112进行除错。

12.在图1中,除错存取电路116可耦接于待测电路112、除错接口114及除错保护电路118。在一些实施例中,除错存取电路116可包括控制接口b1及高速接口b2。控制接口b1可耦接至除错保护电路118,而高速接口b2可耦接至待测电路112,且高速接口b2的传输速度可大于控制接口b1的传输速度。举例来说,控制接口b1可以(但不限于)是进阶周边总线(advanced peripheral bus,apb)的接口,而高速接口b2则可以(但不限于)是进阶高性能总线(advanced high performance bus,ahb)的接口。

13.除错控制器120可以通过除错存取电路116存取到待测电路112中的数据,以对待测电路112进行除错。然而,为避免在待测芯片110完成测试或出货之后,遭到未授权者通过除错接口114任意存取或窜改待测电路112中的数据,而造成信息安全的漏洞,除错保护电路118可以执行保护功能来阻断除错存取电路116及待测电路112之间的通信。如此一来,未授权者就无法继续利用除错接口114来存取待测电路112中的信息,使得待测芯片110的信息安全能够受到保护。

14.举例来说,当保护功能未被启动时,除错保护电路118可以开通除错存取电路116及待测电路112之间的通信,此时除错控制器120可以通过除错存取电路116存取待测电路112的数据以对待测电路112进行除错。在一些实施例中,当除错控制器120完成除错的程序后,除错保护电路118便可启动保护功能。当保护功能被启动时,除错保护电路118会阻断除错存取电路116及待测电路112之间的通信。此时若除错控制器120欲对待测电路112进行除错,就需要先通过除错存取电路116向除错保护电路118传送写入信息wm1,而除错保护电路118则会根据写入信息wm1的内容判断是否停止保护功能。

15.在一些实施例中,除错控制器120可以发送写入信息wm1以将的除错密钥dk1写入除错保护电路118中的缓存器reg1,而除错保护电路118可以利用比较器cmp1来比较除错密钥dk1与其事先储存的保护密钥pk1,并根据比较结果判断是否要停止保护功能。

16.举例来说,待测电路112可以产生保护密钥pk1,并将保护密钥pk1传送至除错保护电路118,使得除错保护电路118可以在执行保护功能之前,事先储存保护密钥pk1。然而,在一些实施例中,保护密钥pk1也可由除错保护电路118自行产生。

17.此外,为避免保护密钥pk1遭到窜改,待测芯片110还可包括一次性写入(one time programmable,otp)内存m1,而除错保护电路118便可将保护密钥pk1储存在一次性写入内存m1。如此一来,就可以避免保护密钥pk1被改写。

18.在保护功能被启动时,除错保护电路118会比较除错密钥dk1及保护密钥pk1,而当除错密钥dk1及保护密钥pk1吻合时,表示除错控制器120应属于被授权的状态,此时除错保

护电路118便会开通除错存取电路116及待测电路112之间的通信以停止保护功能。反之,若除错密钥dk1与保护密钥pk1相异,则表示除错控制器120应未被授权,此时除错保护电路118仍会维持保护功能,而持续阻断除错存取电路116及待测电路112之间的通信,以免未被授权的电路存取待测电路112中的数据。

19.在一些实施例中,为避免未被授权的装置尝试连续以不同的除错密钥来破解除错保护电路118的保护功能,除错保护电路118还可以在除错控制器120连续传送预定数量的写入信息至除错保护电路118,例如(但不限于)五个写入信息,且这些写入信息中的密钥均与保护密钥pk1相异时,停止根据写入信息判断是否停止保护功能,并维持启动保护功能,以确保待测芯片110的信息安全。

20.在图1中,待测电路112可包括除错管理单元du1,除错管理单元du1可耦接于除错存取电路116及除错保护电路118。在一些实施例中,除错管理单元du1可以利用开关组件来实际制作,并且可以用来控制除错存取电路116及待测电路112之间的电性连接。如此一来,除错保护电路118就可以通过控制除错管理单元du1来阻断或开通除错存取电路116及待测电路112之间的通信。

21.然而,在有些实施中,除错管理单元du1也可以利用待测电路112中执行对应程序的控制器或处理器来实际制作。举例来说,除错程序可以支持不同类型的除错模式,例如对于待测电路112中的安全区及非安全区分别提供侵入及非侵入式的除错模式。在此情况下,除错保护电路118可以在执行保护功能时,使除错管理单元du1关闭全部的除错模式,此时待测电路112将忽略来自除错存取电路116所传来的信号,使得除错控制器120无法通过除错存取电路116与待测电路112进行通信。然而,当除错保护电路118欲停止执行保护功能时,除错保护电路118则可使除错管理单元du1开通全部或部分的除错模式,此时除错控制器120则可通过除错存取电路116与待测电路112通信。

22.图2是本发明另一实施例的除错系统200的示意图。除错系统200与除错系统100具有相似的结构并可根据相同的原理操作。然而,除错系统200的待测芯片210可包多个待测电路,例如第一待测电路212a及第二待测电路212b。第一待测电路212a及第二待测电路212b可各自耦接于除错存取电路216及除错保护电路218,并且可以分别执行不同的功能。

23.在一些实施例中,除错保护电路218可以执行第一保护功能及第二保护功能。在第一保护功能未被启动时,除错控制器220可以通过除错存取电路216存取第一待测电路212a的数据以对第一待测电路212a进行除错。当第一保护功能被启动时,除错保护电路218可阻断除错存取电路216及第一待测电路212a之间的通信。除错控制器220可以通过除错存取电路216将第一写入信息wm1传送至除错保护电路218,而除错保护电路218则可根据第一写入信息wm1判断是否停止第一保护功能。

24.相似地,在第二保护功能未被启动时,除错控制器220可以通过除错存取电路216存取第二待测电路212b的数据以对第二待测电路212b进行除错。当第二保护功能被启动时,除错保护电路218可阻断除错存取电路216及第二待测电路212b之间的通信。除错控制器220可以通过除错存取电路216将第二写入信息wm2传送至除错保护电路218,而除错保护电路218则可根据第二写入信息wm2判断是否停止第二保护功能。

25.在一些实施例中,第一保护功能及第二保护功能可以同步启动及结束,也就是说,当除错保护电路218执行第一保护功能及第二保护功能中的一个时,也会同时执行两者中

的另一个。当除错保护电路218停止执行第一保护功能及第二保护功能中的一个时,也会同时停止两者中的另一个。然而本发明并不限定须同步执行第一保护功能及第二保护功能。在一些实施例中,第一保护功能及第二保护功能可以是独立控制的。

26.举例来说,除错保护电路218中可以储存第一保护密钥pk1及第二保护密钥pk2,第一写入信息wm1中可包括第一除错密钥dk1,而第二写入信息wm2中可包括第二除错密钥dk2。在此情况下,在第一保护功能被启动时,除错保护电路218可比较第一除错密钥dk1及第一保护密钥pk1,并在第一除错密钥dk1及第一保护密钥pk1吻合时,开通除错存取电路216及第一待测电路212a之间的通信以停止第一保护功能。相似地,当第二保护功能被启动时,除错保护电路218会比较第二除错密钥dk2及第二保护密钥pk2,而当第二除错密钥dk2及第二保护密钥pk2吻合时,除错保护电路218便会开通除错存取电路216及第二待测电路212b之间的通信以停止第二保护功能。也就是说,除错保护电路218可以分开控制对于第一待测电路212a及第二待测电路212b的保护功能。

27.图3是本发明一实施例的除错系统100的操作方法300的流程图。方法300包括步骤s310至s360,但不限于图3的顺序。

28.s310:除错保护电路118储存保护密钥pk1;

29.s320:除错保护电路118开通除错存取电路116及待测电路112之间的通信;

30.s330:除错控制器120通过除错存取电路116存取待测电路112的数据以对待测电路112进行除错;

31.s340:除错保护电路118执行保护功能;

32.s342:除错保护电路118阻断除错存取电路116及待测电路112之间的通信;

33.s344:除错控制器120通过除错存取电路116将写入信息wm1传送至除错保护电路118;

34.s346:当写入信息wm1中的除错密钥dk1与保护密钥pk1吻合时,进入步骤s320,否则进入步骤s350;

35.s350:除错控制器120传送预定数量的写入信息,且包括的除错密钥dk1均与保护密钥pk1不吻合时,进入步骤s360,否则进入步骤s340;

36.s360:锁定保护功能。

37.通过方法300,除错系统100就可以在步骤s320中利用除错保护电路118开通除错存取电路116及待测电路112之间的通信,使得除错控制器120能够在步骤s330中通过除错存取电路116来存取待测电路112的数据并进行除错。在除错程序完成后,除错保护电路118可在步骤s340及s342中执行保护功能并阻断除错存取电路116及待测电路112之间的通信。而当除错控制器120欲进行除错程序时,则可传送包括除错密钥dk1的写入信息wm1至除错保护电路118,而除错保护电路118则可在步骤s346中比较除错密钥dk1与保护密钥pk1以判断是否可停止执行保护功能。

38.此外,为防止未授权者尝试连续传送不同的密钥来破解保护功能,方法300还可包括步骤s350,而在除错控制器120传送预定数量的错误密钥后,除错保护电路118将不再进行密钥的比对,并锁定保护功能,以确保待测电路112中的信息安全。

39.在一些实施例中,方法300也可应用在除错系统200中。在此情况下,方法300可以执行第一保护功能及第二保护功能来对第一待测电路212a及第二待测电路212b进行保护。

此外,第一保护功能及第二保护功能可以根据系统的需求,而设计成同步启动或是独立控制。

40.综上所述,本发明实施例所提供的除错系统及操作除错系统的方法可以利用除错保护电路来开通或阻断除错存取电路及待测电路之间的通信,因此可以防止未授权者通过除错接口存取待测电路的数据,并提升待测芯片的安全。

41.以上所述仅为本发明的较优实施例,凡依本发明申请所做的等同变化与修改,均应属本发明的保护范围。

42.附图标记说明

43.100、200:除错系统

44.110、210:待测芯片

45.120、220:除错控制器

46.112、212a、212b:待测电路

47.114:除错接口

48.116、216:除错存取电路

49.118、218:除错保护电路

50.m1:一次性写入内存

51.du1:除错管理单元

52.b1:控制接口

53.b2:高速接口

54.wm1、wm2:写入信息

55.pk1、pk2:保护密钥

56.dk1、dk2:除错密钥

57.cmp1:比较器

58.reg1:缓存器

59.300:方法

60.s310至s360:步骤

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。