1.本发明涉及一种高电子迁移率晶体管,特别是涉及一种防止栅极电极和栅极之间产生漏电的高电子迁移率晶体管以及其制作方法。

背景技术:

2.iii-v族半导体化合物由于其半导体特性而可应用于形成许多种类的集成电路装置,例如高功率场效晶体管、高频晶体管或高电子迁移率晶体管(high electron mobility transistor,hemt)。在高电子迁移率晶体管中,两种不同能带隙(band-gap)的半导体材料结合而于结(junction)形成异质结(heterojunction)而为载流子提供通道。近年来,氮化镓系列的材料由于拥有较宽能隙与饱和速率高的特点而适合应用于高功率与高频率产品。氮化镓系列的高电子迁移率晶体管由材料本身的压电效应产生二维电子气(two-dimensional electron gas,2deg),相较于传统晶体管,高电子迁移率晶体管的电子速度及密度均较高,故可用以增加切换速度。

3.然而高电子迁移率晶体管的栅极电极和电极之间经常会有漏电流发生,影响高电子迁移率晶体管的效能。

技术实现要素:

4.有鉴于此,本发明提供一种高电子迁移率晶体管的结构及其制作方法,以防止漏电流。

5.根据本发明的一优选实施例,一种高电子迁移率晶体管包含一第一iii-v族化合物层,一第二iii-v族化合物层设置于第一iii-v族化合物层上,第二iii-v族化合物层的组成与第一iii-v族化合物层不同,一栅极设置于第二iii-v族化合物层上,其中栅极包含一第一p型iii-v族化合物层、一未掺杂iii-v族化合物层和一n型iii-v族化合物层由下至上依序堆叠,第一p型iii-v族化合物层、未掺杂iii-v族化合物层、n型iii-v族化合物层和第一iii-v族化合物层由相同的第iii族和第v族元素所组成的化合物,一源极电极设置于栅极的一侧,一漏极电极设置于栅极的另一侧,一栅极电极设置栅极的正上方。

6.根据本发明的一优选实施例,一种高电子迁移率晶体管的制作方法包含依序形成一第一iii-v族化合物层、一第二iii-v族化合物层、一第一p型iii-v族化合物层、一未掺杂iii-v族化合物层和一n型iii-v族化合物层由下至上依序堆叠,其中第一p型iii-v族化合物层、未掺杂iii-v族化合物层、n型iii-v族化合物层和第一iii-v族化合物层由相同的第iii族和第v族元素所组成的化合物,然后图案化n型iii-v族化合物层、未掺杂iii-v族化合物层和第一p型iii-v族化合物层以形成一栅极,最后形成一源极电极、一漏极电极和一栅极电极,其中栅极电极位于栅极正上方,源极电极和漏极电极分别位于栅极的两侧。

7.为让本发明的上述目的、特征及优点能更明显易懂,下文特举优选实施方式,并配合所附的附图,作详细说明如下。然而如下的优选实施方式与附图仅供参考与说明用,并非用来对本发明加以限制者。

附图说明

8.图1至图3为本发明的第一较佳实施例高电子迁移率晶体管的制作方法的示意图;

9.图4是以第一优选实施例的制作工艺所制作的高电子迁移率晶体管在局部区域内的电场相对于位置的示意图;

10.图5为另一高电子迁移率晶体管在局部区域内的电场相对于位置的示意图;

11.图6为另一高电子迁移率晶体管在局部区域内的电场相对于位置的示意图;

12.图7至图8为本发明的第二优选实施例高电子迁移率晶体管的制作方法的示意图。

13.主要元件符号说明

14.10:基底

15.12:第一iii-v族化合物层

16.14:第二iii-v族化合物层

17.15:第二p型iii-v族化合物层

18.16:第一p型iii-v族化合物层

19.18:未掺杂iii-v族化合物层

20.20:n型iii-v族化合物层

21.22:栅极

22.22a:栅极

23.24:保护层

24.26:开口

25.28:源极电极

26.30:漏极电极

27.32:栅极电极

28.34:二维电子气

29.100:高电子迁移率晶体管

30.200:高电子迁移率晶体管

具体实施方式

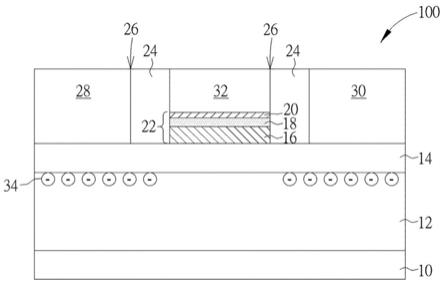

31.图1至图3为根据本发明的第一优选实施例所绘示的高电子迁移率晶体管的制作方法。

32.如图1所示,首先提供一基底10,接着依序形成一第一iii-v族化合物层12、一第二iii-v族化合物层14、一第一p型iii-v族化合物层16、一未掺杂iii-v族化合物层18和一n型iii-v族化合物层20由下至上依序堆叠,其中第一p型iii-v族化合物层16、未掺杂iii-v族化合物层18、n型iii-v族化合物层20和第一iii-v族化合物层12由相同的第iii族和第v族元素所组成的化合物。第一iii-v族化合物层12包含氮化镓,第二iii-v族化合物层14包含氮化铝镓、氮化铝铟、氮化铝铟镓或氮化铝。举例而言,第一iii-v族化合物层12可以为氮化镓,第二iii-v族化合物层14可以为n型氮化铝镓、p型氮化铝镓或是未掺杂氮化铝镓,第一p型iii-v族化合物层16为p型氮化镓,未掺杂iii-v族化合物层18未掺杂的氮化镓,n型iii-v族化合物层20为n型氮化镓。此外,根据本发明的优选实施例,第二iii-v族化合物层14为未掺杂氮化铝镓或p型氮化铝镓。另外,未掺杂iii-v族化合物层18的厚度较n型iii-v族化合

物层20的厚度大。

33.如图2所示,图案化n型iii-v族化合物层20、未掺杂iii-v族化合物层18和第一p型iii-v族化合物层16以形成一栅极22,图案化的方式可以为一蚀刻制作工艺,在蚀刻时以第二iii-v族化合物层14为停止层蚀刻n型iii-v族化合物层20、未掺杂iii-v族化合物层18和第一p型iii-v族化合物层16。然后,形成一保护层24顺应地覆盖第二iii-v族化合物层14和栅极22。

34.如图3所示,图案化保护层24以在保护层24上形成数个开口26,之后形成一源极电极28、一漏极电极30和一栅极电极32分别位于各个开口26中,其中栅极电极32位于栅极22正上方并且接触n型iii-v族化合物层20,源极电极28和漏极电极30分别位于栅极22的两侧,源极电极28和漏极电极30各自接触第二iii-v族化合物层,14,至此本发明的常关型(normally-off)的高电子迁移率晶体管100业已完成。

35.如图3所示,一种高电子迁移率晶体管100包含一基底10,一第一iii-v族化合物层12覆盖基底10,一第二iii-v族化合物层14设置于第一iii-v族化合物层12上并且接触第一iii-v族化合物层12,第二iii-v族化合物层14的组成与第一iii-v族化合物层12不同,一栅极22设置于第二iii-v族化合物层14上并且接触第二iii-v族化合物层14,栅极22由一第一p型iii-v族化合物层16、一未掺杂iii-v族化合物层18和一n型iii-v族化合物层20由下至上依序堆叠所组成,在栅极22中除了第一p型iii-v族化合物层16、未掺杂iii-v族化合物层18和n型iii-v族化合物层20之外,没有其它材料层。第一p型iii-v族化合物层16、未掺杂iii-v族化合物层18、n型iii-v族化合物层20和第一iii-v族化合物层12由相同的第iii族和第v族元素所组成的化合物。

36.第一iii-v族化合物层12包含氮化镓,第二iii-v族化合物层14包含氮化铝镓、氮化铝铟、氮化铝铟镓或氮化铝。举例而言,第一iii-v族化合物层12可以为氮化镓,第二iii-v族化合物层14可以为n型氮化铝镓、p型氮化铝镓或是未掺杂氮化铝镓,第一p型iii-v族化合物层16为p型氮化镓,未掺杂iii-v族化合物层18为未掺杂的氮化镓,n型iii-v族化合物层20为n型氮化镓。此外,根据本发明的优选实施例,第二iii-v族化合物层14为未掺杂氮化铝镓或p型氮化铝镓。另外,未掺杂iii-v族化合物层18的厚度较n型iii-v族化合物层20的厚度大。

37.根据本发明的优选实施例,第一p型iii-v族化合物层16的厚度是未掺杂iii-v族化合物层18的2至6倍,第一p型iii-v族化合物层16的厚度是n型iii-v族化合物层20的2至3倍。n型iii-v族化合物层20的厚度加上未掺杂iii-v族化合物层18的厚度是第一p型iii-v族化合物层16的厚度的2/3至1倍。

38.一源极电极28设置于栅极22的一侧并且接触第二iii-v族化合物层14,一漏极电极30设置于栅极22的另一侧并且接触第二iii-v族化合物层14,一栅极电极32设置栅极22的正上方并且接触栅极22。源极电极28、漏极电极30和栅极电极32各自包含钛、铝、镍、铂或金。一保护层24位于源极电极28和栅极22之间以及位于漏极电极30和栅极22之间,保护层24可以是介电材料,例如氧化硅、氮化硅、氮碳化硅、氮氧化硅、氮碳氧化硅或氮化铝。此外二维电子气34形成在第一iii-v族化合物12内。

39.图4是以第一优选实施例的制作工艺所制作的高电子迁移率晶体管在局部区域内的电场相对于位置的图示,其中具有相同功能的元件将使用第一优选实施例中的元件标

号。由图4中可知在未掺杂iii-v族化合物层18和第一p型iii-v族化合物层16的界面处的电场最大,也就是说在栅极电极32和n型iii-v族化合物20层界面的电场比较小,所以可以避免从栅极电极32和n型iii-v族化合物层20之间产生漏电流,此外,从n型iii-v族化合物层20至第一p型iii-v族化合物层16电场分布较平均,因此高电子迁移率晶体管100的耐压能力较高。另外利用未掺杂iii-v族化合物层18的厚度可以控制高电子迁移率晶体管100的启始电压(threshold voltage),未掺杂iii-v族化合物层18的厚度越大,高电子迁移率晶体管100的启始电压也越大。

40.图5为另一高电子迁移率晶体管在局部区域内的电场相对于位置的图示,其中具有相同功能的元件将使用第一优选实施例中的元件标号。在图5中的高电子迁移率晶体管的栅极22只由第一p型iii-v族化合物层16构成,没有未掺杂iii-v族化合物层18和n型iii-v族化合物层20。由图5中可知在栅极电极32和第一p型iii-v族化合物层16的界面处的电场最大,并且电场分布较图4中的电场分布不均匀,由于在栅极电极32和第一p型iii-v族化合物层16的界面处是最大电场,因此容易在栅极电极32和第一p型iii-v族化合物层16之间产生漏电流。此外,因为电场分布较不平均,因此只由第一p型iii-v族化合物层16构成栅极22时,高电子迁移率晶体管的耐压能力较低。

41.图6为另一高电子迁移率晶体管在局部区域内的电场相对于位置的图示,其中具有相同功能的元件将使用第一优选实施例中的元件标号。在图6中的高电子迁移率晶体管的栅极是由第一p型iii-v族化合物层16和n型iii-v族化合物层20构成,没有未掺杂iii-v族化合物层18。由图6中可知在n型iii-v族化合物层20和第一p型iii-v族化合物层16的界面处的电场最大,但相较于图4的情况,图6的电场分布较不平均,因此由n型iii-v族化合物层20和第一p型iii-v族化合物层16作为栅极22的高电子迁移率晶体管在耐压能力方面,没有以n型iii-v族化合物层20、未掺杂iii-v族化合物层18和第一p型iii-v族化合物层16作为栅极22的高电子迁移率晶体管100的耐压能力好。

42.图7至图8为根据本发明的第二优选实施例所绘示的高电子迁移率晶体管的制作方法,其中具有相同功能的元件将使用第一优选实施例中的元件标号,并且相关的元件说明请参阅第一优选实施例中的说明。

43.第二优选实施例和第一优选实施例的差别在于:在第二优选实施例中,在形成第二iii-v族化合物层14后以及形成第一p型iii-v族化合物层16之前,先形成一第二p型iii-v族化合物层15覆盖第二iii-v族化合物层14,第二p型iii-v族化合物层15和第二iii-v族化合物层14由相同的第iii族和第v族元素所组成的化合物。举例而言,若是第二iii-v族化合物层14为氮化铝镓时,第二p型iii-v族化合物层15就为p型氮化铝镓。值得注意的是第二iii-v族化合物层14和第二p型iii-v族化合物层15中的第iii族元素的比例不同。以第二iii-v族化合物层14和第二p型iii-v族化合物层15都是氮化铝镓为例,在本发明的优选实施例中第二p型iii-v族化合物层15中的铝的比例较第二iii-v族化合物层14中铝的比例少,例如第二p型iii-v族化合物层15为al

0.3

ga

0.7

n而第二iii-v族化合物层14是al

0.45

ga

0.55

n,但不限于此,在不同的需求下,第二p型iii-v族化合物层15中的铝的比例也可以较第二iii-v族化合物层14中铝的比例多。

44.在形成第二p型iii-v族化合物层15后,如同第一优选实施例的步骤,依序形成第一p型iii-v族化合物层16、未掺杂iii-v族化合物层18和n型iii-v族化合物层20由下至上

依序堆叠。如图8所示,图案化n型iii-v族化合物层20、未掺杂iii-v族化合物层18、第一p型iii-v族化合物层16和第二p型iii-v族化合物层15以形成一栅极22a,之后形成一保护层24覆盖栅极22a和第二iii-v族化合物层14,接续形成源极电极28设置于栅极22a的一侧,一漏极电极30设置于栅极22a的另一侧以及一栅极电极32设置栅极22a的正上方,至此本发明的常关型(normally-off)的高电子迁移率晶体管200业已完成。高电子迁移率晶体管200和高电子迁移率晶体管100的差别在于构成栅极22a和栅极22的材料层不同,高电子迁移率晶体管200的栅极22a相较于高电子迁移率晶体管100的栅极22多了一层第二p型iii-v族化合物层15。然而,高电子迁移率晶体管200和高电子迁移率晶体管100都具有防止栅极电极漏电以及可耐高压的特性。

45.本发明特意在栅极中外加了未掺杂iii-v族化合物层,并且选择性地加入第二p型iii-v族化合物层在栅极,如此可以避免栅极电极漏电并且提升高电子迁移率晶体管的击穿电压。

46.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。