1.本发明的实施例涉及集成电路及其形成方法。

背景技术:

2.集成电路(ic)小型化的最近趋势导致器件更小,这消耗更少的功率,但能以更高的速度提供更多功能。小型化工艺也导致了更严格的设计和制造规范以及可靠性挑战。各种电子设计自动化(eda)工具生成、优化和验证集成电路的标准单元布局设计,同时确保满足标准单元布局设计和制造规范。

技术实现要素:

3.本发明的实施例提供了一种集成电路,包括:第一类型有源区域结构与第二类型有源区域结构,位于衬底上并且在第一方向上延伸;前侧第一层导线,位于所述衬底之上的第一连接层中;多个栅极导体,位于所述第一连接层下方并且在第二方向上延伸,并且其中,两个相邻的栅极导体分隔开间距距离,所述间距距离等于接触多晶间距(“cpp”);电路单元,具有在垂直于所述第一方向的所述第二方向上延伸的第一垂直边界和第二垂直边界,其中,所述第一垂直边界和所述第二垂直边界中的每个跨越至少一个边界隔离区域,并且其中,沿着所述第一方向的所述第一垂直边界和所述第二垂直边界之间的距离小于或等于三个所述接触多晶间距;背侧水平导线,位于所述衬底下方的背侧第一导电层中并且在所述第一方向上延伸,其中,所述背侧水平导线跨越所述电路单元的所述第一垂直边界延伸;背侧垂直导线,位于所述背侧第一导电层下方的背侧第二导电层中并且在所述第二方向上延伸,其中,所述背侧垂直导线与所述第一垂直边界对准;以及引脚连接件,用于所述电路单元,直接连接在所述背侧水平导线和所述背侧垂直导线之间。

4.根据本发明的另一实施例,提供了一种集成电路,包括:第一类型有源区域结构与第二类型有源区域结构,位于衬底上并且在第一方向上延伸;前侧第一层导线,位于所述衬底之上的第一连接层中;多个栅极导体,位于所述第一连接层下方并且在第二方向上延伸,并且其中,两个相邻的栅极导体分隔开间距距离,所述间距距离等于接触多晶间距(“cpp”),电路单元,具有在垂直于所述第一方向的所述第二方向上延伸的第一垂直边界和第二垂直边界,其中,所述第一垂直边界和所述第二垂直边界中的每个跨越至少一个边界隔离区域;背侧水平导线,位于所述衬底下方的背侧第一导电层中并且在所述第一方向上延伸;背侧垂直导线,位于所述背侧第一导电层下方的背侧第二导电层中并且在所述第二方向上延伸;引脚连接件,用于所述电路单元,在所述背侧水平导线和所述背侧垂直导线之间的重叠区域处直接连接在所述背侧水平导线和所述背侧垂直导线之间;并且其中,所述背侧垂直导线具有覆盖所述重叠区域的第一部分和位于所述重叠区域外部的第二部分,并且其中,沿着所述第一方向的所述第一部分的第一宽度大于沿着所述第一方向的所述第二部分的第二宽度。

5.根据本发明的又一实施例,提供了一种形成集成电路的方法,包括:在衬底上制造

在第一方向上延伸的第一类型有源区域结构与第二类型有源区域结构;制造在垂直于所述第一方向的第二方向上延伸的多个栅极导体,其中,每个所述栅极导体与所述衬底之上的所述第一类型有源区域结构和/或所述第二类型有源区域结构相交,并且其中,两个相邻的栅极导体分隔开间距距离,所述间距距离等于接触多晶间距(cpp);在所述衬底下方的背侧第一导电层中制造在所述第一方向上延伸的背侧水平导线;制造连接至所述背侧水平导线的引脚连接件;在所述背侧第一导电层下方的背侧第二导电层中制造在所述第二方向上延伸的背侧垂直导线,其中,所述背侧垂直导线与电路单元的第一垂直边界对准,并且其中,所述引脚连接件在所述背侧水平导线与所述背侧垂直导线之间的重叠区域处直接连接在所述背侧水平导线与所述背侧垂直导线之间;并且其中,制造所述背侧水平导线包括将所述背侧水平导线制造为跨越所述电路单元的所述第一垂直边界延伸的的延伸导线,延伸的距离小于一个所述接触多晶间距。

附图说明

6.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各方面。应该注意,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

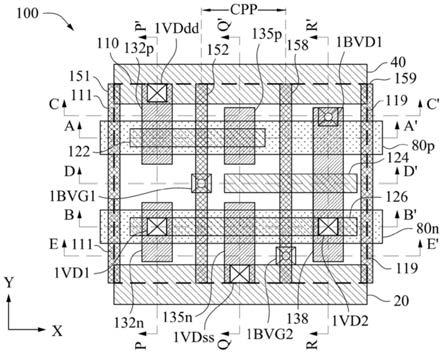

7.图1a至图1b是根据一些实施例的或非门电路的布局图。

8.图1c是根据一些实施例的由图1a至图1b中的布局图指定的或非电路的等效电路。

9.图2a至图2e是根据一些实施例的由图1a至图1b中的布局图指定的或非电路的截面图。

10.图3a至图3c是根据一些实施例的由图1a至图1b中的布局图指定的或非电路的截面图。

11.图4a至图4e是根据一些实施例的或非门电路的布局图。

12.图5a至图5b是根据一些实施例的与非门电路的布局图。

13.图6a至图6b是根据一些实施例的反相器电路的布局图。

14.图7a至图7b是根据一些实施例的反相器电路的布局图。

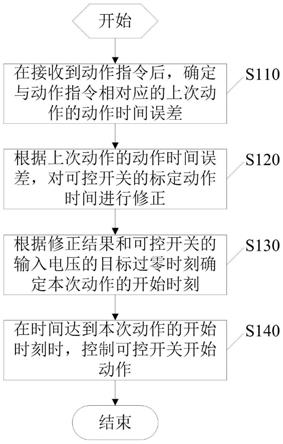

15.图8是根据一些实施例的设计集成电路的工艺的流程图。

16.图9a至图9c是根据一些实施例的单元的布局图。

17.图10是根据一些实施例的制造集成电路的方法的流程图。

18.图11是根据一些实施例的电子设计自动化(eda)系统的框图。

19.图12是根据一些实施例的集成电路(ic)制造系统和与其相关联的ic制造流程的框图。

具体实施方式

20.以下公开提供了许多用于实现所提供主题的不同特征的不同的实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成附加部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可以在各个示例中重复参

考数字和/或字母。该重复是为了简单和清楚的目的,并且其本身不指示讨论的个实施例和/或配置之间的关系。

21.此外,为了便于描述,本文中可以使用诸如“在

…

下方”、“在

…

下面”、“下部”、“在

…

之上”、“上部”等的空间相对术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作工艺中的不同方位。装置可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的空间相对描述符可以同样地作相应地解释。

22.在一些实施例中,集成电路包括位于衬底的前侧处的栅极导体和端子导体。该集成电路还包括位于衬底的背侧处的背侧第一导电层中的背侧水平导线和背侧第二导电层中的背侧垂直导线。感兴趣的背侧垂直导线与电路单元的第一垂直边界对准,并且通过引脚连接件连接至感兴趣的背侧水平导线。在一些实施例中,感兴趣的背侧水平导线是跨越电路单元的第一垂直边界延伸的延伸导线。在一些实施例中,感兴趣的背侧垂直导线是局部二维导线,它具有第一宽度的第一部分和不同于第一宽度的第二宽度的第二部分。在一些实施例中,由于延伸的导线和/或局部二维导线,为引脚连接件的定位提供了更大的灵活性而不会生成设计规则违规。

23.图1a至图1b是根据一些实施例的或非门电路100的布局图。图1a至图1b的布局图包括用于指定在x方向上延伸的p型有源区域结构80p和n型有源区域结构80n、在y方向上延伸的栅极导体(152和158)、在y方向上延伸的端子导体(132p、132n、135p、135n和138)和在y方向上延伸的伪栅极导体(151和159)的布局图案。或非门电路100位于由单元边界110界定的单元中,并且沿着x方向的单元宽度由在y方向上延伸的两个垂直单元边界111和119界定。图1a的布局图还包括用于指定在x方向上延伸的电源轨(40和20)、在x方向上延伸的前侧第一层导线(122、124和126)以及各个通孔连接件的布局图案。图1b的布局图还包括用于指定在x方向上延伸的背侧水平导线(181、182、184和186)、在y方向上延伸的背侧垂直导线(172、175和178)和各个通孔连接件的布局图案。在x-y坐标中,x方向和y方向彼此垂直。

24.在由图1a至图1b的布局图指定的或非门电路100中,两个相邻的栅极导体(诸如栅极导体152和158)分隔开等于接触多晶间距(cpp)的间距距离。在或非门电路100中,沿着x方向的垂直单元边界111和垂直单元边界119之间的距离为三个cpp。

25.图1c是根据一些实施例的由图1a至图1b中的布局图指定的或非门电路100的等效电路。图2a至图2e和图3a至图3c是根据一些实施例的由图1a至图1b中的布局图指定的或非门电路100的截面图。

26.在由图1a至图1b的布局图指定的或非门电路100中和如图1c的等效电路所示,栅极导体152在p型晶体管pa1的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na1的沟道区域处与n型有源区域结构80n相交。栅极导体158在p型晶体管pa2的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na2的沟道区域处与n型有源区域结构80n相交。端子导体132p和135p在p型晶体管pa2和pa1的各个源极/漏极区域处与p型有源区域结构80p相交。端子导体132n和135n在n型晶体管na2和na1的各个源极/漏极区域处与n型有源区域结构80n相交。端子导体138在p型晶体管pa1的漏极区域处和n型晶体管na1的漏极区域处相应地与p型有源区域结构80p和n型有源区域结构80n相交。p型晶体管(pa1和pa2)和n型晶体管(na1和na2)的非限制性示例包括finfet、纳米片晶体管和纳米线晶体管。用于图1a

至图1b中的伪栅极导体151和159的布局图案指定,或非门电路100中的有源区域(诸如,源极区域、漏极区域和沟道区域)与相邻单元中的有源区域隔离。

27.在由图1a至图1b的布局图指定的或非门电路100中和如图1c的等效电路所示,前侧第一层导线(122、124和126)和电源轨(40和20)位于衬底之上的第一连接层中。在一些实施例中,第一连接层是在前段制程(feol)工艺中制造的顶部绝缘层之上的第一金属层m0。在或非门电路100中,端子导体132p通过通孔连接件1vddd导电连接至电源轨40,并且电源轨40配置为提供第一电源电压vdd。端子导体135n通过通孔连接件1vdss导电连接至电源轨20,并且电源轨20配置为提供第二电源电压vss。前侧第一层导线126通过通孔连接件1vd1导电连接至端子导体132n,并且通过通孔连接件1vd2导电连接至端子导体138。

28.在或非门电路100中,端子导体138(图1a中)还通过穿过衬底的通孔连接件1bvd1导电连接至背侧水平导线182(图1b中)。此外,栅极导体152(图1a中)通过通孔连接件1bvg1导电连接至背侧水平导线184(图1b中),并且栅极导体158(图1a中)通过通孔连接件1bvg2导电连接至背侧水平导线186(在图1b中)。

29.在或非门电路100中,背侧水平导线182通过通孔连接件1bv0a导电连接至背侧垂直导线178。背侧水平导线184通过通孔连接件1bv0b导电连接至背侧垂直导线172。背侧水平导线186通过通孔连接件1bv0c导电连接至背侧垂直导线175。

30.在或非门电路100中,背侧水平导线181、182、184和186位于衬底下方的背侧第一导电层中。背侧垂直导线172、175和178位于背侧第一导电层下方的背侧第二导电层中。在一些实施例中,背侧第一导电层是在衬底的背侧处制造的第一背侧金属层bm0,并且背侧第二导电层是在衬底的背侧处制造的第二背侧金属层bm1。第一背侧金属层bm0夹在衬底与第二背侧金属层bm1之间。通孔连接件1bv0a、1bv0b和1bv0c中的每个是穿过将第二背侧金属层bm1和第一背侧金属层bm0分隔开的层间介电(ild)材料的通孔连接件bv0。

31.在或非门电路100中,背侧垂直导线172、通孔连接件1bv0b和背侧水平导线184导电连接在一起以承载或非门电路100的输入信号“a1”。背侧垂直导线175、通孔连接件1bv0c和背侧水平导线186导电连接在一起以承载或非门电路100的输入信号“a2”。背侧垂直导线178、通孔连接件1bv0a和背侧水平导线182导电连接在一起以承载或非门电路100的输出信号“zn”。

32.在或非门电路100中,通孔连接件1bv0a(如图1c所示)用作在z方向上延伸的引脚连接件,用于将背侧垂直导线178连接至背侧水平导线182以承载或非门电路100的输出信号“zn”。在一些实施例中,如图1b所示,当背侧水平导线182跨越垂直单元边界119延伸时,为引脚连接件(即,通孔连接件1bv0a)的定位提供了更大的灵活性,而不会生成设计规则违规。在图1b中,背侧水平导线182跨越垂直单元边界119延伸了在x方向上延伸的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的八分之一的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的四分之一的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的一半的距离“δ”。在一些实施例中,距离“δ”选择为足够大以减轻与背侧垂直导线178和背侧水平导线182之间的引脚连接件连接相关联的设计规则违规。在一些实施例中,距离“δ”选择为小于一个cpp,使得从垂直单元边界119到相邻单元的垂直单元边界的水平间隙距离减小到最小距离以减轻与引脚连接件连接相关联

的设计规则违规。

33.在图1b中,背侧垂直导线178具有在x方向上延伸的宽度“w”。在一些实施例中,选择宽度“w”以减小背侧垂直导线178中的ir降。在一些实施例中,背侧垂直导线178的宽度“w”大于cpp的一半。在一些实施例中,背侧垂直导线178的宽度“w”大于cpp的四分之三。通常,宽度“w”越大,背侧垂直导线178中的ir降越小。然而,相邻背侧垂直导线之间的间距要求限制了宽度“w”的最大值,如果单元中的用于背侧垂直导线的轨道的数量是固定的。减少轨道的数量可能会增大宽度“w”的最大值,但同时也会降低单元设计的路由灵活性。在一些实施例中,路由灵活性和ir降要求之间的折衷确定宽度“w”的最大值。

34.图2a是根据一些实施例的在切割平面a-a’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图2a所示,p型有源区域结构80p位于衬底50上。端子导体132p、135p和138中的每个与p型有源区域结构80p相交。栅极导体152和158中的每个也与p型有源区域结构80p相交。在一些实施例中,p型有源区域结构80p中的有源区域(诸如,源极区域、沟道区域或漏极区域)通过伪栅极导体151下方的边界隔离区域151i和伪栅极导体159下方的边界隔离区域159i与相邻单元中的有源区域隔离。前侧第一层导线122位于绝缘层52上面,绝缘层52覆盖栅极导体(152和158)的和端子导体(132p、135p和138)。背侧垂直导线172、175和178位于背侧层间电介质56上,该背侧层间电介质56位于衬底50的背侧处的背侧层间电介质54上面。

35.图2b是根据一些实施例的在切割平面b-b’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图2b所示,n型有源区域结构80n位于衬底50上。端子导体132n、135n和138中的每个与n型有源区域结构80n相交。栅极导体152和158中的每个也与n型有源区域结构80n相交。在一些实施例中,n型有源区域结构80n中的有源区域(诸如,源极区域、沟道区域或漏极区域)通过伪栅极导体151下方的边界隔离区域151i和伪栅极导体159下方的边界隔离区域159i与相邻单元中的有源区域隔离。前侧第一层导线126位于绝缘层52上面,绝缘层52覆盖栅极导体(152和158)和端子导体(132n、135n和138)。背侧垂直导线172、175和178位于背侧层间电介质56上,该背侧层间电介质56位于衬底50的背侧处的背侧层间电介质54上面。

36.图2c是根据一些实施例的在切割平面c-c’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图2c所示,绝缘层52覆盖栅极导体(152和158)、端子导体(132p、135p和138)和伪栅极导体(151和159)。背侧水平导线181和182位于衬底50的背侧处。背侧层间电介质54的部分将背侧水平导线181与背侧水平导线182分隔开。背侧垂直导线172、175和178位于背侧层间电介质56上,背侧层间电介质56覆盖背侧层间电介质54和背侧水平导线181和182。通孔连接件1bvd1穿过衬底50并且将端子导体138与背侧水平导线182导电连接。通孔连接件1bv0a穿过背侧层间电介质56并且将背侧水平导线182与背侧垂直导线178导电连接。

37.图2d是根据一些实施例的在切割平面d-d’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图2d所示,绝缘层52覆盖栅极导体(152和158)、端子导体138和伪栅极导体(151和159)。背侧水平导线184位于衬底50的背侧处。背侧垂直导线172、175和178位于背侧层间电介质56上,背侧层间电介质56覆盖背侧层间电介质54和背侧水平导线184。通孔连接件1bvg1穿过衬底50并且将栅极导体152与背侧水平导线184导电连接。通孔

连接件1bv0b穿过背侧层间电介质56并且将背侧水平导线184与背侧垂直导线172导电连接。

38.图2e是根据一些实施例的在切割平面e-e’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图2e所示,绝缘层52覆盖栅极导体(152和158)、端子导体(132n、135n和138)和伪栅极导体(151和159)。背侧水平导线186位于衬底50的背侧处。背侧垂直导线172、175和178位于背侧层间电介质56上,背侧层间电介质56覆盖背侧层间电介质54和背侧水平导线186。通孔连接件1bvg2穿过衬底50并且将栅极导体158与背侧水平导线186导电连接。通孔连接件1bv0c穿过背侧层间电介质56并且将背侧水平导线186与背侧垂直导线175导电连接。

39.图3a是根据一些实施例的在切割平面p-p’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图3a所示,端子导体132n与衬底50上的n型有源区域结构80n相交,并且端子导体132p与衬底50上的p型有源区域结构80p相交。绝缘层52覆盖端子导体132n和132p。电源轨(40和20)以及前侧第一层导线122和126位于绝缘层52上面的第一连接层中。通孔连接件1vddd穿过绝缘层52并且将端子导体132p与电源轨40导电连接。背侧水平导线181、184和186位于衬底50的背侧处。背侧层间电介质54与背侧水平导线181、184和186由背侧层间电介质56覆盖。背侧垂直导线172位于背侧层间电介质56上面。通孔连接件1bv0b穿过背侧层间电介质56并且将背侧水平导线184与背侧垂直导线172导电连接。

40.图3b是根据一些实施例的在切割平面q-q’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图3b所示,端子导体135n与衬底50上的n型有源区域结构80n相交,并且端子导体135p与衬底50上的p型有源区域结构80p相交。绝缘层52覆盖端子导体135n和135p。电源轨(20和40)与前侧第一层导线122、124和126位于绝缘层52上面的第一连接层中。通孔连接件1vdss穿过绝缘层52并且将端子导体135n与电源轨20导电连接。背侧水平导线184和186位于衬底50的背侧处。背侧层间电介质54与背侧水平导线184和186由背侧层间电介质56覆盖。背侧垂直导线175位于背侧层间电介质56上面。通孔连接件1bv0c穿过背侧层间电介质56并且将背侧水平导线186与背侧垂直导线175导电连接。

41.图3c是根据一些实施例的在切割平面r-r’中的由图1a至图1b中的布局图指定的或非门电路100的截面图。如图3c所示,端子导体138与衬底50上的n型有源区域结构80n和p型有源区域结构80p相交。绝缘层52覆盖端子导体138。电源轨(20和40))与前侧第一层导线124和126位于绝缘层52上面的第一连接层中。背侧水平导线182、184和186位于衬底50的背侧处。通孔连接件1bvd1穿过衬底50并且将端子导体138与背侧水平导线182导电连接。背侧层间电介质54与背侧水平导线182、184和186由背侧层间电介质56覆盖。背侧垂直导线178位于背侧层间介电层56上面。通孔连接件1bv0a穿过背侧层间介电层56并且将背侧水平导线182与背侧垂直导线178导电连接。

42.在由图1a至图1b的布局图指定的或非门电路100中,背侧垂直导线178在衬底50的背侧处具有均匀的宽度“w”。在一些可选实施例中,至少一条背侧垂直导线包括具有第一宽度的第一部分和具有第二宽度的第二部分,并且第一部分的第一宽度大于第二部分的第二宽度。作为示例,在由图4a至图4b的布局图指定的或非门电路中(在下面更详细地描述),背侧垂直导线178的第一部分具有第一宽度“wa”,并且背侧垂直导线178的第二部分具有第二宽度“wb”,其中第一宽度“wa”大于第二宽度“wb”。

43.图4a至图4e是根据一些实施例的或非门电路400的布局图。图4a至图4e中的布局图的每个包括用于指定背侧水平导线(181、182、184和186)和背侧垂直导线(172、175和178)的布局图案。衬底的背侧处的或非门电路400中的元件的布局(如图4a至图4e所示)与衬底的背侧处的或非门电路100中的元件的布局(如图1b所示)不同。然而,衬底的前侧处的或非门电路400中的元件的布局与衬底的前侧处的或非门电路100中的元件的布局相同(如图1a所示)。因此,对于或非门电路400,仅参考图4a至图4e的布局图详细描述衬底的背侧处的元件的布局,并且不再参考前侧布局图描述前侧处的元件的布局。

44.如图4a至图4e中的布局图所指定的,或非门电路400包括位于衬底下方的背侧第一导电层中的背侧水平导线181、182、184和186。或非门电路400还包括位于背侧第一导电层下方的背侧第二导电层中的背侧垂直导线172、175和178。栅极导体152通过通孔连接件1bvg1导电连接至背侧水平导线184,并且背侧水平导线184通过通孔连接件1bv0b导电连接至背侧垂直导线172。栅极导体158通过通孔连接件1bvg2导电连接至背侧水平导线186,并且背侧水平导线186通过通孔连接件1bv0c导电连接至背侧垂直导线175。端子导体138(在图1a中)通过通孔连接件1bvd1导电连接至背侧水平导线182,并且背侧水平导线182通过通孔连接件1bv0a导电连接至背侧垂直导线178。

45.如由图4a至图4e的布局图所指定的,在或非门电路400中,背侧垂直导线178包括第一部分178a和第二部分178b。第一部分178a覆盖背侧水平导线182和背侧垂直导线178之间的重叠区域,而第二部分178b位于重叠区域外部。第一部分178a具有第一宽度“wa”,并且第二部分具有第二宽度“wb”。第一宽度“wa”大于第二宽度“wb”。在一些实施例中,第一宽度“wa”比第二宽度“wb”大超过一个cpp的八分之一的量。在一些实施例中,第一宽度“wa”比第二宽度“wb”大超过一个cpp的四分之一的量。在一些实施例中,第一宽度“wa”比第二宽度“wb”足够大以允许引脚连接件1bv0a的定位而不生成设计规则违规。在一些实施例中,为单元宽度小于或等于三个cpp的电路单元定位引脚连接件的灵活性提高了集成电路设计中的布局区域覆盖率。

46.在一些实施例中,诸如在图4a的或非门电路400中,背侧水平导线182跨越垂直单元边界119延伸了在x方向上延伸的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的八分之一的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的四分之一的距离“δ”。在一些实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp但大于cpp的一半的距离“δ”。在一些实施例中,距离“δ”选择为足够大以减轻与背侧垂直导线178和背侧水平导线182之间的引脚连接件连接相关联的设计规则违规。在一些实施例中,距离“δ”选择为小于一个cpp,使得从垂直单元边界119到相邻单元的垂直单元边界的水平间隙距离减小到最小距离以减轻与引脚连接件连接相关联的设计规则违规。

47.在一些实施例中,诸如在图4b的或非门电路400中,背侧水平导线182跨越垂直单元边界119延伸。在一些实施例中,诸如在图4c的或非门电路400中,背侧垂直导线178的第一部分178a跨越垂直单元边界119延伸,而背侧垂直导线178的第二部分178b不跨越垂直单元边界119延伸。在一些实施例中,诸如在图4d的或非门电路400中,背侧垂直导线178的第一部分178a和第二部分178b都跨越垂直单元边界119延伸。

48.在一些实施例中,诸如在图4e的或非门电路400中,虽然背侧垂直导线178不跨越

垂直单元边界119延伸,但第一部分178a的第一宽度“wa”增大,以提供将引脚连接件(即,通孔连接件1bv0a)定位在背侧水平导线182上的更大灵活性。此外,也修改背侧垂直导线175(与背侧垂直导线178相邻),以避免设计规则违规。

49.图5a至图5b是根据一些实施例的与非门电路500的布局图。图5a至图5b的布局图包括用于指定p型有源区域结构80p和n型有源区域结构80n、栅极导体(552和558)、端子导体(532p、532n、535p、535n和538)以及伪栅极导体(151和159)的布局图案。与非门电路500位于由单元边界110界定的单元中,并且单元宽度由两个垂直单元边界111和119界定。图5a的布局图还包括用于指定电源轨(40和20)、前侧第一层导线(522、524和526)和各个通孔连接件的布局图案。图5b的布局图还包括用于指定背侧水平导线(581、582、584和586)、背侧垂直导线(572、575和578)和各个通孔连接件的布局图案。

50.在由图5a至图5b的布局图指定的与非门电路500中,栅极导体552在p型晶体管pa1的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na1的沟道区域处与n型有源区域结构80n相交。栅极导体558在p型晶体管pa2的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na2的沟道区域处与n型有源区域结构80n相交。端子导体532p和535p在p型晶体管pa2和pa1的各个源极/漏极区域处与p型有源区域结构80p相交。端子导体532n和535n在n型晶体管na2和na1的各个源极/漏极区域处与n型有源区域结构80n相交。端子导体538在p型晶体管pa1的漏极区域处和在n型晶体管na1的漏极区域处相应地与p型有源区域结构80p和n型有源区域结构80n相交。

51.在由图5a至图5b的布局图指定的与非门电路500中,前侧第一层导线(522、524和526)和电源轨(40和20)位于衬底之上的第一连接层中。在与非门电路500中,端子导体535p通过通孔连接件5vddd导电连接至电源轨40,并且电源轨40配置为提供第一电源电压vdd。端子导体532n通过通孔连接件5vdss导电连接至电源轨20,并且电源轨20配置为提供第二电源电压vss。前侧第一层导线522通过通孔连接件5vd1导电连接至端子导体532p,并且通过通孔连接件5vd2导电连接至端子导体538。

52.在与非门电路500中,端子导体538(图5a中)还通过穿过衬底的通孔连接件5bvd1导电连接至背侧水平导线582(图5b中)。此外,栅极导体552(图5a中)通过通孔连接件5bvg1导电连接至背侧水平导线584(图5b中),并且栅极导体558(图5a中)通过通孔连接件5bvg2导电连接至背侧水平导线586(在图5b中)。

53.在与非门电路500中,背侧水平导线582通过通孔连接件5bv0a导电连接至背侧垂直导线578。背侧水平导线584通过通孔连接件5bv0b导电连接至背侧垂直导线572。背侧水平导线586通过通孔连接件5bv0c导电连接至背侧垂直导线575。在与非门电路500中,背侧水平导线581、582、584和586位于衬底下方的背侧第一导电层中。背侧垂直导线572、575和578位于背侧第一导电层和衬底50下方的背侧第二导电层中。

54.在与非门电路500中,背侧垂直导线572、通孔连接件5bv0b和背侧水平导线584导电连接在一起以承载与非门电路500的输入信号“a1”。背侧垂直导线575、通孔连接件5bv0c和背侧水平导线586导电连接在一起以承载与非门电路500的输入信号“a2”。背侧垂直导线578、通孔连接件5bv0a和背侧水平导线582导电连接在一起以承载与非门电路500的输出信号“zn”。

55.在与非门电路500中,通孔连接件1bv0a用作在z方向上延伸的引脚连接件,用于将

背侧垂直导线578连接至背侧水平导线582以承载与非门电路500的输出信号“zn”。在一些实施例中,当背侧水平导线582跨越垂直单元边界119延伸时,为引脚连接件(即,通孔连接件1bv0a)的定位提供了更大的灵活性,而不会生成设计规则违规。在图5b中,背侧水平导线582沿着x方向跨越垂直单元边界119延伸距离“δ”。在一些实施例中,背侧水平导线582跨越垂直单元边界119延伸小于一个cpp的距离“δ”。在一些实施例中,背侧水平导线582跨越垂直单元边界119延伸超过cpp的八分之一、cpp的四分之一或cpp的二分之一的距离“δ”。在一些实施例中,距离“δ”选择为足够大以减轻与背侧垂直导线578和背侧水平导线582之间的引脚连接件连接相关联的设计规则违规。在一些实施例中,距离“δ”选择为小于一个cpp,使得从垂直单元边界119到相邻单元的垂直单元边界的水平间隙距离减小到最小距离以减轻与引脚连接件连接相关联的设计规则违规。

56.图6a至图6b是根据一些实施例的反相器电路600的布局图。图6a至图6b的布局图包括用于指定p型有源区域结构80p和n型有源区域结构80n、栅极导体(652和658)、端子导体(632、635p、635n和638)和伪栅极导体(151和159)的布局图案。反相器电路600位于由单元边界110界定的单元中,并且单元宽度由两个垂直单元边界111和119界定。图6a的布局图还包括用于指定电源轨(40和20)、前侧第一层导线(622、624和626)和各个通孔连接件的布局图案。图6b的布局图还包括用于指定背侧水平导线(681、682、684和686)、背侧垂直导线(672、675和678)和各个通孔连接件的布局图案。

57.在由图6a至图6b的布局图指定的反相器电路600中,栅极导体652在p型晶体管pa1的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na1的沟道区域处与n型有源区域结构80n相交。栅极导体658在p型晶体管pa2的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管na2的沟道区域处与n型有源区域结构80n相交。端子导体635p在p型晶体管pa2和pa1的源极区域处与p型有源区域结构80p相交。端子导体635n在n型晶体管na2和na1的源极区域处与n型有源区域结构80n相交。端子导体632在p型晶体管pa1的漏极区域和n型晶体管na1的漏极区域处相应地与p型有源区域结构80p和n型有源区域结构80n相交。端子导体638在p型晶体管pa2的漏极区域和n型晶体管na2的漏极区域处相应地与p型有源区域结构80p和n型有源区域结构80n相交。

58.在由图6a至图6b的布局图指定的反相器电路600中,前侧第一层导线(622、624和626)和电源轨(40和20)位于衬底之上的第一连接层中。在反相器电路600中,端子导体635p通过通孔连接件6vddd导电连接至电源轨40,并且电源轨40配置为提供第一电源电压vdd。端子导体635n通过通孔连接件6vdss导电连接至电源轨20,并且电源轨20配置为提供第二电源电压vss。前侧第一层导线626通过通孔连接件6vd1导电连接至端子导体632,并且通过通孔连接件6vd2导电连接至端子导体638。

59.在反相器电路600中,端子导体638(图6a中)还通过穿过衬底的通孔连接件6bvd1导电连接至背侧水平导线682(图6b中)。此外,背侧水平导线684(图6b中)通过通孔连接件6bvg1导电连接至栅极导体652,并且通过通孔连接件6bvg2导电连接至栅极导体658。

60.在反相器电路600中,背侧水平导线682通过通孔连接件6bv0a导电连接至背侧垂直导线678。背侧水平导线684通过通孔连接件6bv0b导电连接至背侧垂直导线672。在反相器电路600中,背侧水平导线681、682、684和686位于衬底下方的背侧第一导电层中。背侧垂直导线672、675和678位于背侧第一导电层下方的背侧第二导电层中。在反相器电路600中,

背侧垂直导线672用作反相器电路600的输入节点“in”。背侧垂直导线678用作反相器电路600的输出节点“zn”。

61.在反相器电路600中,通孔连接件6bv0a用作在z方向上延伸的引脚连接件,用于将背侧垂直导线678连接至背侧水平导线682以承载反相器电路600的输出信号“zn”。在一些实施例中,当背侧水平导线682跨越垂直单元边界119延伸时,为引脚连接件(即,通孔连接件6bv0a)的定位提供更大的灵活性,而不会生成设计规则违规。在图6b中,背侧水平导线682跨越垂直单元边界119延伸了在x方向上延伸的距离“δ”。在一些实施例中,背侧水平导线682跨越垂直单元边界119延伸小于一个cpp的距离“δ”。在一些实施例中,背侧水平导线682跨越垂直单元边界119延伸超过cpp的八分之一、cpp的四分之一或cpp的二分之一的距离“δ”。在一些实施例中,距离“δ”选择为足够大以减轻与背侧垂直导线678和背侧水平导线682之间的引脚连接件连接相关联的设计规则违规。在一些实施例中,距离“δ”选择为小于一个cpp,使得从垂直单元边界119到相邻单元的垂直单元边界的水平间隙距离减小到最小距离以减轻与引脚连接件连接相关联的设计规则违规.

62.图7a至图7b是根据一些实施例的反相器电路700的布局图。图7a至图7b的布局图包括用于指定p型有源区域结构80p和n型有源区域结构80n、栅极导体758、端子导体(735p、735n和738)和伪栅极导体(151和159)的布局图案。反相器电路700位于由单元边界110界定的单元中,并且单元宽度由两个垂直单元边界111和119界定。图7a的布局图还包括用于指定电源轨(40和20)、前侧第一层导线(722、724和726)和各个通孔连接件的布局图案。图7b的布局图还包括用于指定背侧水平导线(782、784和786)、背侧垂直导线(775和778)和各个通孔连接件的布局图案。

63.在由图7a至图7b的布局图指定的反相器电路700中,栅极导体758在p型晶体管tp的沟道区域处与p型有源区域结构80p相交,并且在n型晶体管tn的沟道区域处与n型有源区域结构80n相交。端子导体735p在p型晶体管tp的源极区域处与p型有源区域结构80p相交。端子导体735n在n型晶体管tn的源极区域处与n型有源区域结构80n相交。端子导体738在p型晶体管tp的漏极区域处和n型晶体管tn的漏极区域处相应地与p型有源区域结构80p和n型有源区域结构80n相交。

64.在由图7a至图7b的布局图指定的反相器电路700中,前侧第一层导线(722、724和726)和电源轨(40和20)位于衬底之上的第一连接层中。在反相器电路700中,端子导体735p通过通孔连接件7vddd导电连接至电源轨40,并且电源轨40配置为提供第一电源电压vdd。端子导体735n通过通孔连接件7vdss导电连接至电源轨20,并且电源轨20配置为提供第二电源电压vss。

65.在反相器电路700中,端子导体738(图7a中)还通过穿过衬底的通孔连接件7bvd1导电连接至背侧水平导线782(图7b中)。此外,栅极导体758通过通孔连接件7bvg1导电连接至背侧水平导线784。

66.在反相器电路700中,背侧水平导线782通过通孔连接件7bv0a导电连接至背侧垂直导线778。背侧水平导线784通过通孔连接件7bv0b导电连接至背侧垂直导线775。在反相器电路700中,背侧水平导线782、784和786位于衬底下方的背侧第一导电层中。背侧垂直导线772、775和778位于背侧第一导电层下方的背侧第二导电层中。在反相器电路700中,背侧垂直导线775用作反相器电路700的输入节点“in”。背侧垂直导线778用作反相器电路700的

输出节点“zn”。

67.在反相器电路700中,通孔连接件7bv0a用作在z方向上延伸的引脚连接件,用于将背侧垂直导线778连接至背侧水平导线782,以承载反相器电路700的输出信号“zn”。在一些实施例中,当背侧水平导线782跨越垂直单元边界119延伸时,为引脚连接件(即,通孔连接件7bv0a)的定位提供了更大的灵活性,而不会生成设计规则违规。在一些实施例中,为具有小于或等于两个cpp的单元宽度的电路单元定位引脚连接件的灵活性提高了集成电路设计中的布局区域覆盖率。在图7b中,背侧水平导线782跨越垂直单元边界119延伸了在x方向上延伸的距离“δ”。在一些实施例中,背侧水平导线782跨越垂直单元边界119延伸小于一个cpp的距离“δ”。在一些实施例中,背侧水平导线782跨越垂直单元边界119延伸超过cpp的八分之一、cpp的四分之一或cpp的二分之一的距离“δ”。在一些实施例中,距离“δ”选择为足够大以减轻与背侧垂直导线778和背侧水平导线782之间的引脚连接件连接相关联的设计规则违规。在一些实施例中,距离“δ”选择为小于一个cpp,使得从垂直单元边界119到相邻单元的垂直单元边界的水平间隙距离减小到最小距离以减轻与引脚连接件连接相关联的设计规则违规。

68.图8是根据一些实施例的设计集成电路的工艺800的流程图。作为示例,参考图9a至图9c的布局图解释图8中的工艺800。图9a至图9c是根据一些实施例的单元900的布局图。如图9a至图9c所示,单元900包括第一背侧金属层bm0中的背侧水平导线(981、982、984和986)和第二背侧金属层bm1中的背侧垂直导线(972、975和978)。通孔连接件1bv0a(用作引脚连接件)将背侧垂直导线978连接至背侧水平导线982。

69.在图8中,工艺800从设计流程的第一部分805开始。第一部分805包括在背侧导线的放置和路由之前的设计操作。设计流程的第一部分805中的示例操作包括衬底的前侧处的各种元件的布局规划、分区、电源规划以及放置和路由。在工艺800完成设计流程的第一部分805之后,工艺800进行到操作810,对各种背侧导线进行自动放置和路由(apr)。然后,在操作810之后,工艺800进行到操作820,对背侧导线的布局设计进行设计规则检查(drc)。布局设计的设计规则是对布局设计施加的几何约束,以确保基于布局设计的相应电路能够正常可靠地运行,并且相应的电路也可以以可接受的良率生产。进行设计规则检查以确保布局设计不违反设计规则。如果背侧导线的布局设计通过了设计规则检查,则工艺800进行到设计流程的剩余部分895。另一方面,如果背侧导线的布局设计未能通过设计规则检查,则工艺800进行到操作832。drc故障的一个示例是当两条背侧导线之间的分隔间距变得太小时。drc故障的另一个示例是当引脚连接件的位置太靠近背侧导线的边缘时。

70.在操作832中,分析单元900附近的布局区域(在操作820处发现单元900具有至少一个设计规则违规)以确定单元900的位置是否可以移动。如果单元900的位置可以移动,则工艺800进行到操作838以修复设计规则违规,并且单元900的位置在修改的布局设计中从原始位置移动到可选位置。例如,在如图9a所示的修改的布局设计中,单元900从原始位置902移动到可选位置908。另一方面,在操作832中,如果单元900的位置不能移动,则工艺800进行到操作834。

71.在操作834中,分析单元900附近的布局区域(在操作820发现单元900具有至少一个设计规则违规)以确定用于支持引脚访问的背侧水平导线是否可以延伸。如果背侧水平导线可以延伸,则工艺800进行到操作838以修复设计规则违规,并且将背侧水平导线重新

设计为在修改的布局设计中跨越垂直单元边界延伸的延伸导线。例如,在如图9b所示的修改的布局设计中,背侧水平导线982(作为延伸的导线)跨越垂直单元边界119延伸距离“δ”。另一方面,在操作834中,如果用于支持引脚访问的背侧水平导线不能延伸,则工艺800进行到操作836。

72.在操作836中,将用于通过引脚连接件访问电路节点的背侧垂直导线在修改的布局设计中重新设计为局部二维导线,并且工艺800进行到操作838。局部两个三维导线具有第一宽度的第一部分和不同于第一宽度的第二宽度的第二部分。例如,在如图9c所示的修改的布局设计中,背侧垂直导线978具有第一部分978a和第二部分978b。第一部分978a具有第一宽度“wa”,并且第二部分978b具有小于第一宽度“wa”的第二宽度“wb”。此外,在如图9c所示的修改的布局设计中,也修改背侧垂直导线975。在一些实施例中,修改背侧垂直导线975以避免由第一部分978a的增大的第一宽度“wa”引起的设计规则违规。在一些可选实施例中,不修改背侧垂直导线975,而第一部分978a设计为具有增大的第一宽度“wa”。在操作836中,当用于访问电路节点的背侧垂直导线(诸如图9c中的978)重新设计为局部二维导线时,局部二维导线有可能导致设计规则违规,并且可能需要修改相邻的背侧垂直导线(诸如图9c中的975)以减轻设计规则违规。例如,当背侧垂直导线978更改为图9c中的局部二维导线时,图9c中的背侧垂直导线975从图9c中的背侧垂直导线975缩短的。在图8的示例流程图中,由于修改相邻背侧垂直导线的可能性,操作836位于操作832和934之后的工艺流程中。

73.在图8中,在工艺800完成操作838之后,工艺800返回到操作810,并且对各种背侧导线进行自动放置和路由(apr)。然后,工艺800进行到操作820,并且再次检查修改的布局设计是否设计规则违规。重复包括操作838、810和820的迭代,直到布局设计通过设计规则检查,然后,工艺800进行到设计流程的剩余部分895。设计流程的剩余部分895中的示例操作包括时钟树综合、rc提取、时序分析、信号完整性分析、验证等。

74.图10是根据一些实施例的制造集成电路的方法1000的流程图。图10中描述方法1000的操作的顺序仅用于说明;方法1000的操作能够以不同于图10中描述的顺序执行。应当理解,可以在图10中描述的方法1000之前、期间和/或之后执行附加操作,并且在本文中可能仅简要描述一些其他工艺。

75.在方法1000的操作1010中,制造第一类型有源区域结构和第二类型有源区域结构。在一些实施例中,第一类型有源区域结构为p型有源区域结构,并且第二类型有源区域结构为n型有源区域结构。在一些实施例中,第一类型有源区域结构为n型有源区域结构,并且第二类型有源区域结构为p型有源区域结构。在图2a至图2e和图3a至图3c所示的示例实施例中,在衬底50的顶部上制造p型有源区域结构80p和n型有源区域结构80n。在操作1010中制造的有源区域结构的示例包括鳍结构、纳米片结构和纳米线结构。

76.在方法1000的操作1022和操作1024中,制造栅极导体和端子导体。栅极导体和端子导体中的每个与衬底之上的第一类型有源区域结构和/或第二类型有源区域结构相交。在图2a至图2e和图3a至图3c所示的示例实施例中,在操作1022中制造的栅极导体包括与p型有源区域结构80p和n型有源区域结构80n相交的栅极导体152和158。在示例实施例中,在操作1022中制造的端子导体包括与p型有源区域结构80p相交的端子导体132p、135p和138以及与n型有源区域结构80n相交的端子导体132n、135n和138。在操作1022和操作1024之后,工艺流程进行到操作1030。

77.在方法1000的操作1030中,制造前侧第一层导线。在图2a至图2e和图3a至图3c所示的示例实施例中,在前段制程(feol)工艺中制造顶部绝缘层之后,在操作1030中制造位于顶部绝缘层上面的第一连接层(诸如第一金属层m0)中的前侧第一层导线122、124和126。

78.在操作1010、1022、1024和1030之后,在操作1040中翻转包含衬底的晶圆。然后,工艺流程进行到1050。在方法1000的操作1050中,制造穿过衬底的通孔连接件。在操作1050中制造的通孔连接件的一个示例是用于将衬底的前侧处的栅极导体连接至衬底的背侧处的导线的通孔连接件。在操作1050中制造的通孔连接件的另一个示例是用于将衬底的前侧处的端子导体连接至衬底的背侧处的导线的通孔连接件。在图2a至图2e和图3a至图3c所示的示例实施例中,在操作1050中制造穿过衬底50的通孔连接件1bvg1、1bvg2和1bvd1。在操作1050之后,工艺流程进行到操作1060。

79.在方法1000的操作1060中,在衬底的背侧处制造背侧水平导线。在一些实施例中,背侧水平导线中的一条制造为跨越电路单元的垂直边界延伸小于一个cpp的距离的延伸的导线。在图2a至图2e和图3a至图3c所示的示例实施例中,在衬底50的背侧处的背侧第一导电层中(诸如第一背侧金属层bm0中)制造背侧水平导线181、182、184和186。在示例实施例中,背侧水平导线182跨越垂直单元边界119延伸小于一个cpp的距离“δ”。在操作1060之后,工艺流程进行到操作1070。

80.在方法1000的操作1070中,制造通孔连接件。在操作1070中制造的通孔连接件的一个示例是用于连接背侧水平导线和背侧垂直导线的通孔连接件。在图2a至图2e和图3a至图3c所示的示例实施例中,在操作1070中制造穿过背侧层间电介质56的通孔连接件1bv0a、1bv0b和1bv0c。在操作1070之后,工艺流程进行到操作1080。

81.在方法1000的操作1080中,制造背侧垂直导线。在一些实施例中,背侧垂直导线中的一条与电路单元的垂直边界对准并且通过引脚连接件直接连接至背侧水平导线中的一条。在一些实施例中,与电路单元的垂直边界对准的背侧垂直导线是局部二维导线,局部二维导线具有第一宽度的第一部分和不同于第一宽度的第二宽度的第二部分。在图2a至图2e和图3a至图3c所示的示例实施例中,在背侧第一导电层中(诸如在第一背侧金属层bm0中)制造背侧垂直导线172、175和178。在示例实施例中,背侧垂直导线178与垂直单元边界119对准。背侧垂直导线178通过通孔连接件1bv0a(用作引脚连接件)导电连接至背侧水平导线182。在图4a至图4e所示的示例实施例中,背侧垂直导线178包括具有第一宽度“wa”的第一部分178a和具有第二宽度“wb”的第二部分178b。

82.在如图2a至图2e和图3a至图3c所示的示例实施例中,背侧垂直导线(在第二背侧金属层bm1中)与栅极导体的接触多晶间距(cpp)之间的齿轮比为一比一(即1:1)。在一些可选实施例中,背侧垂直导线(在第二背侧金属层bm1中)与栅极导体的cpp之间的齿轮比为二比三(即,2:3)。在又一些可选实施例中,背侧垂直导线(在第二背侧金属层bm1中)与栅极导体的cpp之间的齿轮比为一比二(即,1:2)。齿轮比的其他选择也在本发明的预期范围内。

83.图11是根据一些实施例的电子设计自动化(eda)系统1100的框图。

84.在一些实施例中,eda系统1100包括apr系统。根据一些实施例,例如,可使用eda系统1100实现根据一个或多个实施例的在本文中描述的设计表示线路由布置的布局图的方法。

85.在一些实施例中,eda系统1100是通用计算器件,包括硬件处理器1102和非暂时性

计算机可读存储介质1104。存储介质1104编码有(即存储)计算机程序代码1106(即一组可执行指令)。根据一个或多个实施例,硬件处理器1102对指令1106的执行表示(至少部分地)eda工具,该eda工具实现本文中描述的方法的部分或全部(在下文中,所述工艺和/或方法)。

86.处理器1102经由总线1108电耦接至计算机可读存储介质1104。处理器1102还通过总线1108电耦接至i/o接口1110。网络接口1112也经由总线1108电连接至处理器1102。网络接口1112连接至网络1114,使得处理器1102和计算机可读存储介质1104能够经由网络1114连接至外部元件。处理器1102配置为执行在计算机可读存储介质1104中编码的计算机程序代码1106,以便使系统1100可用于执行所述工艺和/或方法的部分或全部。在一个或多个实施例中,处理器1102是中央处理单元(cpu)、多处理器、分布式处理系统、专用集成电路(asic)和/或合适的处理单元。

87.在一个或多个实施例中,计算机可读存储介质1104是电子、磁、光、电磁、红外和/或半导体系统(或装置或设备)。例如,计算机可读存储介质1104包括半导体或固态存储器、磁带、可移动计算机磁盘、随机存取存储器(ram)、只读存储器(rom)、硬磁盘和/或光盘。在使用光盘的一些实施例中,计算机可读存储介质1104包括压缩盘-只读存储器(cd-rom)、压缩盘-读/写(cd-r/w)和/或数字视频盘(dvd)。

88.在一个或多个实施例中,存储介质1104存储计算机程序代码1106,该计算机程序代码1106配置为使系统1100(其中这种执行表示(至少部分地)eda工具)可用于执行所述工艺和/或方法的部分或全部。在一个或多个实施例中,存储介质1104还存储促进执行所述工艺和/或方法的部分或全部的信息。在一个或多个实施例中,存储介质1104存储包括如本文所公开的这种标准单元的标准单元的库1107。在一个或多个实施例中,存储介质1104存储对应于本文公开的一个或多个布局的一个或多个布局图1109。

89.eda系统1100包括i/o接口1110。i/o接口1110耦接至外部电路。在一个或多个实施例中,i/o接口1110包括用于向处理器1102传送信息和命令的键盘、小键盘、鼠标、轨道球、轨道板、触摸屏和/或光标方向键。

90.eda系统1100还包括耦接至处理器1102的网络接口1112。网络接口1112允许系统1100与网络1114通信,一个或多个其他计算机系统连接至该网络。网络接口1112包括无线网络接口,诸如蓝牙、wifi、wimax、gprs、wcdma等;或有线网络接口,诸如ethernet、usb或ieee-1364。在一个或多个实施例中,所述工艺和/或方法的部分或全部在两个或多个系统1100中实施。

91.系统1100配置为通过i/o接口1110接收信息。通过i/o接口1110接收的信息包括指令、数据、设计规则、标准单元的库和/或用于由处理器1102处理的其他参数中的一个或多个。信息经由总线1108传送到处理器1102。eda系统1100配置为通过i/o接口1110接收与ui相关的信息。该信息作为用户接口(ui)1142存储在计算机可读介质1104中。

92.在一些实施例中,所述工艺和/或方法的部分或全部被实现为由处理器执行的独立软件应用。在一些实施例中,所述工艺和/或方法的部分或全部实现为作为附加软件应用的部分的软件应用。在一些实施例中,所述工艺和/或方法的部分或全部实现为软件应用的插件。在一些实施例中,所述工艺和/或方法中的至少一个实现为作为eda工具的部分的软件应用。在一些实施例中,所述工艺和/或方法的部分或全部实现为由eda系统1100使用的

软件应用。在一些实施例中,使用诸如可从cadence design systems公司获得的的工具或其他合适的布局生成工具生成包括标准单元的布局图。

93.在一些实施例中,工艺实现为存储在非暂时性计算机可读记录介质中的程序的函数。非暂时性计算机可读记录介质的示例包括但不限于外部/可移动和/或内部/内置存储或存储单元,例如,一个或多个光盘(诸如dvd)、磁盘(诸如硬盘)、半导体存储器(诸如rom、ram、存储卡等)。

94.图12是根据一些实施例的集成电路(ic)制造系统1200和与其相关联的ic制造流程的框图。在一些实施例中,基于布局图,使用制造系统1200制造(a)一个或多个半导体掩模或(b)半导体集成电路的层中的至少一个组件中的至少一个。

95.在图12中,ic制造系统1200包括在设计、开发和制造周期和/或与制造ic器件1260有关的服务中彼此交互的实体,诸如设计室1220、掩模室1230和ic厂商/制造商(“fab”)1250。系统1200中的实体通过通信网络连接。在一些实施例中,通信网络是单个网络。在一些实施例中,通信网络是各种不同的网络,诸如内联网和因特网。通信网络包括有线和/或无线通信信道。每个实体与一个或多个其他实体交互,并且向一个或多个其他实体提供服务和/或从一个或多个其他实体接收服务。在一些实施例中,设计室1220、掩模室1230和ic制造商1250中的两个或多个由单个较大的公司拥有。在一些实施例中,设计室1220、掩模室1230和ic制造商1250中的两个或多个共存于共同设施中并且使用共同资源。

96.设计室(或设计团队)1220生成ic设计布局图1222。ic设计布局图1222包括为ic器件1260设计的各种几何图案。几何图案对应于构成待制造的ic器件1260的各种组件的金属、氧化物或半导体层的图案。各个层组合形成各个ic部件。例如,ic设计布局图1222的部分包括各种ic部件,诸如将在半导体衬底(诸如硅晶圆)和设置在半导体衬底上的各个材料层中形成的有源区域、栅电极、源极和漏极、层间互连件的金属线或通孔以及用于形成接合焊盘的开口。设计室1220实施适当的设计工序以形成ic设计布局图1222。设计工序包括逻辑设计、物理设计或放置和路由中的一个或多个。ic设计布局图1222呈现在具有几何图案信息的一个或多个数据文件中。例如,ic设计布局图1222可以用gdsii文件格式或dfii文件格式表示。

97.掩模室1230包括数据准备1232和掩模制造1244。掩模室1230使用ic设计布局图1222来制造一个或多个掩模1245,用于根据ic设计布局图1222制造ic器件1260的各个层。掩模室1230执行掩模数据准备1232,其中ic设计布局图1222转换为代表性数据文件(“rdf”)。掩模数据准备1232将rdf提供给掩模制造1244。掩模制造1244包括掩模写入器。掩模写入器将rdf转换为衬底上的图像,诸如掩模(中间掩模)1245或半导体晶圆1253。ic设计布局图1222由掩模数据准备1232操纵,以符合掩模写入器的特定特性和/或ic制造商1250的要求。在图12中,掩模数据准备1232和掩模制造1244示出为单独的要素。在一些实施例中,掩模数据准备1232和掩模制造1244可以统称为掩模数据准备。

98.在一些实施例中,掩模数据准备1232包括光学邻近校正(opc),opc使用光刻增强技术来补偿图像误差,诸如可能由衍射、干涉、其他工艺效应等引起的图像误差。opc调整ic设计布局图1222。在一些实施例中,掩模数据准备1232包括进一步的分辨率增强技术(ret),诸如轴外照射、子分辨率辅助部件、相移掩模、其他合适的技术等或它们的组合。在一些实施例中,还使用逆光刻技术(ilt),ilt将opc视为逆成像问题。

99.在一些实施例中,掩模数据准备1232包括掩模规则检查器(mrc),mrc使用一组掩模创建规则检查已经经受opc中的工艺的ic设计布局图1222,掩模创建规则包含某些几何和/或连接限制以确保足够的裕度,以解决半导体制造工艺中的可变性等。在一些实施例中,mrc修改ic设计布局图1222以补偿掩模制造1244期间的限制,这可以撤消由opc实施的部分修改以便满足掩模创建规则。

100.在一些实施例中,掩模数据准备1232包括光刻工艺检查(lpc),lpc模拟将由ic制造商1250实施以制造ic器件1260的处理。lpc基于ic设计布局图1222模拟该处理以创建模拟制造的器件,诸如ic器件1260。lpc模拟中的处理参数可以包括与ic制造周期的各种工艺相关的参数、与用于制造ic的工具相关的参数和/或制造工艺的其他方面。lpc考虑各种因素,诸如空间图像对比度、焦深(“dof”)、掩模误差增强因子(“meef”)、其他合适的因子等或它们的组合。在一些实施例中,在通过lpc创建模拟制造的器件之后,如果模拟的器件在形状上不够接近以满足设计规则,则重复opc和/或mrc以进一步细化ic设计布局图1222。

101.应当理解,为了清楚起见,已经简化了掩模数据准备1232的上述描述。在一些实施例中,数据准备1232包括诸如逻辑操作(lop)的附加特征,以根据制造规则修改ic设计布局图1222。另外,在数据准备1232期间施加于ic设计布局图1222的工艺可以以各种不同的顺序执行。

102.在掩模数据准备1232之后并且在掩模制造1244期间,基于修改的ic设计布局图1222制造掩模1245或掩模1245的组。在一些实施例中,掩模制造1244包括基于ic设计布局图1222执行一个或多个光刻曝光。在一些实施例中,基于修改的ic设计布局图1222,使用电子束(e束)或多个电子束的机制在掩模(光掩模或中间掩模)1245上形成图案。掩模1245可以用各种技术形成。在一些实施例中,使用二元技术形成掩模1245。在一些实施例中,掩模图案包括不透明区域和透明区域。用于曝光已经涂布在晶圆上的图像敏感材料层(例如,光刻胶)的辐射束(诸如紫外(uv)光束)由不透明区域阻挡并且传输通过透明区域。在一个示例中,掩模1245的二元掩模版本包括透明衬底(例如,熔融石英)和涂布在二元掩模的不透明区域中的不透明材料(例如,铬)。在另一示例中,使用相移技术形成掩模1245。在掩模1245的相移掩模(psm)版本中,在相移掩模上形成的图案中的各种部件配置为具有适当的相位差以提高分辨率和成像质量。在各个示例中,相移掩模可以是衰减psm或交替psm。由掩模制造1244生成的掩模用于各种工艺中。例如,这种掩模用于离子注入工艺中以在半导体晶圆1253中形成各个掺杂区域,用于蚀刻工艺中以在半导体晶圆1253中形成各个蚀刻区域和/或用于其他合适的工艺中。

103.ic制造商1250是ic制造业务,包括用于制造各种不同ic产品的一个或多个制造设施。在一些实施例中,ic制造商1250是半导体代工厂。例如,可能存在用于多个ic产品(前段制程(feol)制造)的前端制造的制造设施,而第二制造设施可以为ic产品(后段制程(beol)制造)的互连和封装提供后端制造,并且第三制造设施可以为代工业务提供其他服务。

104.ic制造厂1250包括制造工具1252,制造工具1252配置为对半导体晶圆1253执行各种制造操作,使得根据掩模(例如,掩模1245)制造ic器件1260。在各个实施例中,制造工具1252包括晶圆步进机、离子注入机、光刻胶涂布机、处理室(例如cvd室或lpcvd炉)、cmp系统、等离子体蚀刻系统、晶圆清洁系统或能够执行如本文讨论的一个或多个或合适的制造工艺的其他制造设备。

105.ic制造商1250使用由掩模室1230制造的掩模(或多个掩模)1245来制造ic器件1260。因此,ic制造商1250至少间接地使用ic设计布局图1222来制造ic器件1260。在一些实施例中,半导体晶圆1253由ic制造商1250使用掩模(或多个掩模)1245制造以形成ic器件1260。在一些实施例中,ic制造包括至少间接地基于ic设计布局图1222执行一个或多个光刻曝光。半导体晶圆1253包括硅衬底或其上形成有材料层的其他适当衬底。半导体晶圆1253还包括各个掺杂区域、介电部件、多级互连件等中的一个或多个(在随后的制造步骤中形成)。

106.关于集成电路(ic)制造系统(例如,图12的系统1200)以及与其相关联的ic制造流程的细节可以在例如2016年2月9日授权的美国专利第9,256,709号、2015年10月1日公布的美国授权前公开号20150278429、2014年2月6日公布的美国授权前公开号20140040838、2007年8月21日授权的美国专利第7,260,442号中找到,它们的全部内容结合于此作为参考。

107.例如,在第9,256,709号美国专利中,在设计室(或设计团队)生成ic设计布局。ic设计布局包括为ic器件设计的各种几何图案。几何图案对应于构成要制造的ic器件的各种组件的金属,氧化物或半导体层的图案。各个层组合形成各种ic功能。例如,ic设计布局的部分包括各种ic部件,例如有源区域、栅电极、源极和漏极、层间互连的金属线或通孔,以及用于在半导体中形成的用于焊盘的开口,开口将形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层。设计室执行适当的设计过程以形成ic设计布局。设计过程可以包括逻辑设计、物理设计和/或布局布线。ic设计布局被呈现在具有几何图案信息的一个或多个数据文件中。掩模室使用ic设计布局来制造一个或多个掩模,掩模用于根据ic设计布局来制造ic器件的各个层。掩模室执行掩模数据准备,其中将ic设计布局转换成可以由掩模编写器物理写入的形式,其中将由掩模数据准备准备的设计布局修改为遵守特定的掩模制造商和/或掩模厂商,然后进行制造。在本实施例中,掩模数据准备和掩模制造被图示为单独的元件,然而,掩模数据准备和掩模制造可以被统称为掩模数据准备。掩模数据准备通常包括光学接近度校正(opc),其使用光刻增强技术来补偿图像误差,诸如可能由于衍射、干涉或其他处理效应而引起的那些图像误差。掩模数据准备可以包括其他分辨率增强技术(ret),例如离轴照明、子分辨率辅助特征、相移掩模、其他合适的技术或其组合。掩模数据准备132还包括掩模规则检查器(mrc),掩模规则检查器使用一组掩模创建规则来检查已经在opc中进行过处理的ic设计布局,该掩模创建规则可以包含一些几何和连通性限制以确保足够的裕度。

108.例如,在第20150278429号美国预授权公开文本中,在一个实施例中,ic制造系统可以采用无掩模光刻技术,诸如电子束光刻或光学无掩模光刻。在这样的系统中,掩模制造被旁路,并且ic设计布局通过适合于利用特定的无掩模光刻技术进行晶圆处理的数据准备来修改。数据准备修改了适合于ic制造系统中的后续操作的设计布局。数据准备的结果以一个或多个数据文件表示,例如gdsii文件格式或dfii文件格式的文件。一个或多个数据文件包括几何图案的信息,例如表示主要设计图案和/或辅助部件的多边形。在本实施例中,一个或多个数据文件还包括由数据准备产生的辅助数据。辅助数据将用于增强ic制造系统的各种操作,例如由掩模室进行的掩模制造和由ic制造商进行的晶圆曝光。

109.例如,在第20140040838号美国预授权公开文本中,ic设计布局被呈现在具有几何

图案信息的一个或多个数据文件中。在一示例中,ic设计布局以本领域已知的“gds”格式表示。在替代实施例中,ic设计布局可以以诸如dfii、cif、oasis或任何其他合适的文件类型的替代文件格式在ic制造系统中的组件之间传输。ic设计布局300包括代表集成电路的部件的各种几何图案。例如,ic设计布局可以包括主要的ic部件,例如有源区、栅电极、源极和漏极、金属线、层间互连通孔,以及用于在半导体中形成的用于焊盘的开口,开口将形成在半导体衬底(例如硅晶圆)和设置在半导体衬底上的各种材料层。ic设计布局还可包括一些辅助部件,诸如用于成像效果、处理增强和/或掩模识别信息的那些部件。

110.例如,在第7,260,442号美国专利中,掩模制造系统包括:用于加工掩模的加工工具;与处理工具连接的计量工具,用于检查掩模并获得检查结果;控制器,与处理工具和计量工具耦接,用于生成处理工具的制造模型,并根据设备数据、材料数据和掩模的检查结果对制造模型进行校准。掩模制造系统可包括至少一个处理工具、计量工具、控制器、数据库和制造执行系统。处理工具可以是曝光工具、显影剂、蚀刻机或光刻胶剥离剂。计量工具执行蚀刻后检查或剥离后检查,并分别获得蚀刻后检查结果或剥离后检查结果。控制器用于处理工具的运行到运行控制,包括前馈控制和后馈控制。控制器从计量工具接收蚀刻后或剥离后检查结果,并从数据库中检索器件和材料数据。与制造执行系统连接的控制器生成处理工具的制造模型,并根据设备数据、材料数据和掩模的检查结果来校准制造模型。

111.本发明的一个方面涉及一种集成电路。集成电路包括:第一类型有源区域结构与第二类型有源区域结构,位于衬底上在第一方向上延伸;前侧第一层导线,位于衬底之上的第一连接层中;以及多个栅极导体,位于第一连接层下方在第二方向上延伸。两个相邻的栅极导体分隔开间距距离,该间距距离等于接触多晶间距(“cpp”)。该集成电路还包括具有在垂直于第一方向的第二方向上延伸的第一垂直边界和第二垂直边界的电路单元。第一垂直边界与第二垂直边界中的每个跨越至少一个边界隔离区域,并且第一垂直边界与第二垂直边界之间的沿着第一方向的距离小于或等于三个cpp。该集成电路还包括位于衬底下方的背侧第一导电层中的在第一方向上延伸的背侧水平导线、位于背侧第一导电层下方的背侧第二导电层中的在第二方向上延伸的背侧垂直导线,以及直接连接在背侧水平导线和背侧垂直导线之间的用于电路单元的引脚连接件。背侧水平导线跨越电路单元的第一垂直边界延伸。背侧垂直导线与第一垂直边界对准。

112.在上述集成电路中,其中,背侧水平导线跨越电路单元的第一垂直边界延伸的距离小于一个接触多晶间距但大于接触多晶间距的八分之一。

113.在上述集成电路中,其中,背侧水平导线跨越电路单元的第一垂直边界延伸的距离小于一个接触多晶间距但大于接触多晶间距的四分之一。

114.在上述集成电路中,其中,背侧水平导线跨越电路单元的第一垂直边界延伸的距离小于一个接触多晶间距但大于接触多晶间距的一半。

115.在上述集成电路中,其中,背侧垂直导线的沿着第一方向的宽度大于接触多晶间距的四分之三。

116.在上述集成电路中,其中,背侧垂直导线的沿着第一方向的宽度大于接触多晶间距的一半。

117.在上述集成电路中,其中,沿着第一方向的第一垂直边界与第二垂直边界之间的距离小于或等于两个接触多晶间距。

118.本发明的另一方面涉及一种集成电路。集成电路包括位于衬底上在第一方向上延伸的第一类型有源区域结构与第二类型有源区域结构、位于衬底之上的第一连接层中的前侧第一层导线以及位于第一连接层下方的在第二方向上延伸的多个栅极导体。两个相邻的栅极导体分隔开间距距离,该间距距离等于接触多晶间距(“cpp”)。该集成电路还包括具有在垂直于第一方向的第二方向上延伸的第一垂直边界和第二垂直边界的电路单元。第一垂直边界与第二垂直边界中的每个跨越至少一个边界隔离区域。该集成电路还包括位于衬底下方的背侧第一导电层中的在第一方向上延伸的背侧水平导线、位于背侧第一导电层下方的背侧第二导电层中的在第二方向上延伸的背侧垂直导线以及在背侧水平导线和背侧垂直导线之间的重叠区域处直接连接在背侧水平导线和背侧垂直导线之间的用于电路单元的引脚连接件。背侧垂直导线具有覆盖重叠区域的第一部分和位于重叠区域外部的第二部分。沿着第一方向的第一部分的第一宽度大于沿着第一方向的第二部分的第二宽度。

119.在上述集成电路中,其中,第一宽度比第二宽度大超过接触多晶间距的八分之一的量。

120.在上述集成电路中,其中,第一宽度比第二宽度大超过接触多晶间距的四分之一的量。

121.在上述集成电路中,其中,第一垂直边界和第二垂直边界沿着第一方向分隔开的距离小于或等于三个接触多晶间距。

122.在上述集成电路中,其中,第一垂直边界和第二垂直边界沿着第一方向分隔开的距离小于或等于两个接触多晶间距。

123.在上述集成电路中,其中,背侧水平导线跨越电路单元的第一垂直边界延伸的距离小于一个接触多晶间距但大于接触多晶间距的八分之一。

124.在上述集成电路中,其中,背侧水平导线跨越电路单元的第一垂直边界延伸的距离小于一个接触多晶间距但大于接触多晶间距的四分之一。

125.本发明的另一方面涉及一种方法。该方法包括在衬底上制造在第一方向上延伸的第一类型有源区域结构和第二类型有源区域结构,以及制造在垂直于第一方向的第二方向上延伸的多个栅极导体。每个栅极导体与衬底之上的第一类型有源区域结构和/或第二类型有源区域结构相交。两个相邻的栅极导体分隔开间距距离,该间距距离等于接触多晶间距(cpp)。该方法还包括在衬底下方的背侧第一导电层中制造在第一方向上延伸的背侧水平导线,制造连接至背侧水平导线的引脚连接件,以及在背侧第一导电层下方的背侧第二导电层中制造在第二方向上延伸的背侧垂直导线,背侧垂直导线与电路单元的第一垂直边界对准。引脚连接件在背侧水平导线与背侧垂直导线之间的的重叠区域处直接连接在背侧水平导线与背侧垂直导线之间。在该方法中,制造背侧水平导线包括将背侧水平导线制造为跨越电路单元的第一垂直边界延伸的延伸导线,延伸的距离小于一个cpp。

126.在上述方法中,方法还包括:制造背侧垂直导线以形成覆盖重叠区域的第一部分和位于重叠区域外部的第二部分,并且其中,沿着第一方向的第一部分的第一宽度大于沿着第一方向的第二部分的第二宽度。

127.在上述方法中,方法还包括:在衬底之上和多个栅极导体之上的第一连接层中制造前侧第一层导线。

128.在上述方法中,其中,制造背侧水平导线包括:

129.将背侧水平导线制造为跨越电路单元的第一垂直边界延伸的延伸导线,延伸的距离小于一个接触多晶间距但大于接触多晶间距的八分之一。

130.在上述方法中,其中,制造背侧水平导线包括:将背侧水平导线制造为跨越电路单元的第一垂直边界延伸的延伸导线,延伸的距离小于一个接触多晶间距但大于接触多晶间距的四分之一。

131.在上述方法中,其中,制造背侧垂直导线包括:将背侧垂直导线制造为具有均匀的宽度的导线,宽度大于接触多晶间距的一半。

132.本领域的普通技术人员将容易看出,所公开的实施例中的一个或多个实现了上述优点中的一个或多个。在阅读了前述说明书之后,普通技术人员将能够影响如本文广泛公开的各种变化、等同的替换和各种其他实施例。因此,此处授予的保护旨在仅受所附权利要求及其等同中包含的定义的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。