1.本发明涉及一种脉冲神经元加固电路、加固方法,涉及脉冲神经网络技术领域。

背景技术:

2.脉冲神经网络作为第三代神经网络,以其仿生神经动力学特性及事件驱动的优势,在类脑神经形态计算领域广泛应用。脉冲神经元(spiking neuron)是脉冲神经网络的基本计算单元,其模拟生物神经元的工作模式,通过对输入的脉冲信号进行整合计算并向后面的神经元输出新的脉冲信号,从而完成神经元之间的信息传递。脉冲神经元通过神经元模型参数计算来输出兴奋或抑制的神经元放电的脉冲信号。常用的脉冲神经元模型包括1907年lapicque提出的lif模型、2003年e.m.izhikevich提出的izhikevich模型、1952年hodgkin和huxley提出的hodgkin-huxley模型,其中izhikevich模型能够仿真生物神经元最突出的20种兴奋或抑制的神经元放电的脉冲信号。

3.脉冲神经元在空间应用时极易受到单粒子效应的影响,若神经元模型参数因为单粒子翻转或单粒子瞬态引发了单位错或多位错,则会造成神经元放电行为异常,输出错误的脉冲信号,严重的话,将导致类脑神经形态计算芯片的输出结果错误。

技术实现要素:

4.本发明要解决的技术问题是:克服现有技术的不足,提供了一种脉冲神经元加固电路、加固方法,解决现有技术中脉冲神经元受到单粒子效应影响易发生计算错误的缺陷,有效的提高脉冲神经元的空间环境适应性。该方法通过配置信息和模型参数能够实现脉冲神经网络所需要的脉冲神经元及神经元放电脉冲信号;进一步地,该方法通过ecc编解码模块对配置信息和模型参数进行纠检错容错;进一步地,该方法通过影子存储器(或寄存器组)对配置信息和模型参数进行备份容错。

5.本发明目的通过以下技术方案予以实现:

6.一种脉冲神经元加固电路,包括第一寄存器组、第二寄存器组、第三寄存器组、编码模块、解码模块、逻辑模块、可配置脉冲神经元计算单元;

7.编码模块用于对外部或逻辑模块输入的第一数据和或第二数据进行编码;

8.第一寄存器组用于存储编码后的第一数据;

9.第二寄存器组用于存储编码后的第二数据;

10.第三寄存器组用于直接存储第一数据和或第二数据;

11.解码模块用于对编码后的第一数据和或第二数据进行纠检错解码,并记录解码结果;编码模块的编码方式与解码模块的解码方式相对应;

12.逻辑模块根据解码结果,选择解码后的第一数据和或第二数据输出给可配置脉冲神经元计算单元,或选择第三寄存器组中的第一数据和或第二数据输出给可配置脉冲神经元计算单元和编码模块;

13.可配置脉冲神经元计算单元利用输入的第一数据和或第二数据进行配置。

14.本发明一实施例中,第一数据为配置信息,第二数据为模型参数。

15.本发明一实施例中,可配置脉冲神经元计算单元利用配置信息生成lif神经元或izhikevich神经元或hodgkin-huxley神经元。

16.本发明一实施例中,可配置脉冲神经元计算单元利用模型参数生成对应的兴奋或抑制的神经元放电的脉冲信号。

17.本发明一实施例中,第三寄存器组与第一寄存器组和第二寄存器组空间隔离,或第三寄存器组进行独立加固,用于减小空间单粒子效应的影响。

18.本发明一实施例中,第三寄存器采用十字交叉布局方式与第一寄存器组和第二寄存器组空间隔离,且根据可配置脉冲神经元计算单元工作的空间环境,确定第三寄存器组与第一寄存器组和第二寄存器组的空间距离;其中空间环境包括太空轨道高度、空间辐照环境、三个寄存器组的空间布局方式。

19.本发明一实施例中,编码模块采用ecc编码方式。

20.本发明一实施例中,解码模块进行纠检错解码时,对输入的数据进行一位错纠正、多位错检测。

21.本发明一实施例中,当解码结果为多位错时;逻辑模块选择第三寄存器组中的第一数据和第二数据,输出给可配置脉冲神经元计算单元和编码模块。

22.本发明一实施例中,编码模块包括第一编码模块和第二编码模块,第一编码模块用于对外部或逻辑模块输入的第一数据进行编码;第二编码模块用于对外部或逻辑模块输入的第二数据进行编码。

23.本发明一实施例中,解码模块包括第一解码模块和第二解码模块,第一解码模块用于对外部或逻辑模块输入的第一数据进行纠检错解码;第二解码模块用于对外部或逻辑模块输入的第二数据进行纠检错解码。

24.本发明一实施例中,编码模块的编码方式与解码模块的解码方式根据不同的神经元模型,采用不同的编解码位数,对输入的数据进行多位错纠正以及多位错检测。

25.一种脉冲神经元加固方法,包括如下步骤:

26.对外部输入的第一数据和或第二数据进行原始存储,并对该输入的第一数据和或第二数据进行编码;

27.编码后的第一数据、第二数据进行分别存储;

28.对编码后的第一数据和或第二数据进行纠检错解码;

29.当解码时出现的错误数据较少时,对错误数据进行纠正后,用于配置脉冲神经元;当解码时出现的错误数据较多时,利用原始存储的数据配置脉冲神经元,并利用原始存储的数据对编码前的相应错误数据进行替换。

30.本发明一实施例中,第一数据为配置信息,可配置脉冲神经元生成lif神经元或izhikevich神经元或hodgkin-huxley神经元。

31.本发明一实施例中,第二数据为模型参数,可配置脉冲神经元生成对应的兴奋或抑制的神经元放电的脉冲信号。

32.本发明一实施例中,原始存储与编码后存储空间隔离,或原始存储进行独立加固,用于减小空间单粒子效应的影响。

33.本发明一实施例中,第原始存储采用十字交叉布局方式与编码后存储空间隔离,

且根据脉冲神经元工作的空间环境,确定空间隔离距离;其中空间环境包括太空轨道高度、空间辐照环境、空间隔离的布局方式。

34.本发明一实施例中,采用ecc编码方式以及ecc解码方式。

35.本发明一实施例中,纠检错解码时,对输入的数据进行一位错纠正、多位错检测。

36.本发明一实施例中,解码时出现多位错时,利用原始存储的数据配置脉冲神经元。

37.本发明一实施例中,编码方式与解码方式相匹配,且根据不同的神经元模型,采用不同的编解码位数,对输入的数据进行多位错纠正以及多位错检测。

38.本发明一实施例中,采用两路编码电路,其中一路对第一数据进行编码,另一路对第二数据进行编码。

39.本发明一实施例中,采用两路解码电路,其中一路对第一数据进行纠检错解码,另一路对第二数据进行纠检错解码。

40.本发明相比于现有技术具有如下有益效果:

41.(1)本发明通过配置信息和模型参数信息可生成多种神经元及其放电脉冲信号,提高了脉冲神经网络的适应性,同时,在一种神经元被空间粒子损坏的情况下,可通过配置信息配置成另外一种神经元,提升了神经元的可靠性。

42.(2)本发明在神经元配置信息出现一位错或多位错时,通过ecc纠检错机制自动纠错,提升了神经元的可靠性。

43.(3)本发明在神经元配置信息出现多位错时,通过仲裁校正控制逻辑模块控制影子存储器(或寄存器组)输出正确配置信息数据,同时纠正错误的配置信息,提升了神经元的可靠性。

44.(4)本发明在神经元模型参数出现一位错或多位错时,通过ecc纠检错机制自动纠错,提升了神经元的可靠性。

45.(5)本发明在神经元模型参数出现多位错时,通过仲裁校正控制逻辑模块控制影子存储器(或寄存器组)输出正确模型参数数据,同时纠正错误的模型参数,提升了神经元的可靠性。

附图说明

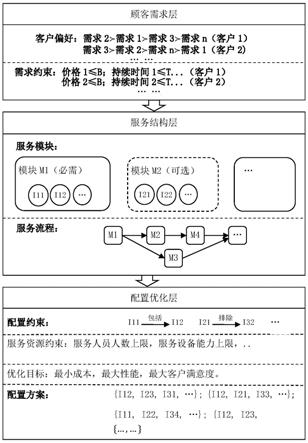

46.图1为本发明实施例中高可靠神经元的结构图;

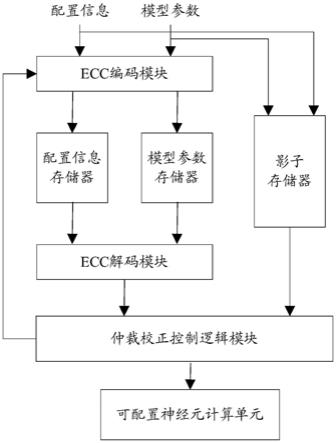

47.图2为本发明实施例中仲裁校正控制逻辑模块的逻辑示意图。

具体实施方式

48.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明的实施方式作进一步详细描述。

49.实施例1:

50.一种脉冲神经元加固电路、加固方法,包括配置信息存储器(或寄存器组)、模型参数存储器(或寄存器组)、ecc编码模块、ecc解码模块、可配置神经元计算单元、影子存储器(或寄存器组)、仲裁校正控制逻辑模块;

51.所述配置信息存储器(或寄存器组)存储多种神经元模型的配置信息,可配置神经元计算单元可依据配置信息生成所需的脉冲神经元,比如lif神经元或izhikevich神经元

或hodgkin-huxley神经元;

52.所述模型参数存储器(或寄存器组)存储多种神经元模型对应的参数信息,可配置神经元计算单元可依据模型参数信息实现对应的兴奋或抑制的神经元放电的脉冲信号,比如存储的20组izhikevich模型参数,分别对应强直脉冲发放、第1类兴奋等20种神经元放电行为;

53.所述ecc编码模块由纠检错编码的逻辑电路组成,可对输入的数据进行一位错纠正多位错检测的编码;

54.所述ecc解码模块由纠检错解码的逻辑电路组成,可对输入的数据进行解码实现一位错的纠正以及多位错的检测,若无错误或发生了一位错,则输出正确结果给仲裁校正控制逻辑模块,若发生了多位错,则输出错误标识给仲裁校正控制逻辑模块;

55.所述可配置神经元计算单元由可配置的数字逻辑电路(比如加法器、乘法器等)或可配置的亿阻器等新型器件组成,通过配置信息可配置生成对应的脉冲神经元;

56.所述影子存储器(或寄存器组)存储脉冲神经元的配置信息和模型参数的备份;

57.所述仲裁校正控制逻辑模块根据ecc解码模块输出的错误标识,控制影子存储器(或寄存器组)输出备份的正确数据给可配置神经元计算单元,同时对配置信息存储器和模型参数存储器中出现的错误进行纠正。

58.优选的,上述高可靠脉冲神经元,输入的配置信息数据通过ecc编码模块进行纠检错编码后,输出给配置信息存储器(或寄存器组),当配置信息存储器(或寄存器组)输出给ecc解码模块的配置信息数据出现一位错误时,所述ecc解码模块通过纠检错解码逻辑纠正错误数据后,输出正确的配置信息数据给可配置神经元计算单元。

59.优选的,上述高可靠脉冲神经元,输入的配置信息通过ecc编码模块进行纠检错编码后,输出给配置信息存储器(或寄存器组),当配置信息存储器(或寄存器组)输出的配置信息数据出现多位错误时,所述ecc解码模块通过纠检错解码输出配置信息错误标识给仲裁校正控制逻辑模块。

60.优选的,上述高可靠脉冲神经元,仲裁校正控制逻辑模块接收到配置信息错误标识后,控制影子存储器(或寄存器组)输出备份的正确配置信息数据给可配置神经元计算单元,同时将正确配置信息数据输出给ecc编码模块,ecc编码模块对配置信息数据重新纠检错编码后,再将正确编码数据输出给配置信息存储器,从而完成配置信息存储器的错误信息纠正。

61.优选的,上述高可靠脉冲神经元,输入的模型参数数据通过ecc编码模块进行纠检错编码后,输出给模型参数存储器(或寄存器组),当模型参数存储器(或寄存器组)输出给ecc解码模块的模型参数数据出现一位错误时,所述ecc解码模块通过纠检错解码逻辑纠正错误数据后,输出正确的模型参数数据给可配置神经元计算单元。

62.优选的,上述高可靠脉冲神经元,输入的模型参数数据通过ecc编码模块进行纠检错编码后,输出给模型参数存储器(或寄存器组),当模型参数存储器(或寄存器组)输出的模型参数数据出现多位错误时,所述ecc解码模块通过纠检错解码输出模型参数错误标识给仲裁校正控制逻辑模块。

63.优选的,上述高可靠脉冲神经元,仲裁校正控制逻辑模块接收到模型参数错误标识后,控制影子存储器(或寄存器组)输出备份的正确模型参数数据给可配置神经元计算单

元,同时将正确模型参数数据输出给ecc编码模块,ecc编码模块对模型参数重新纠检错编码后,再将正确编码数据输出给模型参数存储器,从而完成模型参数存储器的错误信息纠正。

64.优选的,影子存储器与配置信息存储器和模型参数存储器在物理实现中,采用十字交叉布局,即进行空间隔离,间隔不小于预设值,预设值的取值范围为2-10um,以实现脉冲神经元在leo、meo和geo等全轨道范围下高可靠工作之目标。更具体的:

65.通过重粒子蒙特卡洛模型仿真,并与nasa数据、辐照试验数据对比分析,确定以下布局条件:

66.1)当单粒子翻转阈值超过37mev

·

cm2/mg或在meo轨道工作时,存储器间隔不小于第一预设值,第一预设值的取值范围为8-10um。

67.2)当单粒子翻转阈值超过15mev

·

cm2/mg或在geo轨道工作时,存储器间隔不小于第二预设值,第二预设值的取值范围为5-7um。

68.3)当单粒子翻转错误率不大于1e-10/device

·

day或在leo轨道工作时,存储器间隔不小于第三预设值,第三预设值的取值范围为2-4um。

69.实施例2:

70.一种脉冲神经元加固电路、加固方法,具体可以包括配置信息存储器、模型参数存储器、ecc编码模块、ecc解码模块、可配置神经元计算单元、影子存储器、仲裁校正控制逻辑模块。

71.ecc编码模块的输出连接配置信息存储器和模型参数存储器。

72.配置信息存储器和模型参数存储器的输出连接ecc解码模块。

73.ecc解码模块和影子存储器的输出连接仲裁校正控制逻辑模块。

74.仲裁校正控制逻辑模块的输出连接可配置神经元计算单元和ecc编码模块。

75.在本发明实施例中,出于低功耗省资源的考虑,仅使用一个ecc编码模块和ecc解码模块,通过选通开关分时复用模块,来完成配置信息和模型参数的纠检错编码和解码;也可使用两个ecc编码模块和两个ecc解码模块,分别对应配置信息存储器和模型参数存储器,分别完成配置信息的纠检错编解码和模型参数的纠检错编解码。

76.在本发明实施例中,配置信息存储器存储多种神经元模型的配置信息,可配置神经元计算单元可依据配置信息生成所需的脉冲神经元以及神经元工作状态,脉冲神经元可以是lif神经元或izhikevich神经元或hodgkin-huxley神经元,神经元工作状态可以是泄漏模式、阈值放电模式或复位模式等。

77.在本发明实施例中,模型参数存储器存储多种神经元模型对应的参数信息,可配置神经元计算单元可依据模型参数信息实现对应的兴奋或抑制的神经元放电的脉冲信号,比如存储的20组izhikevich模型参数,分别对应强直脉冲发放、第1类兴奋等20种神经元放电行为;存储的6组hodgkin-huxley模型参数,分别对应rs神经元放电、ib神经元放电、fs神经元放电等6种兴奋性或抑制性神经元放电行为;存储的3组lif模型参数,分别对应积分器放电等3种神经元放电行为。

78.在本发明实施例的实施方式一中,ecc编码模块由纠检错编码的逻辑电路组成,可对输入的数据进行一位错纠正多位错检测的编码,具体可以采用汉明码进行纠检错编码。ecc解码模块由纠检错解码的逻辑电路组成,可对输入的数据进行解码实现一位错的纠正

以及多位错的检测,具体可以采用汉明码进行纠检错解码,若无错误或发生了一位错,则输出正确结果(即错误标识为0)给仲裁校正控制逻辑模块,若发生了多位错,则输出错误标识(即错误标识为1)给仲裁校正控制逻辑模块。

79.在本发明实施例的实施方式二中,ecc编解码模块根据输入神经元模型的复杂程度,采取相应的加固编解码策略:

80.a、对于简单的神经元模型,比如支持3种神经元放电行为的lif神经元模型,配置参数和模型参数总计不大于39位时,采用纠4检4编码,需24位校验位,则编码码长开销63位(数据位39,校验位24);

81.b、对于中等复杂的神经元模型,比如支持6种神经元放电行为的hodgkin-huxley神经元模型,配置参数和模型参数总计不大于64位时,分为4组,每组16位数据采用纠1检2编码,每组需校验位6位,则可实现纠4检8编码,对应编码码长开销88位(数据位64,校验位24);

82.c、对于复杂的神经元模型,比如支持20种神经元放电行为的izhikevich神经元模型,配置参数和模型参数总计大于64位时,以32位数据为一组进行划分,每组采用纠1检2编码,每组需校验位7位,则可实现纠正多位错的效果,例如128位神经元数据分为4组,每组32位数据,采用纠1检2编码,每组需校验位7位,则可实现纠4检8编码,对应编码码长开销156位(数据位128,校验位28)。

83.采用上述实施方式二中的加固编解码策略时;若无错误,或发生了位错的数量不超过4个且已完成纠正,则输出正确结果(即错误标识为0)给仲裁校正控制逻辑模块,否则,则输出错误标识(即错误标识为1)给仲裁校正控制逻辑模块。

84.在本发明实施例中,可配置神经元计算单元通过配置信息可配置生成对应的脉冲神经元,具体实现可以包括:由可配置的加法器、乘法器等数字逻辑电路或由可配置的亿阻器等新型器件实现lif神经元或izhikevich神经元或hodgkin-huxley神经元。

85.在本发明实施例中,影子存储器存储脉冲神经元的配置信息和模型参数的备份;仲裁校正控制逻辑模块根据ecc解码模块输出的错误标识,控制影子存储器输出备份的正确数据给可配置神经元计算单元,同时对配置信息存储器和模型参数存储器中出现的错误进行纠正。

86.仲裁校正控制逻辑模块的工作过程如图2所示:如果ecc解码模块输出的配置信息错误标识为0,则说明配置信息正确,选择ecc解码模块输出的配置信息数据给可配置神经元计算单元;如果ecc解码模块输出的配置信息错误标识为1,则说明配置信息错误,从影子存储器取出正确的配置信息数据给可配置神经元计算单元,并将正确的配置信息数据发送给ecc编码模块,对错误的配置信息数据进行校正替换;如果ecc解码模块输出的模型参数错误标识为0,则说明模型参数正确,选择ecc解码模块输出的模型参数数据给可配置神经元计算单元;如果ecc解码模块输出的模型参数错误标识为1,则说明模型参数错误,从影子存储器取出正确的模型参数数据给可配置神经元计算单元,并将正确的模型参数数据发送给ecc编码模块,对错误的模型参数数据进行校正替换。

87.在本发明实施例中,影子存储器与配置信息存储器和模型参数存储器在物理实现中,采用十字交叉布局,即进行空间隔离,间隔不小于预设值,预设值的取值范围为2-10um,以实现脉冲神经元在leo、meo和geo等全轨道范围下高可靠工作之目标。优选的,采用十字

交叉布局包括三种,第一种为影子存储器、配置信息存储器、模型参数存储器三者两两垂直;第二种为配置信息存储器与模型参数存储器平行,影子存储器与配置信息存储器和模型参数存储器均垂直;第三种为配置信息存储器与模型参数存储器平行,影子存储器与配置信息存储器和模型参数存储器的夹角大于60

°

。其中,在每一种布局中,为便于描述三者之间的关系,可将每个存储器均等效为一个片状结构。

88.在第二种空间布局或第三种空间布局的情况下,更具体的:

89.通过重粒子蒙特卡洛模型仿真,并与nasa数据、辐照试验数据对比分析,确定以下布局条件:

90.1)当单粒子翻转阈值超过37mev

·

cm2/mg或在meo轨道工作时,存储器间隔不小于第一预设值,第一预设值的取值范围为8-10um。

91.2)当单粒子翻转阈值超过15mev

·

cm2/mg或在geo轨道工作时,存储器间隔不小于第二预设值,第二预设值的取值范围为5-7um。

92.3)当单粒子翻转错误率不大于1e-10/device

·

day或在leo轨道工作时,存储器间隔不小于第三预设值,第三预设值的取值范围为2-4um。

93.实施例3:

94.一种脉冲神经元加固电路,包括第一寄存器组、第二寄存器组、第三寄存器组、编码模块、解码模块、逻辑模块、可配置脉冲神经元计算单元;

95.编码模块用于对外部或逻辑模块输入的第一数据和或第二数据进行编码;

96.第一寄存器组用于存储编码后的第一数据;

97.第二寄存器组用于存储编码后的第二数据;

98.第三寄存器组用于直接存储第一数据和或第二数据;

99.解码模块用于对编码后的第一数据和或第二数据进行纠检错解码,并记录解码结果;编码模块的编码方式与解码模块的解码方式相对应;

100.逻辑模块根据解码结果,选择解码后的第一数据和或第二数据输出给可配置脉冲神经元计算单元,或选择第三寄存器组中的第一数据和或第二数据输出给可配置脉冲神经元计算单元和编码模块;

101.可配置脉冲神经元计算单元利用输入的第一数据和或第二数据进行配置。

102.本发明一实施方式中,第一数据为配置信息,第二数据为模型参数。

103.本发明一实施方式中,可配置脉冲神经元计算单元利用配置信息生成lif神经元或izhikevich神经元或hodgkin-huxley神经元。

104.本发明一实施方式中,可配置脉冲神经元计算单元利用模型参数生成对应的兴奋或抑制的神经元放电的脉冲信号。

105.本发明一实施方式中,第三寄存器组与第一寄存器组和第二寄存器组空间隔离,或第三寄存器组进行独立加固,用于减小空间单粒子效应的影响。

106.本发明一实施方式中,第三寄存器采用十字交叉布局方式与第一寄存器组和第二寄存器组空间隔离,且根据可配置脉冲神经元计算单元工作的空间环境,确定第三寄存器组与第一寄存器组和第二寄存器组的空间距离;其中空间环境包括太空轨道高度、空间辐照环境、三个寄存器组的空间布局方式。

107.本发明一实施方式中,编码模块采用ecc编码方式。

108.本发明一实施方式中,解码模块进行纠检错解码时,对输入的数据进行一位错纠正、多位错检测。

109.本发明一实施方式中,当解码结果为多位错时;逻辑模块选择第三寄存器组中的第一数据和第二数据,输出给可配置脉冲神经元计算单元和编码模块。

110.本发明一实施方式中,编码模块包括第一编码模块和第二编码模块,第一编码模块用于对外部或逻辑模块输入的第一数据进行编码;第二编码模块用于对外部或逻辑模块输入的第二数据进行编码。

111.本发明一实施方式中,解码模块包括第一解码模块和第二解码模块,第一解码模块用于对外部或逻辑模块输入的第一数据进行纠检错解码;第二解码模块用于对外部或逻辑模块输入的第二数据进行纠检错解码。

112.本发明一实施方式中,编码模块的编码方式与解码模块的解码方式根据不同的神经元模型,采用不同的编解码位数,对输入的数据进行多位错纠正以及多位错检测。

113.实施例4:

114.一种脉冲神经元加固方法,包括如下步骤:

115.对外部输入的第一数据和或第二数据进行原始存储,并对该输入的第一数据和或第二数据进行编码;

116.编码后的第一数据、第二数据进行分别存储;

117.对编码后的第一数据和或第二数据进行纠检错解码;

118.当解码时出现的错误数据较少时,对错误数据进行纠正后,用于配置脉冲神经元;当解码时出现的错误数据较多时,利用原始存储的数据配置脉冲神经元,并利用原始存储的数据对编码前的相应错误数据进行替换。

119.本发明一实施方式中,第一数据为配置信息,可配置脉冲神经元生成lif神经元或izhikevich神经元或hodgkin-huxley神经元。

120.本发明一实施方式中,第二数据为模型参数,可配置脉冲神经元生成对应的兴奋或抑制的神经元放电的脉冲信号。

121.本发明一实施方式中,原始存储与编码后存储空间隔离,或原始存储进行独立加固,用于减小空间单粒子效应的影响。

122.本发明一实施方式中,第原始存储采用十字交叉布局方式与编码后存储空间隔离,且根据脉冲神经元工作的空间环境,确定空间隔离距离;其中空间环境包括太空轨道高度、空间辐照环境、空间隔离的布局方式。

123.本发明一实施方式中,采用ecc编码方式以及ecc解码方式。

124.本发明一实施方式中,纠检错解码时,对输入的数据进行一位错纠正、多位错检测。

125.本发明一实施方式中,解码时出现多位错时,利用原始存储的数据配置脉冲神经元。

126.本发明一实施方式中,编码方式与解码方式相匹配,且根据不同的神经元模型,采用不同的编解码位数,对输入的数据进行多位错纠正以及多位错检测。

127.本发明一实施方式中,采用两路编码电路,其中一路对第一数据进行编码,另一路对第二数据进行编码。

128.本发明一实施方式中,采用两路解码电路,其中一路对第一数据进行纠检错解码,另一路对第二数据进行纠检错解码。

129.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

130.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。