1.本发明属于电子琴技术领域,特别涉及一种教学用乐理电子琴。

背景技术:

2.随着人们生活水平的提高,琴棋书画已然成为人们业余时间陶冶情操、精神享受的重要组成部分。电子琴是一种人们喜闻乐见的音乐器件,音色多、音质好和功能强大受到人们喜欢,也是学生学习音乐最普遍的入门乐器之一。利用电子琴音乐合成的特殊功能,对学生进行综合音乐能力的培养,以激发他们从内心对音乐的理解热爱。

3.电子琴是一种键盘乐器,其实它就是一种电子合成器,它采用大规模集成电路,大多配置声音记忆存储器。现有的音乐课堂使用的电子琴大多采用电教板,通过教鞭头部的磁感线圈来感应电教板上五线谱下埋设的导体产生的磁场,但是采用电磁感应容易产生涡流,线圈之间有可能有杂物进入,一旦产生电涡流,就如同电磁炉一样,安全性问题非常明显;磁感应线圈的外圈上可能会存在磁场泄露的问题,有产生辐射的可能。

技术实现要素:

4.针对上述问题,本发明提供一种新的教学用乐理电子琴。

5.本发明具体技术方案如下:

6.本发明提供一种教学用乐理电子琴,包括可折叠的琴体,所述琴体上设有手写用五线谱表,所述五线谱表的背面设有与谱线对应平行的多条金属线,所述琴体内设有电路板,所述电路板上集成有主控电路以及与所述主控电路通讯的时钟驱动电路、扫描电路和扫描拾捡电路;

7.所述时钟驱动电路用于给扫描电路和扫描拾捡电路提供时钟输入信号,扫描电路用于接收主控电路输出的信号实时向五线谱表下埋设的金属丝通入脉冲电流,产生相应的扫描脉冲信号,所述扫描拾捡电路用于在工作时接收扫描脉冲信号并发送给主控电路,所述主控电路用于对扫描脉冲信号进行处理以及输出读写信号脉冲给时钟驱动电路。

8.本发明所取得的有益效果:

9.本发明提供一种新的教学用乐理电子琴,通过在五线谱表下埋设金属丝,扫描电路向金属丝通入电路产生扫描脉冲信号,避免了电磁感应电路产生涡流的可能,也避免了磁场泄露产生辐射的可能。

附图说明

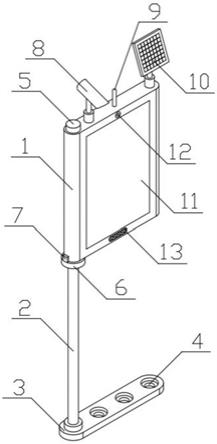

10.图1为目前的五线谱电教板的结构示意图;

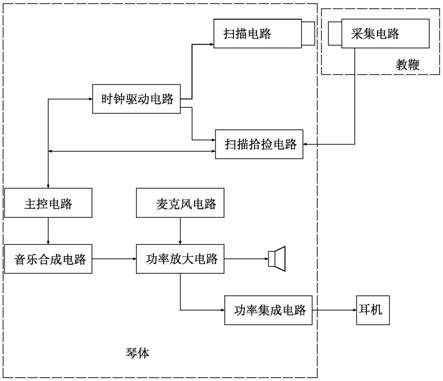

11.图2为目前的五线谱电教板的结构框图;

12.图3为本发明中教学用乐理电子琴的结构框图;

13.图4为本发明中琴体的结构示意图;

14.图5为本发明中教鞭的结构示意图;

15.图6为本发明中主控电路、时钟驱动电路、扫描电路和扫描拾捡电路的电路图;

16.图7为本发明中麦克风电路的电路图;

17.图8为本发明中音乐合成电路、功率放大电路和功率集成电路的电路图;

18.图9为本发明中电源电路的电路图;

19.图10为本发明中第一信号采集电路的电路图;

20.图11为本发明中第二信号采集电路的电路图;

21.图12为本发明中电源转换电路的电路图。

22.图1中,1为壳体,2为扬声器,3为键盘图形,4为演示板,5为五线谱表,6为电源插座,7为控制板,8为颤音开关,9为键盘显示灯开关,10为变调开关—c,11变调开关—f,12变调开关—g,13为音量旋钮,14为教鞭插孔,15为电源保险,16为电源开关,17为教鞭,18为音高显示灯。

具体实施方式

23.在对本技术实施例的技术方案说明之前,首先结合附图对本技术实施例的技术场景进行说明。

24.参见图1,为一种五线谱电教板的结构示意图。该结构由壳体、演示板和教鞭组成,在教鞭顶部装有感应线圈,在演示板上五线谱表下面分别埋设一系列与谱线平行对应的导线、导体其中的一种。在演示时,将教鞭插入教鞭插孔,使用者可随意在演示板的谱线上书写音符或乐句,当教鞭去触指时,扬声器中便会发出所触指的音符在五线谱上所处位置的对应音高

25.参见图2,为电教板的电路框图,由电子琴电路板、键盘显示电路板、时间分割扫描和控制电路板、捡拾电路板和供电电源20组成。电子琴电路由主振荡器21、音频产生电路22、音频选通电路23、音色滤波器24、放大器25和扬声器2组成;时间分割扫描和控制电路由时钟振荡器26、时分割脉冲分配器27、扫描电路驱动器28、时分割选通门29和埋设在五线谱表的普线下的一系列导体19组成。

26.工作时,时钟振荡器产生一系列频率恒定的脉冲输入时分割脉冲分配器,脉冲分配器产生时分割信号,分别输送到扫描电路驱动器中,向埋设在五线谱表的相应谱线下的一系列导体m中通入扫描脉冲电路,产生相应的时分割扫描脉冲磁场,同时将输出的时分割信号分别送入时分割选通门。拾捡电路由装于教鞭前端的感应线圈23和扫描磁场拾捡器32构成,感应线圈拾捡到相应的时分割扫描脉冲磁场信号,经感应线圈的感应电路放大整形后输出的信号送入时分割选通门;

27.对应到结构图中,即在演示时,将教鞭插入教鞭插孔,当使用者用教鞭触指到演示板五线谱表上的某一条谱线的某音符时,通过装于教鞭前端的感应线圈,将与所述谱线相应的时分割扫描脉冲磁场信号拾捡,经扫描磁场拾捡器控制时分割选通门,当所述的信号与时分割脉冲分配器来的信号同步时,则发生控制信号的控制音频选通电路使电子琴电路发出所触音符在五线谱表上所处位置的对应音高。

28.但是采用电磁感应容易产生涡流,线圈之间有可能有杂物进入,一旦产生电涡流,就如同电磁炉一样,安全性问题非常明显;磁感应线圈的外圈上可能会存在磁场泄露的问题,有产生辐射的可能。

29.本技术提供了一种教学用乐理电子琴。

30.如图3所示,包括可折叠的琴体,所述琴体上设有手写用五线谱表,所述五线谱表的背面设有与谱线对应平行的多条金属线,所述琴体内设有电路板,所述电路板上集成有主控电路以及与所述主控电路通讯的时钟驱动电路、扫描电路和扫描拾捡电路;

31.所述时钟驱动电路用于给扫描电路和扫描拾捡电路提供时钟输入信号,扫描电路用于接收主控电路输出的信号实时向五线谱表下埋设的金属丝通入脉冲电流,产生相应的扫描脉冲信号,所述扫描拾捡电路用于在工作时接收扫描脉冲信号并发送给主控电路,所述主控电路用于对扫描脉冲信号进行处理以及输出读写信号脉冲给时钟驱动电路。

32.本发明提供一种新的教学用乐理电子琴,通过在五线谱表下埋设金属丝,扫描电路向金属丝通入电路产生扫描脉冲信号,避免了电磁感应电路产生涡流的可能,也避免了磁场泄露产生辐射的可能;同时,采用主控电路对各电路进行控制,使得信号处理速度更快,且更加智能。

33.如图3、图5所示,本实施例中还包括教鞭7,所述琴体与所述教鞭之间电连接;所述教鞭的头部设有金属接收头8,且所述教鞭内集成有采集电路,所述采集电路用于在金属接收头靠近或者接触五线谱表时接收金属丝发出的扫描脉冲信号,并将扫描脉冲信号发送给扫描拾捡电路;所述金属丝发出的是一个经100-200hz左右调制的25khf方波信号。

34.本实施例中教鞭的头部采用金属接收头替换感应线圈,可以避免涡流的产生。

35.本实施例中所述电路板上还集成有音乐合成电路、功率放大电路以及供电电路;所述主控电路对扫描脉冲信号处理后输出midi信号给音乐合成电路,所述音乐合成电路用于将midi信号合成为数字音频流信号,并将数字音频流信号转换为模拟量信号,所述功率放大电路用于将模拟量信号放大后输出给扬声器播放,所述电源电路用于将输入的交流电转换成工作电压进行供电。

36.如图4所示,所述琴体包括键盘1和显示板2,两者通过转轴转动连接,键盘上设有琴键区和五线谱大谱表区,所述琴键区设有琴键3,所述五线谱大谱表区设有五线谱大谱表4以及多个显示灯5,各所述显示灯5设于所述五线谱大谱表4上且在所述五线谱大谱表4上的位置与琴键区和五线谱大谱表区,所述琴键区设有键盘3,所述五线谱大谱表区设有五线谱大谱表4以及多个显示灯5,各所述显示灯5设于所述五线谱大谱表4上且在所述五线谱大谱表4上的位置与键盘3上的音调相对应3上的音调相对应;显示板上设有五线谱表6,五线谱表的谱线下埋设有与谱线平行对应的金属丝;琴体的侧壁上还设有插孔,包括教鞭插孔,耳机插孔,电源插孔,usb插孔,网线插孔等,其中,教鞭插入教鞭插孔时对应扫描拾捡电路开始工作。

37.如图5所示,教鞭上还设有两开关,分别用于控制升音和降音,可以在用教鞭演示乐曲时对音调进行临时的升降处理,以满足乐曲需要;还可以对五线谱上的每一个音随意的进行音调的升降处理,所以用教鞭在五线谱上除了可以进行首调唱名法教学外也可以进行固定调的唱名法教学;其中。按下升音开关时,所发出的音调即会自动升高半音,按下降音开关时,所发出的音调即会自动降低半音。按下升音或降音开关时,通过采集电路将升降音信号发送给扫描拾捡电路。

38.该教学用乐理电子琴包括键盘和显示板,键盘和显示板通过转轴转动连接,在不使用时,显示板可以扣合在键盘上不仅,可以对琴体进行防护,键盘上设置琴键和五线谱大

谱表,五线谱大谱表上的多个显示灯的位置与键盘上的音调相对应,可以根据调名或调号查找音阶在键盘及谱表上的对应位置、根据琴键音名查找对应的调名或调号、不同调式的首调唱名在琴键上的排列顺序、不同音调的琴键之间的音程关系、和弦音的组合规则以及在键盘上的排列规律,把虚拟抽象的乐理知识直观化、综合化、简单化,趣味化,有利于学生对乐理知识的掌握。

39.如图6所示,所述主控电路包括主控芯片u1(87c51)、锁存器u2(74ls373)、存储芯片u3(29)和静态存储器u6(6264),主控芯片u1的31引脚连接vcc,19引脚通过电容c1接地,18引脚通过电容c2接地,且18引脚和19引脚之间并联有晶振y1(18.432m),9引脚连接非门芯片u5a的输出端,u5a的输入端分别通过二极管d1(in4148)连接vcc以及通过电容c4(10u)接地,二极管d1的两端并联有电阻r1(20k),u1的10引脚接收输入信号,11引脚输出midi信号,30引脚连接锁存器u2的le引脚,32-39引脚分别对应连接锁存器u2的输入引脚d7-d0,21-28引脚分别对应连接存储芯片u3的地址线引脚a8-a15,17引脚分别连接存储芯片u3的oe引脚、静态存储器u6的读出允许信号引脚oe以及时钟驱动电路,16引脚分别连接静态存储器u6的写允许信号引脚we以及时钟驱动电路,1-3引脚分别连接存储芯片u3的地址线引脚a16-a18,8引脚分别连接存储芯片u3的ce引脚、静态存储器u6片选信号引脚cs2以及时钟驱动电路,锁存器u2的oe引脚接地,输出引脚q0-q7分别与存储芯片u3的地址线引脚a0-a7连接,且静态存储器u6的地址线引脚a0-a12与存储芯片u3的地址线引脚a0-a12对应并联,存储芯片u3的数据线引脚dq0-dq7、静态存储器u6的数据线引脚d0-d7分别与锁存器u2的输入引脚d0-d7并联,且存储芯片u3的we引脚连接vcc。

40.如图6所示,所述主控电路中还包括存储芯片u4,存储芯片u4和存储芯片u3的连接方式一样,且型号均为29c040。

41.如图6所示,所述主控芯片接收服务器端的信号并输出信号给服务器端,其具体电路如下:主控芯片u1的10引脚连接光耦u16(6n135)的6引脚,光耦u16的8引脚连接件vdd,6引脚通过电阻r21(4.7k)连接vdd,5引脚接地,2引脚通过电阻r20(220)连接接口mdin的1引脚以及接口midiin1的4引脚,3引脚连接接口midiin的5引脚以及接口mdin的2引脚,2引脚和3引脚之间并联二极管d2(in4148);主控芯片u1的11引脚通过与非门芯片u7b和电阻r6(2k)连接三极管q1(8050)的基极,三极管q1的发射极接地,集电极通过电阻r7(270)连接接口mdout的2引脚和接口midiout1的5引脚,接口mdout的1引脚和接口midiout1的4引脚并联并通过电阻r8(200)连接vcc以及通过电容c30(220p)接地;其中,接口mdin、midiin1、mdout和midiout1均与服务器端连接,接口mdin、midiin1用于接收服务器端的midi信号,接口mdout和midiout1向服务器端发送midi信号。

42.如图8所示,所述音乐合成电路包括音乐合成器u19(cs9236)以及数模转换器u20(cs4333),音乐合成器u19的20引脚输入midi信号,24引脚分别通过电阻r58(47k)连接3v、通过二极管d3(in4148)连接3v以及通过电容c35(1u)接地,23引脚通过电阻r56(10k)连接3v,19、22、8和5引脚均接地,9和21引脚均连接3v,6引脚通过电容c53(22p)接地,7引脚通过电容c54(10p)接地以及连接数模转换器u20的4引脚,6引脚和7引脚之间并联晶振xtal1(16.9344m),10引脚和11引脚分别连接数模转换器u20的3引脚和1引脚,数模转换器u20的2引脚通过电阻r57(10k)连接3v,6引脚接地,7引脚连接a3v,5引脚上串联有电容c5(10u)和电阻r61(15k),8引脚上串联有电容c6(10u)和电阻r62(15k),且电阻61的负极连接功率放

大电路以及通过电容c56(1000p)接地,电阻r62的负极连接功率放大电路以及通过电容c57(1000p)接地。

43.如图7所示,所述电路板上还集成有麦克风电路,所述麦克风电路包括运算放大器u21c和u21b,运算放大器u21c的10引脚通过电阻r71(20k)连接2.5v,9引脚上串联电阻r70(20k)和电容c60(0.1u),电容c60的正极通过电阻r75(10k)连接5v以及连接接口mic,接口mic外接话筒,u21c的9引脚与8引脚之间通过电阻r69(27k)并联,且通过电容c29(0.1u)和电阻r72(47k)连接运算放大器u21b的6引脚,u21b的5引脚通过电阻r74(20k)连接2.5v,7引脚通过电容c28(0.1u)输出micout给功率放大电路,且6引脚和7引脚之间通过电阻r73(100k)并联。

44.如图8所示,所述功率放大电路包括运算放大器u21a和u21d(lm324),运算放大器u21a的2引脚通过电阻r12(15k)连接电阻r16的负极以及通过电阻r67(47k)连接micout,3引脚连接2.5v,4引脚连接5v,11引脚接地,1引脚通过电容c15(47u)连接接口aout的2引脚,且1引脚和2引脚之间通过电阻r14(150k)并联,电阻r14两端并联有电容c14(22p);

45.运算放大器u21d的12引脚连接2.5v,13引脚通过电阻r13(15k)连接电阻62的负极以及通过电阻r68(47k)连接micout,14引脚通过电容c16(47u)连接接口aout的3引脚,且13引脚和14引脚之间通过电阻r16(150k)并联,电阻r16两端并联有电容61(22p),接口aout外接扬声器。

46.如图8所示,所述功率放大电路还将输出的信号给功率集成电路,所述功率集成电路包括功率集成芯片u15(tea2025),u15的10引脚通过电容c17(1u)和电阻r17(150k)连接电容c16的输出端,7引脚通过电容c18(1u)和电阻r59(150k)连接电容c15的输出端,电阻r17的负极通过电阻r18(20k)接地,电阻r59的负极通过电阻r19(20k)接地,u15的11引脚通过电容c19(100u)接地,6引脚通过电容c20(100u)接地,8引脚通过电容c23(100u)接地,2引脚通过电容c15(470u)连接耳机接口sp2以及通过电容c32(0.22u)接地,3引脚通过电容c22(100u)与2引脚并联,15引脚通过电容c24(470u)连接耳机接口sp1以及通过电容c31(0.22u)接地,14引脚通过电容c21(100u)与15引脚并联,16引脚连接9v、通过电容c26(100u)接地以及通过电容c66(0.1u)接地;耳机接口sp2和sp1外接耳机。

47.如图6所示,所述时钟驱动电路包括译码器u8(74hc138)、与非门芯片u7a(74hc00)和非门芯片u5b、u5c(4069),非门芯片u7a的1引脚连接主控芯片u1的17引脚,2引脚连接主控芯片的16引脚,3引脚连接译码器u8的6引脚,译码器u8的5引脚通过非门芯片u5b连接主控芯片的8引脚;

48.与非门芯片u7a的1引脚以及静态存储器u6的读出允许信号引脚oe,16引脚分别连接与非门芯片u7a的2引脚以及静态存储器u6的写允许信号引脚we,4引脚通过非门芯片u5c连接静态存储器u6的片选信号引脚cs1,1引脚分别连接锁存器u2的q0引脚、存储芯片u3的a0引脚和静态存储器u6的a0引脚,2引脚分别连接锁存器u2的q1引脚、存储芯片u3的a1引脚和静态存储器u6的a1引脚,3引脚分别连接锁存器u2的q3引脚、存储芯片u3的a3引脚和静态存储器u6的a3引脚,11-15引脚分别输出cs0-cs4。

49.如图9所示,所述电源电路包括电源变换器u22(mc34063a)、稳压器u23(mc7805)、二极管d4-d7(in4007),二极管d6和d4串联形成的回路与d7和d5串联形成的回路并联,d4的阳极和d5的阳极均接地,且d6的阳极连接接口power1的2引脚,d7的阳极连接接口power1的

1引脚,接口power1外接电源线,二极管d7的阴极输出9v、通过电容c62(2200u/16v)接地以及通过电阻r15(1)连接电源变换器u22的6引脚,电源变换器u22的6引脚通过电容c27(1000u/16v)接地以及通过电阻r64(1)与7引脚并联,电阻r65(1)和电阻r66(1)分别并联在电阻r64两端,u22的8引脚和1引脚与7引脚并联,3引脚通过电容c59(470p)接地,4引脚接地,2引脚通过电感l1(220uh)输出vcc以及通过电阻r51(2k)、r50(1k)和r63(1k)接地,5引脚与电阻r63的正极连接,电感l1的输入端通过二极管d8(in5819)接地,输出端通过电容c58(1000u)接地;

50.稳压器u23的1引脚输入9v,2引脚接地,3引脚输出5v、通过电容c68(10u)接地以及通过电阻r10(10k)和r11(10k)接地,电容c63(0.1u)和电容c65(0.1u)分别并联在电容c68的两端,电阻r10的负极输出2.5v,电容c12(10u)和电容c67(0.1u)分别并联在电阻r11的两端。

51.电源电路还包括三极管q2(9013)和q3(9013),三极管q2的基极通过发光二极管led2(red)和led1(red)接地,集电极连接vdd,发射极输出3v,且基极与集电极之间并联电阻r60(1k);

52.三极管q3的基极通过发光二极管led4(red)和led3(red)接地,集电极输入5v,发射极输出a3v、通过电容c64(0.1u)接地以及通过电容c11(470u)接地,基极与集电极之间并联电阻r79(2k),集电极与发射极之间并联二极管d11(in4007)。

53.如图6所示,所述扫描电路包括触发器u9(74hc373)、u10(74hc373)、u11(74hc373)以及连接器con26,所述触发器u9的输入引脚d1-d8、触发器u10的输入引脚d1-d8、触发器u11的输入引脚d1-d8分别与锁存器u2的输入引脚d0-d7并联,触发器u11的输出引脚q1-q8、触发器u10的输出引脚q1-q8、触发器u9的输出引脚q1-q8分别连接连接器con26的2-25引脚,触发器u11的1引脚连接vcc,11引脚通过非门芯片u5d(4069)连接cs0引脚,触发器u10的1引脚连接vcc,11引脚通过非门芯片u5e连接cs1引脚,触发器u9的1引脚连接vcc,11引脚通过非门芯片u5f连接cs2引脚。

54.所述采集电路包括第一信号采集电路、第二信号采集电路以及电源转换电路,其中,所述教鞭设有两个,第一信号采集电路和第二信号采集电路分别对应一个教鞭;

55.如图10所示,所述第一信号采集电路包括运算放大器u17a-u17d(tl084),运算放大器u17a的输入端2引脚通过电阻r28(47k)连接接口jb1的2引脚,3引脚通过电阻r29(47k)连接vgnd,11引脚接地,4引脚连接jb5v,输出端1引脚通过电阻r43(20k)和电容c48(1000p)连接u17b的5引脚,且1引脚和2引脚之间并联电阻r34(1m),电阻r28与接口jb1的2引脚之间串联有电容c39(0.01u)、c35(0.01u)和c36(0.01u),电容c36的正极与c35的负极之间并联有串联连接的电阻r23(330k)和r22(330k),电阻r23的负极通过电容c33(0.022u)接地,电容c36的负极通过电阻r26(150k)接地,电阻r43的负极与运算放大器u17b的7引脚之间并联电阻r37(20k),且电阻r43的负极通过电容c49(220p)连接vgnd,电容c48的负极通过电阻r38(20k)连接vgnd,运算放大器u17b的6引脚通过电阻r48(27k)连接vgnd,且6引脚与7引脚之间并联电阻r30(47k),7引脚通过电容c40(0.01u)和电阻r36(4.7k)连接运算放大器u17c的9引脚,运算放大器u17c的10引脚通过电阻r53(15k)连接vgnd,9引脚与8引脚之间并联电容c52(27p),8引脚通过电容c41(0.1u)连接运算放大器u17d的13引脚,电容c52两端并联有串联连接的电阻r55(20k)和变阻器rv1(47k),电容c41的负极通过电阻r44(47k)接地以及

通过电阻r77(68k)连接jb5v,运算放大器u17d的12引脚连接vgnd,14引脚输出jb1,接口jb1的1引脚接地,3引脚和4引脚分别输出jb1up和jb1dn;

56.其中,u17a、u17b组成带通滤波放大,u17c是教鞭的感应灵敏度调整,u17d为信号的采集阈值门,当采集的信号幅度大于阈值电压,即被采用并去做选音处理;

57.如图11所示,第二信号采集电路包括运算放大器u18a-u18d(tl084),运算放大器u18d的输入端13引脚通过电阻r31(47k)连接接口jb2的2引脚,12引脚通过电阻r32(47k)连接vgnd,输出端14引脚通过电阻r39(20k)和电容c47(1000p)连接u18c的10引脚,且13引脚和14引脚之间并联电阻r35(1m),电阻r31与接口jb2的2引脚之间串联有电容c42(0.01u)、c37(0.01u)和c38(0.01u),电容c38的正极与c37的负极之间并联有串联连接的电阻r25(330k)和r24(330k),电阻r25的负极通过电容c34(0.022u)接地,电容c38的负极通过电阻r27(150k)接地,电阻r39的负极与运算放大器u18c的8引脚之间并联电阻r40(20k),且电阻r39的负极通过电容c46(220p)连接vgnd,电容c47的负极通过电阻r41(20k)连接vgnd,运算放大器u18c的9引脚通过电阻r49(27k)连接vgnd,且9引脚与8引脚之间并联电阻r33(47k),8引脚通过电容c43(0.01u)和电阻r42(4.7k)连接运算放大器u18a的2引脚,运算放大器u18a的11引脚接地,3引脚通过电阻r52(15k)连接vgnd,4引脚连接jb5v,2引脚与1引脚之间并联电容c51(27p),1引脚通过电容c44(0.1u)连接运算放大器u18b的6引脚,电容c51两端并联有串联连接的电阻r54(20k)和变阻器rv2(47k),电容c44的负极通过电阻r45(47k)接地以及通过电阻r78(68k)连接jb5v,运算放大器u18b的5引脚连接vgnd,7引脚输出jb2,接口jb2的1引脚接地,3引脚和4引脚分别输出jb2up和jb2dn;

58.其中,u18d、u18c组成带通滤波放大,u17a是教鞭的感应灵敏度调整,u17b为信号的采集阈值门,当采集的信号幅度大于阈值电压,即被采用并去做选音处理;其中,接口jb1和jb2均用来外接教鞭,本实施例中是以两个教鞭为例;

59.如图12所示,电源转换电路包括电阻r9(4.7)、r46(10k)、r47(10k)、电容c13(220u)和c50(10u),电阻r9和电容c13串联,电阻r9的正极输入vcc,负极输出jb5v,电容c13的负极接地,电阻r46和电阻r47串联,电容c50并联在电阻r47两端,且电阻r46的正极输入jb5v,负极输出vgnd;

60.所述扫描拾捡电路包括教鞭接收电路以及教鞭升降音控制电路;

61.如图6所示,所述教鞭接收电路包括驱动信号芯片u12(74hc244)和计数器u14(74hc393),驱动信号u12的1引脚和19引脚并联后连接译码器u8的12引脚,输出引脚1y1-1y4、2y1-2y4和u13的输出引脚1y1-1y4、2y1-2y4分别与锁存器u2的输入引脚d0-d7并联,驱动信号芯片u12的输入引脚1a1-1a4分别连接计数器u14a的输出引脚q0-q3,输入引脚2a1-2a4分别连接计数器u14b的输出引脚q0-q3,计数器u14a的时钟输入引脚连接jb1,复位输入引脚与u14b的复位输入引脚并联并连接主控芯片u1的7引脚,u14b的时钟输入引脚连接jb2;

62.如图6所示,所述教鞭升降音控制电路包括驱动信号芯片u13,驱动信号芯片u13的1引脚和19引脚并联后连接译码器u8的11引脚,输入引脚ia1通过电阻r2(4.7k)连接vcc、通过电容c7(1u)接地以及连接jb2up,输入引脚ia2通过电阻r3(4.7k)连接vcc、通过电容c8(1u)接地以及连接jb2dn,输入引脚ia3通过电阻r4(4.7k)连接vcc、通过电容c9(1u)接地以及连接jb1up,输入引脚ia4通过电阻r5(4.7k)连接vcc、通过电容c10(1u)接地以及连接

jb1dn,输出引脚iy1-2y4分别与锁存器u2的输入引脚d0-d7并联。

63.虽然本说明书包含很多具体的实施细节,但是这些不应当被解释为对任何发明的范围或者对可以要求保护的内容的范围的限制,而是作为可以使特定发明的特定实施方式具体化的特征的说明。在独立的实施方式的语境中的本说明书中描述的特定特征还可以与单个实施方式组合地实施。相反地,在单个实施方式的语境中描述的各种特征还可以独立地在多个实施方式中实施,或者在任何合适的子组合中实施。此外,虽然以上可以将特征描述为组合作用并且甚至最初这样要求,但是来自要求的组合的一个或多个特征在一些情况下可以从该组合去掉,并且要求的组合可以转向子组合或者子组合的变形。

64.在特定情况下,多任务处理和并行处理可以是有利的。此外,上述实施方式中的各种系统模块和组件的分离不应当理解为在所有实施方式中要求这样的分离。

65.已经描述了主题的特定实施方式。其他实施方式在以下权利要求的范围内。例如,在权利要求中记载的活动可以以不同的顺序执行并且仍旧实现期望的结果。作为一个实例,为了实现期望的结果,附图中描述的处理不必须要求示出的特定顺序或者顺序次序。在特定实现中,多任务处理和并行处理可以是有优势。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。