1.本发明实施例涉及通信领域,具体而言,涉及一种输出高谐波抑制的倍频信号的方法、装置及存储介质。

背景技术:

2.现有技术中,在输出倍频信号的过程中,例如需要二倍频信号,则直接将初始信号输入到二倍频器中,由二倍频器输出二倍频信号。然而,在此过程中,二倍频器还会输出初始信号、三倍频信号、四倍频信号等等信号。造成输出的倍频信号的谐波抑制比低。

技术实现要素:

3.本发明实施例提供了一种输出高谐波抑制的倍频信号的方法、装置及存储介质,以至少解决相关技术中输出的倍频信号的谐波抑制比低的问题。

4.根据本发明的一个实施例,提供了一种输出倍频信号的方法,包括:获取初始信号;将所述初始信号输入到目标电路中,其中,所述目标电路中包括并联电路,所述并联电路的第一电路上设置有倍频器,所述并联电路的第二电路上设置有相位调整模块,所述第一电路与所述目标电路的输入端与输出端连接,所述第二电路与所述输入端和所述输出端保持断开状态,所述相位调整模块用于将所述第二电路的相位调整为目标相位,所述目标相位与所述第一电路的第一相位的相位差值大于90度;将所述目标电路输出的目标信号作为所述初始信号的倍频信号。

5.根据本发明的另一个实施例,提供了一种输出倍频信号的装置,包括:目标电路,所述目标电路中包括并联电路,所述并联电路的第一电路上设置有倍频器,所述并联电路的第二电路上设置有相位调整模块,所述第一电路与所述目标电路的输入端与输出端连接,所述第二电路与所述输入端和所述输出端保持断开状态,所述相位调整模块用于将所述第二电路的相位调整为目标相位,所述目标相位与所述第一电路的第一相位的相位差值大于90度,所述目标电路用于将输入的初始信号倍频为所述初始信号的倍频信号。

6.根据本发明的又一个实施例,还提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

7.根据本发明的又一个实施例,还提供了一种电子装置,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

8.通过本发明,由于设置了相位调整模块,将所述第二电路的相位调整为与第一电路的相位的相位差值大于90度的相位,且将相位调整模块在第二电路中断开,将倍频器在第一电路中连接,从而使相位调整模块可以抵消第一电路中的倍频器输出的干扰信号,得到更加纯净的倍频信号。可以解决输出的倍频信号的谐波抑制比低问题,达到提高输出的倍频信号的频谱纯度的效果。

附图说明

9.图1是根据本发明实施例的输出倍频信号的方法的硬件结构图;

10.图2是根据本发明实施例的输出倍频信号的方法的流程图;

11.图3是根据本发明实施例的输出倍频信号的方法的系统结构示意图;

12.图4是根据本发明实施例的输出倍频信号的方法的系统结构示意图;

13.图5是根据本发明实施例的输出倍频信号的方法的倍频器的电路结构图;

14.图6是传统平衡式二倍频变频增益及谐波抑制比示意图;

15.图7是根据本发明实施例的输出倍频信号的方法的第一二倍频器的变频增益及谐波抑制比示意图;

16.图8是根据本发明实施例的输出倍频信号的方法的基次谐波抑制比对比曲线示意图;

17.图9是根据本发明实施例的输出倍频信号的装置的目标电路示意图。

具体实施方式

18.下文中将参考附图并结合实施例来详细说明本发明的实施例。

19.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

20.本技术实施例中所提供的方法实施例可以在移动终端、计算机终端或者类似的运算装置中执行。以运行在移动终端上为例,图1是本发明实施例的一种输出倍频信号的方法的移动终端的硬件结构框图。如图1所示,移动终端可以包括一个或多个(图1中仅示出一个)处理器102(处理器102可以包括但不限于微处理器mcu或可编程逻辑器件fpga等的处理装置)和用于存储数据的存储器104,其中,上述移动终端还可以包括用于通信功能的传输设备106以及输入输出设备108。本领域普通技术人员可以理解,图1所示的结构仅为示意,其并不对上述移动终端的结构造成限定。例如,移动终端还可包括比图1中所示更多或者更少的组件,或者具有与图1所示不同的配置。

21.存储器104可用于存储计算机程序,例如,应用软件的软件程序以及模块,如本发明实施例中的输出倍频信号的方法对应的计算机程序,处理器102通过运行存储在存储器104内的计算机程序,从而执行各种功能应用以及数据处理,即实现上述的方法。存储器104可包括高速随机存储器,还可包括非易失性存储器,如一个或者多个磁性存储装置、闪存、或者其他非易失性固态存储器。在一些实例中,存储器104可进一步包括相对于处理器102远程设置的存储器,这些远程存储器可以通过网络连接至移动终端。上述网络的实例包括但不限于互联网、企业内部网、局域网、移动通信网及其组合。

22.传输装置106用于经由一个网络接收或者发送数据。上述的网络具体实例可包括移动终端的通信供应商提供的无线网络。在一个实例中,传输装置106包括一个网络适配器(network interface controller,简称为nic),其可通过基站与其他网络设备相连从而可与互联网进行通讯。在一个实例中,传输装置106可以为射频(radio frequency,简称为rf)模块,其用于通过无线方式与互联网进行通讯。

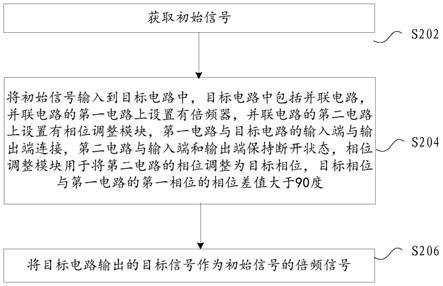

23.可选地,如图2所示,上述输出倍频信号的方法包括:

24.s202,获取初始信号;

25.s204,将所述初始信号输入到目标电路中,其中,所述目标电路中包括并联电路,所述并联电路的第一电路上设置有倍频器,所述并联电路的第二电路上设置有相位调整模块,所述第一电路与所述目标电路的输入端与输出端连接,所述第二电路与所述输入端和所述输出端保持断开状态,所述相位调整模块用于将所述第二电路的相位调整为目标相位,所述目标相位与所述第一电路的第一相位的相位差值大于90度;

26.s206,将所述目标电路输出的目标信号作为所述初始信号的倍频信号。

27.可选地,上述输出倍频信号的方法可以但不限于应用于对初始信号进行倍频的过程中。如果希望获取几倍频信号,倍频器就选择使用几倍频器。如获取二倍频信号时,可以将二倍频器与相位调整模块并联,将相位调整模块与电路保持断开状态,将相位调整模块与电路连接,且相位调整模块将相位调整模块所在的第二电路的相位调整为目标相位,从而与二倍频器所在的第一电路的相位差值在90度以上。此时,由于第一电路与第二电路的相位差值在90度以上,因此,相位调整模块所在的第二电路可以产生与第一电路相反的信号,抵消掉第二电路的倍频器在倍频的过程中产生的干扰信号,使倍频信号更加纯净,提高了输出的倍频信号的频谱纯度。

28.可选地,所述相位调整模块还用于将所述第二电路的谐波幅度设置为与所述第一电路的谐波幅度的差值小于第一阈值的谐波幅度。

29.如果两个电路的谐波幅度的差值小,则可以保证第一电路的干扰信号被第二电路的信号尽可能多的抵消,提高输出的倍频信号的谐波抑制比。需要说明的是,将第二电路的谐波幅度设置为与所述第一电路的谐波幅度的差值小于第一阈值的谐波幅度,实际上为在相位调整模块和断开的开关共同作用下谐波幅度与第一电路的谐波幅度的差值小于第一阈值。

30.可选地,所述目标相位与所述第一相位的相位差值为180度。如果第二电路与第一电路的相位相差180度,则表示相位完全相反,则可以尽可能多的抵消第一电路的干扰信号。

31.可选地,所述相位调整模块为移相器或者反相器或者放大器。也就是说,本技术实施例中的相位调整模块为任意的可以调整相位的装置或者电路或者模块单元,本技术实施例并不限定。

32.所述第一电路通过单刀双掷开关与所述输入端与所述输出端连接。可选地,如果单刀双掷开关与目标电路的第一电路连接,则初始信号可以经过第一电路的倍频器得到倍频信号,在此过程中,第二电路断开,第二电路的相位调整模块可以抵消一部分干扰信号。如果单刀双掷开关与目标电路的第二电路连接,则初始信号可以经过第二电路得到初始信号,在此过程中,第一电路可以抵消一部分干扰信号,达到对输出的初始信号进行过滤的效果。

33.可选地,所述倍频器为第一二倍频器,所述输出端后连接有第二二倍频器,所述将所述目标电路输出的目标信号作为所述初始信号的倍频信号包括:

34.在所述第一电路与所述目标电路的输入端与输出端连接,所述第二电路与所述输入端与所述输出端保持断开状态的情况下,所述初始信号经过所述第一二倍频器与所述第二二倍频器,输出四倍频信号;

35.在所述第一电路与所述目标电路的输入端与输出端保持断开状态,所述第二电路

与所述输入端与所述输出端连接的情况下,所述初始信号经过所述相位调整模块与所述第二二倍频器,输出二倍频信号。

36.通过本实施例,从而实现在获取输出的初始信号的倍频信号的过程中,提高输出的倍频信号的谐波抑制比的效果。

37.以下结合一个具体示例解释上述输出倍频信号的方法。

38.本技术实施例关于本振链路中倍频器的谐波抑制。本技术实施例提出了一种目标电路。如图3电路的系统框架图,该目标电路包括:单刀双掷开关304,相位调整模块306和倍频器308。单刀双掷开关与倍频器308连接,相位调整模块306断开。基次谐波(初始信号)由输入端302输入,经过倍频器308,由输出端输出二次谐波(倍频器308为二倍频器)。

39.作为一种可选的示例,本技术实施例中的目标电路中并联电路与一个二倍频器相连。如图4所示。图4中的f0为基次谐波,移相器为相位调整模块,rfin为基次谐波输入段,rfout为基次谐波输出端,x2 doubler1和x2 doubler2是二倍频器。箭头为信号强弱,带有方向。

40.当图4中系统处于x2工作模式时,单刀双掷开关虚线位置导通,实线位置断开,信号通过第一级的并联支路中的移相器和第二级倍频器级联;当系统处于x4工作模式时,单刀双掷开关实线位置导通,虚线位置断开,信号通过第一级的倍频器和第二级倍频器级联。x2工作模式即为输入基次谐波输出二次谐波,x4工作模式即为输入基次谐波,输出四次谐波。

41.与传统的二倍四倍频复用系统相比,本技术实施例提出的改进方案不仅没有增加硬件面积的占用,还能提高整体的谐波抑制比。

42.新型x2倍频器和x4倍频器复用系统包括两个单刀双掷开关,两级倍频器和一个移相器。两个单刀双掷开关控制其在不同的场景下选择第一级的不同通路。倍频器x2 doubler1实现输入信号从f0到2f0的倍频,倍频器x2 doubler2实现输入信号从2f0到4f0的倍频。

43.当单刀双掷开关打到实线处时,第一级电路中x2 doubler1导通,信号经过两级倍频器实现四倍频,实现输入信号从f0到4f0的四倍频。此时另一条通路上的移相器和两个断开的开关共同产生一个较小的信号和第一级倍频器输出信号反向叠加,可以起到抑制谐波的作用,从而提高整个四倍频的谐波抑制比。在倍频器的设计中,偶次谐波分量很容易通过差分电路抑制掉,基次谐波尤其是离输出有用频谱较近的基次谐波和三次谐波较难抑制,另外,第一级倍频器的基次谐波(f0)会和第二级倍频器的基次谐波(2f0)、二次谐波(4f0)等混频产生新的频谱分量。因此提高倍频器的基次谐波抑制比能够明显的改善倍频器的整体性能。

44.当单刀双掷开关打到虚线处时,第一级电路中移相器导通,其对于输入信号的频谱几乎没有什么副作用。信号通过移相器和x2 doubler2级联,实现二倍频,而移相器带来的增益也会改善二倍频的增益、平坦度和谐波抑制等。

45.原理结合图4继续说明。

46.在系统的输入端输入一个纯净的正弦信号acos(ω0t),其中ω0=2πf0。考虑两个单刀双掷开关均处于实线处,即第一级倍频器导通的情况。

47.忽略导通开关引入的损耗,那么节点2处的信号为acos(ω0t),经过第一级倍频器

后,节点3处的信号为:

48.a1cos(ω0t) a2cos(2ω0t) a3cos(3ω0t) a4cos(4ω0t)

…

49.其中a2为输出信号的幅度,基次谐波幅度为a1,三次谐波幅度为a3,四次谐波幅度为a4。如果是实际过程中,a2比较接近1,a1、a3、a4比较接近零。也就是说,最理想的结果为输出的是a2cos(2ω0t),但是会存在其他的信号干扰。而移相器会降低该干扰。

50.由于两个单刀双掷开关均在倍频器的通路上导通,开关在移相器的通路上断开。开关从输入端口到断路端口有一定的隔离度il,这使得节点4处的信号幅度衰减了il,同样的经过第二个开关,信号幅度会再衰减il。假设移相器的增益为1,那么节点5处的信号为b1cos(ω0t)。

51.图4中的移相器相位可调,保证节点5和节点3处的在f0处相位相反,那么节点6处的信号为:

52.|a

1-b1|cos(ω0t) a2cos(2ω0t) a3cos(3ω0t) a4cos(4ω0t)

…

53.从节点1到6处的第一级倍频器的基次谐波抑制明显得到了改善,对于四倍频器来说,输入信号的频谱变得“干净”,输出信号的谐波抑制也会得到改善。

54.考虑第二种场景,两个单刀双掷开关均处于虚线处,即第一级倍频器所在支路不导通,信号通过移相器级联第二级倍频器时,依然忽略开关带来的损耗,假设移相器的增益为1。那么节点6处的信号为:与传统的倍频器架构相比,此节点处的信号幅度略大一些,这对于和第二级倍频器级联后的输出信号来说,也增大了输出功率。

55.考虑到整个系统级联时,移相器所占芯片面积本就无法省掉,因此移相器的引入不会带来额外的面积。

56.例如设计doubler1为输入频率3.5ghz-6.5ghz的二倍频器,doubler2为输入频率7ghz-13ghz的二倍频器,当系统工作于四倍频模式时,两级倍频器级联,输入频率为3.5ghz-6.5ghz,输出频率为14ghz-26ghz;当系统工作于二倍频模式时,移相器和第二级倍频器级联,输入频率为7ghz-13ghz,输出频率为14ghz-26ghz。

57.采用平衡式倍频器的架构说明本发明所采用倍频器架构的有益之处,倍频器的电路结构图如图5所示,由一级平衡式倍频器和一级buffer组成。vcas为共源共栅管的栅极电压,vgm为共源管的栅极电压,vdd为电路的工作电压。

58.第一级二倍频器的变频增益及谐波抑制比如图6所示。h2为二次谐波功率,也就是需要的二倍频信号,hr1为基次谐波抑制比,hr3为三次谐波抑制比,hr4为四次谐波抑制比。在关心频段内,倍频器的变频增益为-1dbˉ3db;倍频器的基次谐波抑制比hr1在26dbc以上,三次谐波抑制比hr3在32dbc以上,四次谐波抑制比hr4在28dbc以上。第一级倍频器的并联支路上增加了移相器单元后,对其相位变化扫参优化,当移相器的相位变化使得两路的相位差大概在180

°

时,倍频器的谐波抑制比明显提高,其变频增益及谐波抑制比如图7所示。在关心频段内,倍频器的变频增益为-1dbˉ3db;倍频器的基次谐波抑制比hr1在31dbc以上,三次谐波抑制比hr3在38dbc以上,四次谐波抑制比hr4在28dbc以上。很明显,改进后的倍频器的变频增益几乎没有什么变化,但是谐波抑制比却得到了极大的改善,尤其体现在基次谐波抑制比上。

59.为了便于比较,将两者的基次谐波放在一起进行对比,如图8所示。在关心频段内,基次谐波抑制比至少提高了5db,甚至在中心频率5.5ghz左右,基次谐波抑制比提高了

15db。

60.两级倍频器级联后得到的四倍频的谐波抑制比分别受到两级倍频器谐波抑制比的影响,因此第一级倍频器谐波抑制的改善也间接提高了四倍频器的谐波抑制比。

61.在这个二倍频四倍频复用的倍频器系统中,即便是第一级倍频器并联支路不引入移相器等移相单元,也需要微带线或者共面波导将其连通,因此移相器的引入没有占用额外的面积。

62.本发明旨在通过两个电路结构互相作用,在关心频段信号矢量合成,达到降低基次谐波抑制的作用,在倍频电路中是一个非常有意义的创新。本发明不仅适用于二倍频四倍频复用系统,对于单独的二倍频电路仍然适用,亦可通过并联支路的方式提高二倍频电路的谐波抑制比,具体实现方式可参照第一级电路。

63.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到根据上述实施例的方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端设备(可以是手机,计算机,服务器,或者网络设备等)执行本发明各个实施例所述的方法。

64.在本实施例中还提供了一种输出倍频信号的装置,该装置用于实现上述实施例及优选实施方式,已经进行过说明的不再赘述。如以下所使用的,术语“模块”可以实现预定功能的软件和/或硬件的组合。尽管以下实施例所描述的装置较佳地以软件来实现,但是硬件,或者软件和硬件的组合的实现也是可能并被构想的。

65.可选地,如图9所示,该装置包括:目标电路902。目标电路中包括并联电路,并联电路的第一电路上设置有倍频器,并联电路的第二电路上设置有相位调整模块,第一电路与目标电路的输入端与输出端连接,第二电路与输入端和输出端保持断开状态,相位调整模块用于将第二电路的相位调整为目标相位,目标相位与第一电路的第一相位的相位差值大于90度,目标电路用于将输入的初始信号倍频为初始信号的倍频信号。

66.本实施例的其他示例请参见上述示例,在此不再赘述。

67.本发明的实施例还提供了一种计算机可读存储介质,该计算机可读存储介质中存储有计算机程序,其中,该计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

68.在一个示例性实施例中,上述计算机可读存储介质可以包括但不限于:u盘、只读存储器(read-only memory,简称为rom)、随机存取存储器(random access memory,简称为ram)、移动硬盘、磁碟或者光盘等各种可以存储计算机程序的介质。

69.本发明的实施例还提供了一种电子装置,包括存储器和处理器,该存储器中存储有计算机程序,该处理器被设置为运行计算机程序以执行上述任一项方法实施例中的步骤。

70.在一个示例性实施例中,上述电子装置还可以包括传输设备以及输入输出设备,其中,该传输设备和上述处理器连接,该输入输出设备和上述处理器连接。

71.本实施例中的具体示例可以参考上述实施例及示例性实施方式中所描述的示例,本实施例在此不再赘述。

72.显然,本领域的技术人员应该明白,上述的本发明的各模块或各步骤可以用通用的计算装置来实现,它们可以集中在单个的计算装置上,或者分布在多个计算装置所组成的网络上,它们可以用计算装置可执行的程序代码来实现,从而,可以将它们存储在存储装置中由计算装置来执行,并且在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤,或者将它们分别制作成各个集成电路模块,或者将它们中的多个模块或步骤制作成单个集成电路模块来实现。这样,本发明不限制于任何特定的硬件和软件结合。

73.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。