sgt-mosfet半导体器件的制备方法

技术领域

1.本发明涉及功率半导体技术领域,更具体地,涉及一种sgt-mosfet半导体器件的制备方法。

背景技术:

2.sgt-mosfet是一种新型的功率半导体器件,具有传统深沟槽mosfet的低导通损耗的优点,同时具有更加低的开关损耗。sgt-mosfet作为开关器件应用于新能源电动车、新型光伏发电、节能家电等领域的电机驱动系统、逆变器系统及电源管理系统,是核心功率控制部件。

3.传统sgt-mosfet的沟槽结构由两个多晶硅部分组成:上半部分是控制栅,下半部分是屏蔽栅,所述屏蔽栅位于所述控制栅下方,目前采用多晶硅间隔离氧化层(inter poly oxide,ipo)实现所述屏蔽栅与所述控制栅之间的隔离,对于现有的sgt器件(尤其是高压sgt器件)而言,对于电耦合(charge couple)结构,为了实现沟槽底部的电荷平衡(charge balance)并降低sgt器件的单位面积的导通电阻,需要对沟槽的深度以及沟槽内的氧化层的厚度有着严格的要求。

4.然而,由于受到现有工艺的限制,很难对沟槽的深度及沟槽内的氧化层的厚度进行优化,无法保证sgt器件中沟槽底部的电荷平衡,使得sgt器件的单位面积的导通电阻较大。受现有技术方法所形成的ipo层的膜厚不稳定,相邻深沟槽内的ipo的厚度就可能有1000埃至2000埃的膜厚差异,从而影响sgt-mosfet的沟道长度;同时,过薄的ipo层容易导致短路,造成器件的失效。如果ipo层沿着不平整的屏蔽栅top的形貌生长,不平整的ipo界面导致刻蚀药液的堆积,影响器件性能,同时也会进一步在器件栅的沉积过程中,使得其底部出现尖角,影响器件的可靠性。

技术实现要素:

5.本发明的目的在于克服现有技术存在的上述缺陷,提供一种sgt-mosfet半导体器件的制备方法。

6.为实现上述目的,本发明提供一种sgt-mosfet半导体器件的制备方法,其特征在于,包括:

7.提供半导体衬底,所述半导体衬底具有深沟槽,所述深沟槽具有第一沟槽区以及第二沟槽区,所述第二沟槽区与所述第一沟槽区相连且位于所述第一沟槽区上方;

8.在所述深沟槽的侧壁和底部形成第一介质层;

9.在所述第一沟槽区的第一介质层上形成栅结构,所述栅结构填充所述第一沟槽区;

10.在所述栅结构上形成的第一氧化层;

11.在所述第二沟槽区的侧壁和底部形成多晶硅层,所述多晶硅层包括位于所述第二沟槽区侧壁的第一介质层表面的侧壁多晶硅层,以及位于所述第一氧化层表面的底面多晶

硅层,所述底面多晶硅层的厚度厚于所述侧壁多晶硅层的厚度;

12.氧化所述侧壁多晶硅层和所述底面多晶硅层,直至所述侧壁多晶硅层全部氧化成初始第二氧化层,所述底面多晶硅层部分氧化成所述初始第二氧化层;

13.去除所述初始第二氧化层以及位于所述第二沟槽区的侧壁的第一介质层,直至暴露出所述第一氧化层上的剩余的底面多晶硅层;

14.氧化所述剩余的底面多晶硅层,在所述第一氧化层上形成第二氧化层。

15.优选地,所述半导体衬底为硅衬底,所述第一介质层的材料为氧化硅,所述第一介质层的形成工艺包括热氧化法,所述第一介质层的厚度为1000埃~6000埃。

16.优选地,所述深沟槽的沟槽深度为1um~7um,所述深沟槽的开口尺寸为0.8um~2.5um。

17.优选地,所述第一沟槽区的第一沟槽深度为所述沟槽深度的1/3~1/2。

18.优选地,在所述栅结构上形成的第一氧化层后,所述第二沟槽区的深宽比增大1.5~2倍。

19.优选地,所述侧壁多晶硅层的的厚度为500埃~2000埃,所述多晶硅层的形成工艺包括低温沉积工艺,所述低温沉积工艺的沉积温度小于530℃。

20.优选地,所述初始第二氧化层的厚度为800埃~2400埃。

21.优选地,采用热氧化法氧化所述剩余的底面多晶硅层,所述第二氧化层还形成在所述第二沟槽区的侧壁。

22.优选地,所述第二氧化层的厚度为250埃~1000埃。

23.优选地,氧化所述侧壁多晶硅层和所述底面多晶硅层,直至所述侧壁多晶硅层全部氧化成初始第二氧化层,所述底面多晶硅层部分氧化成所述初始第二氧化层之后,还包括:在所述初始第二氧化层上形成填充所述第二沟槽区的第二介质层;去除所述初始第二氧化层以及位于所述第二沟槽区的侧壁的第一介质层时,还去除所述第二介质层。

24.从上述技术方案可以看出,本发明提供一种sgt-mosfet半导体器件的制备方法,在深沟槽的侧壁和底部形成第一介质层;在第一沟槽区的第一介质层上形成栅结构;在所述栅结构上形成的第一氧化层;在第二沟槽区的侧壁和底部形成多晶硅层,所述多晶硅层包括位于所述第二沟槽区侧壁的第一介质层表面的侧壁多晶硅层,以及位于所述第一氧化层表面的底面多晶硅层,所述底面多晶硅层的厚度厚于所述侧壁多晶硅层的厚度。通过位于所述第一氧化层表面的底面多晶硅层后续形成第二氧化层,弥补了第一氧化层的膜厚不均匀的情况。氧化所述侧壁多晶硅层和所述底面多晶硅层,直至所述侧壁多晶硅层全部氧化成初始第二氧化层,所述底面多晶硅层部分氧化成所述初始第二氧化层;去除所述初始第二氧化层以及位于所述第二沟槽区的侧壁的第一介质层,直至暴露出所述第一氧化层上的剩余的底面多晶硅层,所述剩余的底面多晶硅层作为刻蚀停止层,避免第一氧化层被腐蚀而影响器件性能。氧化所述剩余的底面多晶硅层,在所述第一氧化层上形成第二氧化层,通过氧化所述剩余的底面多晶硅层,从而避免出现第一氧化层过薄,以及保证第一栅极结构上的氧化层厚度的一致性,具有显著的意义。

附图说明

25.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现

有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

26.图1至图8示出了根据本发明实施例的一种sgt-mosfet半导体器件的制备方法的工艺步骤示意图。

具体实施方式

27.为使本发明的内容更加清楚易懂,以下结合说明书附图,对本发明的内容作进一步说明。当然本发明并不局限于该具体实施例,本领域内的技术人员所熟知的一般替换也涵盖在本发明的保护范围内。

28.需要说明的是,在下述的具体实施方式中,在详述本发明的实施方式时,为了清楚地表示本发明的结构以便于说明,特对附图中的结构不依照一般比例绘图,并进行了局部放大、变形及简化处理,因此,应避免以此作为对本发明的限定来加以理解。

29.为使本发明的目的、技术方案和优点更加清楚,下面结合附图,对本发明的具体实施方式作进一步的详细说明,图1至图7示出了根据本发明实施例的一种sgt-mosfet半导体器件的制备方法的工艺步骤示意图。

30.如图1所示,提供半导体衬底100,所述半导体衬底100具有深沟槽101。提供半导体衬底100,所述半导体衬底100具有深沟槽101,所述深沟槽101具有第一沟槽区(未图示)以及第二沟槽区(未图示),所述第二沟槽区与所述第一沟槽区相连且位于所述第一沟槽区上方。

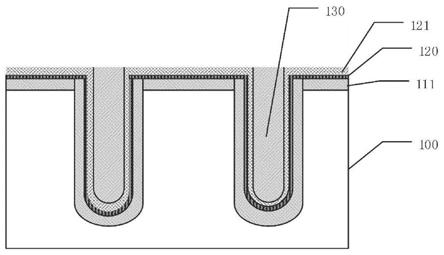

31.所述半导体衬底100可以为si衬底、ge衬底、sige衬底、sic衬底、soi(绝缘体上硅,silicon on insulator)衬底或goi(绝缘体上锗,germanium on insulator)衬底等,还可以为包括其他元素半导体或化合物半导体的衬底,例如玻璃衬底或iii-v族化合物衬底(例如氮化镓衬底或砷化镓衬底等),还可以为叠层结构,例如si/sige等,还可以其他外延结构,例如sgoi(绝缘体上锗硅)等。在一实施例中,所述半导体衬底100为硅衬底,在所述硅衬底上沉积外延层,然后图形化所述外延层,在所述外延层内形成深沟槽101。在本实施例中,所述半导体衬底100为硅衬底,通过光刻工艺在所述半导体衬底100上形成图形化光刻胶层,所述图形化光刻胶层定义出所述深沟槽101的位置和形状,以所述图形化光刻胶层为掩模,刻蚀所述半导体衬底100,在所述半导体衬底100内形成若干个深沟槽101,再去除所述图形化光刻胶层。在本实施例中,所述深沟槽的沟槽深度为1um~7um,所述深沟槽的开口尺寸为0.8um~2.5um。在一实施例中,形成所述深沟槽101后,还圆角化所述深沟槽101底部的角,形成u型深沟槽101。所述深沟槽101的截面形状还包括矩形、正方形所组成群组中的一种或矩形、正方形、正“v”形及反“v”形中的两种以上。由于该工艺在本领域中是已知的,所以这里不再重复细节。所述第一沟槽区的第一沟槽深度为所述沟槽101深度的1/3~1/2,所述第一沟槽深度决定了后续形成的第一栅结构的高度。

32.如图2所示,在所述深沟槽101的侧壁和底部形成第一介质层110。

33.经过标准表面清洁后,在所述半导体衬底100上通过使用本领域已知的技术形成所述第一介质层110,这些技术包括但不限于使用物理沉积、例如低压化学气相沉积(lpcvd)的化学沉积、例如等离子体增强化学汽相沉积(pecvd)等离子体沉积、物理化学沉

积的组合沉积、脉冲激光沉积、热蒸发、电子束蒸发、例如直流溅射和射频溅射的溅射沉积、原子排列(atomic alignment)、湿法氧化,干法氧化,化学溶液氧化等领域内熟知的技术形成所述第一介质层110。在本实施例中,所述第一介质层110的形成工艺为热氧化法,所述半导体衬底100为硅衬底,通过热氧化法在所述半导体衬底100上形成所述第一介质层110,后续再采用cmp去除位于所述半导体衬底100表面的第一介质层110,所述第一介质层110的材料为氧化硅,通过热氧化法在所述深沟槽101的侧壁和底部形成一层致密的氧化硅,所述第一介质层110的厚度为1000埃~6000埃。

34.如图3所示,在所述第一沟槽区的第一介质层110上形成栅结构111,所述栅结构111填充所述第一沟槽区。

35.在本实施例中,通过在所述第一介质层110上沉积多晶硅并回刻,在所述第一介质层110上形成填充所述第一沟槽区的所述栅结构111。

36.如图4所示,在所述栅结构111上形成的第一氧化层120。

37.在本实施例中,所述栅结构111的材料为多晶硅,通过直接热氧化所述栅结构111,在所述栅结构111上形成所述第一氧化层120。由于该工艺在本领域中是已知的,所以这里不再重复细节。在本实施例中,通过热氧化形成所述第一氧化层120,由于所述第二深沟槽的侧壁已经被沉积第一介质层110,因此,在所述栅结构111上形成的第一氧化层120后,所述第二沟槽区的深宽比相对于未填充所述第一氧化层120的第二沟槽区的深宽比增大1.5~2倍。在另一实施例中,所述第一氧化层120的形成工艺包括化学气相沉积。

38.如图5所示,在所述第二沟槽区的侧壁和底部形成多晶硅层130,所述多晶硅层130包括位于所述第二沟槽区侧壁的第一介质层110表面的侧壁多晶硅层131,以及位于所述第一氧化层120表面的底面多晶硅层132,所述底面多晶硅层132的厚度厚于所述侧壁多晶硅层131的厚度。

39.在本实施例中,所述侧壁多晶硅层131的厚度为500埃~1500埃。所述侧壁多晶硅层131的的厚度为500埃~2000埃,所述侧壁多晶硅层131的形成工艺包括低温沉积工艺,所述低温沉积工艺的沉积温度小于530℃。所述多晶硅层130为不掺杂的多晶硅,采用低温沉积的工艺形成所述不掺杂的多晶硅,从而不会影响所述半导体衬底100上的epi的浓度分布,由此避免了影响器件的bv性能。在所述深沟槽101的侧壁和底部形成第一介质层110,并在所述栅结构111上形成的第一氧化层120后,所述第二沟槽区的深宽比增大,所述多晶硅层130受所述第二沟槽区侧壁的影响,位于所述第二沟槽区底部的所述多晶硅层130的顶面由于沉积挤压而抬升,由此形成的位于所述第一氧化层120表面的底面多晶硅层132,所述底面多晶硅层132的厚度厚于所述侧壁多晶硅层131的厚度,在另一实施例中,位于所述第一沟槽区底部的底面多晶硅层132的膜厚较位于所述第一沟槽区侧壁的侧壁多晶硅层131的膜厚大500埃。通过位于所述第一氧化层120表面的底面多晶硅层132后续形成第二氧化层,弥补了第一氧化层120的膜厚不均匀的情况,使得在第一沟槽区后续形成表面平整的ipo膜。

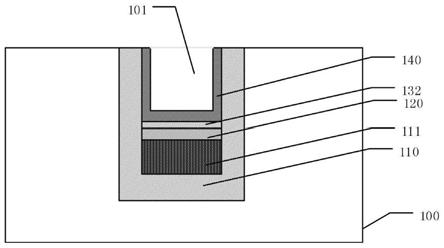

40.如图6所示,氧化所述侧壁多晶硅层131和所述底面多晶硅层132,直至所述侧壁多晶硅层131全部氧化成初始第二氧化层140,所述底面多晶硅层132部分氧化成所述初始第二氧化层140。

41.所述初始第二氧化层140的厚度为800埃~2400埃。在本实施例中,所述初始第二

氧化层140的形成工艺为热氧化法,通过直接热氧化所述多晶硅层130,所述侧壁多晶硅层131全部氧化成初始第二氧化层140,所述底面多晶硅层132部分氧化成所述初始第二氧化层140。在另一实施例中,氧化所述侧壁多晶硅层131和所述底面多晶硅层132,直至所述侧壁多晶硅层131全部氧化成所述初始第二氧化层140,所述底面多晶硅层132部分氧化成所述初始第二氧化层140之后,在所述初始第二氧化层140上形成填充所述第二沟槽区的第二介质层(未图示)。采用高密度等离子体沉积工艺形成所述第二介质层,由于所述第二沟槽区的结构形貌以及高密度等离子体沉积工艺的特性,会出现所述第二沟槽区的开口处封闭较快,而所述第二沟槽区内空洞的现象,所述第二介质层包含平坦状的填充部以及位于所述第二沟槽区的尖峰状的凸起部,所述尖峰状的凸起部也是导致现有技术出现ipo膜厚不均升至膜缺失的原因之一。

42.如图7所示,去除所述初始第二氧化层(未图示)以及位于所述第二沟槽区的侧壁的第一介质层110,直至暴露出所述第一氧化层120上的剩余的底面多晶硅层132。

43.在本实施例中,采用各向同性的湿法刻蚀工艺去除所述初始第二氧化层140以及位于所述第二沟槽区的侧壁的第一介质层110。在另一实施例中,去除所述初始第二氧化层140以及位于所述第二沟槽区的侧壁的第一介质层110时,还去除所述第二介质层,具体的,先采用各向同性的湿法刻蚀回刻所述第二介质层,由于所述第二介质层的特有形貌,所述尖峰状的凸起部会较容易被优先去除,然后再采用各向同性的湿法刻蚀工艺去除所述初始第二氧化层140以及位于所述第二沟槽区的侧壁的第一介质层110。由于所述底面多晶硅层132部分氧化成所述初始第二氧化层140,因此,剩余的未被氧化的所述底面多晶硅层132作为刻蚀停止层,避免所述栅结构111上形成的第一氧化层120被腐蚀而影响器件性能。

44.如图8所示,氧化所述剩余的底面多晶硅层(未图示),在所述第一氧化层120上形成第二氧化层141。

45.在本实施例中,通过热氧化法氧化所述剩余的底面多晶硅层,所述热氧化法还氧化所述第二沟槽区的侧壁,所述第二氧化层141还形成在所述第二沟槽区的侧壁。所述剩余的底面多晶硅层132一方面作为去除所述初始第二氧化层140以及位于所述第二沟槽区的侧壁的第一介质层110过程中的刻蚀停止层,另一方面通过氧化所述剩余的底面多晶硅层132,从而避免出现ipo过薄的现象,同时也保证ipo膜厚的一致性。所述第二氧化层141的厚度为250埃~1000埃。所述第二氧化层141还形成在所述第二沟槽区的侧壁。

46.基于本发明的方法制备的sgt-mosfet半导体器件的制备方法,在深沟槽的侧壁和底部形成第一介质层;在第一沟槽区的第一介质层上形成栅结构;在所述栅结构上形成的第一氧化层;在第二沟槽区的侧壁和底部形成多晶硅层,所述多晶硅层包括位于所述第二沟槽区侧壁的第一介质层表面的侧壁多晶硅层,以及位于所述第一氧化层表面的底面多晶硅层,所述底面多晶硅层的厚度厚于所述侧壁多晶硅层的厚度。通过位于所述第一氧化层表面的底面多晶硅层后续形成第二氧化层,弥补了第一氧化层的膜厚不均匀的情况。氧化所述侧壁多晶硅层和所述底面多晶硅层,直至所述侧壁多晶硅层全部氧化成初始第二氧化层,所述底面多晶硅层部分氧化成所述初始第二氧化层;去除所述初始第二氧化层以及位于所述第二沟槽区的侧壁的第一介质层,直至暴露出所述第一氧化层上的剩余的底面多晶硅层,所述剩余的底面多晶硅层作为刻蚀停止层,避免第一氧化层被腐蚀而影响器件性能。氧化所述剩余的底面多晶硅层,在所述第一氧化层上形成第二氧化层,通过氧化所述剩余

的底面多晶硅层,从而避免出现第一氧化层过薄,以及保证第一栅极结构上的氧化层厚度的一致性,具有显著的意义。

47.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。