技术特征:

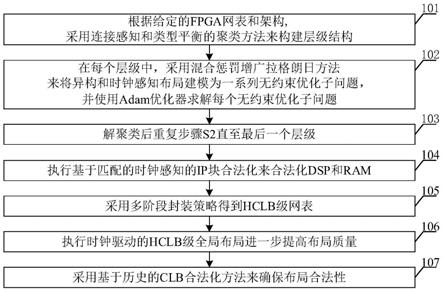

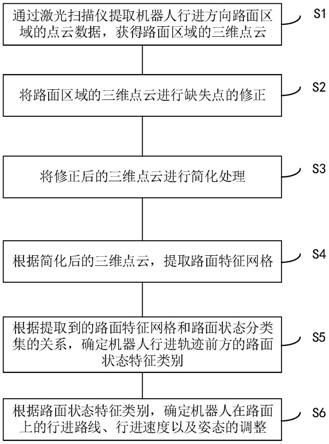

1.一种考虑时钟约束的超大规模异构fpga布局方法,其特征在于:包括以下步骤:步骤s1,根据给定的fpga网表和架构,采用连接感知和类型平衡的聚类方法来构建层级结构;步骤s2,在每个层级中,采用混合惩罚增广拉格朗日方法来将异构和时钟感知布局建模为一系列无约束优化子问题,并使用adam优化器求解每个无约束优化子问题;步骤s3,解聚类后重复步骤s2直至最后一个层级;步骤s4,执行基于匹配的时钟感知的ip块合法化来合法化dsp和ram;步骤s5,采用多阶段封装策略得到hclb级网表;步骤s6,执行时钟驱动的hclb级全局布局进一步提高布局质量;步骤s7,采用基于历史的clb合法化方法来确保布局合法性。2.根据权利要求1所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:所述步骤s1中两个模块/聚类b

i

和b

j

的聚类分数s

ctc

(b

i

,b

j

)定义为其中η1和η2是两个常数,内部连接项w

int

、外部连接项w

ext

和类型平衡项w

bal

的具体定义如下:如下:如下:其中n

ext

是包含b

i

或b

j

但没有两者的网络数量,而n

bal

是b

i

和b

j

中的lut和ff数量之差。3.根据权利要求1所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:所述步骤s2中需解约束优化问题其中t={ff,lut,dsp,ram}是模块类型的集合,是近似于半周线长的平滑线长函数,f(x,y)是时钟围栏区域cost函数f(x

i

,y

i

)=f

h

(x

i

) fv(y

i

)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(6)其中f

h

(x

i

)和fv(y

i

)分别给出了水平和垂直围栏区域cost,而f

h

(x

i

)定义为:其中x

il

和x

ir

分别是模块i的围栏区域的左右边界坐标,类似地可获得竖直方向cost函

数fv(y

i

);是计算bin b中类型为t∈t的模块的总面积的平滑密度函数,而是bin b中类型为t∈t的模块的最大允许面积;将式(5)转为无约束优化问题其中λ

c

是围栏区域函数的罚参数,λ

t

是类型t的模块密度函数的罚参数,是类型t的模块在bin b的拉格朗日乘子,ω

t

是类型t的模块的光滑因子参数;使用如下方法来解该问题上式中,o

t

是模块类型t的溢出率,用于衡量模块分布的均匀性;ω0和ω1是两个常数,并且ω

t

将随着模块的分散而减少。4.根据权利要求2所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:所述步骤s5中多阶段封装分为如下步骤:(1)基于2引脚线网的lut-ff配对;(2)基于多引脚网络的lut-ff配对;(3)时钟感知ble封装;(4)亲和感知hclb封装;(5)距离驱动的hclb封装;(6)hclb封装后处理。5.根据权利要求4所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:步骤(2)中,首先将每一个lut或ff作为一个顶点,一一检查多引脚网络;如果多引脚网络e中一个lutb

i

和一个ffb

j

之间的曼哈顿距离小于fpga的两个单元,那么b

i

和b

j

之间存在边,边权重设为其中|e|是网络连接到的模块数;在遍历所有多引脚网络后,构建了一个加权图;通过解决最大加权匹配问题,可进一步形成一些lut-ff对,以减少外部线网的线长。6.根据权利要求4所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:步骤(3)中,将一个lut-ff对、单个lut或单个ff均视为一个ble,然后,使用基于最佳选择聚类的时钟感知ble打包算法,以形成对hclb封装友好的ble;合并两个bles b

i

和b

j

的亲和度函数定义为:其中e

i,j

是连接b

i

和b

j

的网络的集合,|e|是网络e中的模块数量,dist(b

i

,b

j

)是b

i

和b

j

之间的距离,而k1是定义的参数。7.根据权利要求6所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:步骤(4)中,此阶段应用最佳选择聚类来封装连接在相同线网上的hclb;合并两个hclbb

i

和b

j

的亲和度函数定义为:其中area(b

i

)表示b

i

的面积,此步骤需确保每个hclb最多包含四个bles,这四个bles共享相同的clk和sr信号,并且最多有两个不同的ce信号;此外,还禁止长距离hclb合并。8.根据权利要求4所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:步骤(5)中,将两个hclb之间的曼哈顿距离作为亲和度,并应用最佳选择聚类来封装hclb。9.根据权利要求4所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:步骤(6)中,如果hclb的数量仍然超过目标hclb站点容量,将进行此步骤,以进一步减少最终的hclb数量;首先构造一个加权图,其中一个顶点代表一个hclb,一条边代表一个合法的hclb合并;两个hclb之间的边权重是包含它们的网络数量;通过迭代执行基于最大加权匹配的hclb打包并逐渐放宽最大距离约束,直到满足hclb站点容量约束。10.根据权利要求1所述的考虑时钟约束的超大规模异构fpga布局方法,其特征在于:所述步骤s7中,通过迭代增加各溢出站点的cost与溢出半列的时钟cost,并将对应模块移除重新放置在cost最小的位置上,每经过一定的周期数增加一次搜索半径,最终将所有模块放置到合法位置。

技术总结

本发明公开了一种考虑时钟约束的超大规模异构FPGA布局方法,包括以下步骤:(1)根据给定的网表和架构,采用连接感知和类型平衡的聚类方法来构建层级结构;(2)在每个层级中,采用混合惩罚增广拉格朗日方法将异构和时钟感知的布局建模为一系列无约束优化子问题,并执行Adam求解每个子问题;(3)执行基于匹配的时钟感知的IP块合法化;(4)采用多阶段封装策略得到HCLB级网表;(5)执行时钟驱动的全局布局提高布局质量;(6)最后采用基于历史的CLB合法化方法来确保布局合法性。本发明能够在满足时钟约束的前提下,快速得到高质量的布局结果,有效减少布线线长,可满足目前超大规模FPGA布局阶段的需求。阶段的需求。阶段的需求。

技术研发人员:朱自然 梅扬杰

受保护的技术使用者:东南大学

技术研发日:2022.02.07

技术公布日:2022/5/17

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。