技术特征:

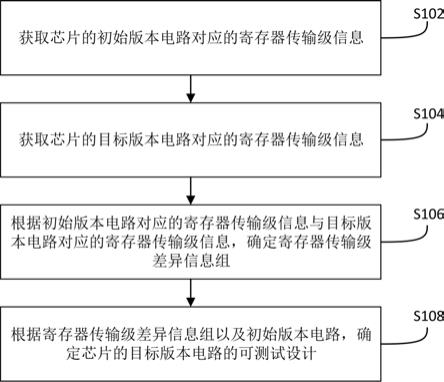

1.一种芯片可测试设计的确定方法,其特征在于,所述方法包括:获取芯片的初始版本电路对应的寄存器传输级信息;获取所述芯片的目标版本电路对应的寄存器传输级信息;根据所述初始版本电路对应的寄存器传输级信息与所述目标版本电路对应的寄存器传输级信息,确定寄存器传输级差异信息组;根据所述寄存器传输级差异信息组以及所述初始版本电路,确定所述芯片的目标版本电路的可测试设计。2.根据权利要求1所述的芯片可测试设计的确定方法,其特征在于,所述根据所述寄存器传输级差异信息组,确定所述目标版本电路的可测试设计的步骤包括:根据所述寄存器传输级差异信息组,修改所述初始版本电路中的扫描寄存器,得到所述目标版本电路中的扫描链模块;根据预设协议文件以及所述目标版本电路中的扫描链模块,确定目标版本电路的扫描链模块的电路信号;根据所述目标版本电路中的扫描链模块以及所述目标版本电路的扫描链模块的电路信号,确定所述芯片的目标版本电路的可测试设计。3.根据权利要求2所述的芯片可测试设计的确定方法,其特征在于,所述目标版本电路的扫描链模块的电路信号包括:所述目标版本电路的扫描链模块中每条扫描链的时钟信号组、所述目标版本电路的扫描链模块的使能信号以及所述目标版本电路的扫描链模块中新插入的每个扫描寄存器对应的重置信号。4.根据权利要求3所述的芯片可测试设计的确定方法,其特征在于,目标版本电路的扫描链模块中每条扫描链的时钟信号组的确定方法为:将所述目标版本电路的扫描链模块中所有扫描链分为若干条子扫描链;根据预设协议文件,确定芯片的锁存单元存储的电平信息;根据所述电平信息,确定所述子扫描链对应的时钟信号;根据所述子扫描链对应的时钟信号,确定所述目标版本电路的扫描链模块中每条扫描链的时钟信号组。5.根据权利要求3所述的芯片可测试设计的确定方法,其特征在于,所述目标版本电路的扫描链模块中新插入的每个扫描寄存器对应的重置信号的确定方法为:获取所述目标版本电路的扫描链模块中新插入的每个扫描寄存器对应的寄存器接入的功能重置信号;将所述功能重置信号引入选择器,得到选择信号;根据所述选择信号与所述预设协议文件,确定所述目标版本电路的扫描链模块中新插入的每个扫描寄存器对应的重置信号。6.根据权利要求2所述的芯片可测试设计的确定方法,其特征在于,所述寄存器传输级差异信息组携带有待插入的扫描寄存器信息;所述根据所述寄存器传输级差异信息组,修改所述初始版本电路中扫描寄存器,得到所述目标版本电路中的扫描链模块的步骤为:根据所述待插入的扫描寄存器信息,确定待插入的扫描寄存器;

获取所述初始版本电路的扫描链模块中扫描链的数量信息以及触发器信息;将所述扫描链模块划分为若干个组合逻辑内核;获取每个所述组合逻辑内核唯一对应的测试向量集;根据所述测试向量集确定每个所述组合逻辑内核的链周期;根据所述扫描链的数量信息、所述触发器信息以及每个所述组合逻辑内核的链周期,确定链周期特值;根据所述链周期特值,确定所述待插入的扫描寄存器的插入位置;在所述插入位置插入所述待插入的扫描寄存器,得到所述目标版本电路的扫描链模块。7.根据权利要求6所述的芯片可测试设计的确定方法,其特征在于,所述触发器信息包括触发器的总数量、充当驱动器的扫描寄存器所包括的触发器数量以及充当接收器的扫描寄存器所包括的触发器数量;所述组合逻辑内核的链周期相对于对应的测试向量集元素个数单调递增;所述触发器的总数量与所述扫描链的总数量之商不小于所述组合逻辑内核的链周期;对于任意相关的两组所述组合逻辑内核,均有如下条件:;其中:t

a

表示第一组合逻辑内核的链周期;t

b

表示第二组合逻辑内核的链周期;sl表示两组所述组合逻辑内核中扫描寄存器的总数量;rd(a,b)表示所述第一组合逻辑内核中为同时充当驱动器与接收器而在所述第二组合逻辑内核中只充当驱动器的扫描寄存器所包括的触发器数量;rr(a,b)表示所述第一组合逻辑内核中为同时充当驱动器与接收器而在所述第二组合逻辑内核中只充当接收器的扫描寄存器所包括的触发器数量;c

b

表示所述第二组合逻辑内核中包含的同时充当驱动器与接收器的扫描寄存器包括的触发器数量;n表示所述初始版本电路的扫描链模块中扫描链的数量。8.根据权利要求1所述的芯片可测试设计的确定方法,其特征在于,所述芯片可测试设计的确定方法还包括:获取所述芯片的初始版本电路的门级网表;根据所述寄存器传输级差异信息组以及所述初始版本电路,确定所述目标版本电路的功能设计;根据所述目标版本电路的功能设计、所述目标版本电路的可测试设计以及所述初始版本电路的门级网表,确定所述芯片对应的目标版本电路。9.一种计算机设备,其特征在于,包括存储器和处理器,所述存储器中存储有计算机程序,所述计算机程序被所述处理器执行时,使得所述处理器执行权利要求1至8中任一项权利要求所述芯片可测试设计的确定方法的步骤。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时,使得所述处理器执行权利要求1至8中任一项权利要求所述芯片可测试设计的确定方法的步骤。

技术总结

本申请适用于计算机技术领域,提供了一种芯片可测试设计的确定方法、设备和存储介质,所述方法包括:获取芯片的初始版本电路对应的寄存器传输级信息;获取所述芯片的目标版本电路对应的寄存器传输级信息;根据所述初始版本电路对应的寄存器传输级信息与所述目标版本电路对应的寄存器传输级信息,确定寄存器传输级差异信息组;根据所述寄存器传输级差异信息组以及所述初始版本电路,确定所述芯片的目标版本电路的可测试设计。本申请通过对前后版本电路的寄存器传输级信息的比对获得电路差异,并以之为准自动修改生成目标版本可测试设计,相较于人工更新可测试设计效率与准确率更高,有效降低了芯片版本更新的时间成本、简化了芯片版本更新的操作。片版本更新的操作。片版本更新的操作。

技术研发人员:魏星 刁屹 林德基

受保护的技术使用者:奇捷科技(深圳)有限公司

技术研发日:2022.04.02

技术公布日:2022/5/16

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。