1.本技术实施例涉及计算机领域,尤其涉及一种内存管理管理方法及混合内存管理单元。

背景技术:

2.高带宽存储器(high bandwidth memory,hbm)是一种利用硅穿孔(through silicon vias,tsv)技术实现同步动态随机存取内存(synchronous dynamic random-access memory,sdram)三维(three dimensional,3d)堆叠的计算机内存,相对当前sdram具有更高密度、更大带宽、更低时延的特性。储存级记忆体(storage class memory,scm)一种新型存储介质,兼具sdram的低时延,和闪存(flash)的持久存储特性。

3.虚拟内存技术是计算机内存管理的一种技术,中央处理器(central processing unit,cpu)的内存管理单元(memory management unit,mmu)和操作系统(operating system,os)通过物理内存与外置存储的换入换出实现虚拟内存,从而扩展了物理内存空间。

4.随着增强现实(augmented reality,ar)、虚拟现实(virtual realit,vr)、物联网(internet of things,iot)以及流计算技术的发展,只有纯内存计算才能够满足这类应用场景的需求,此类场景下cpu访问存储器的过程中数百个微秒的波动都会造成部分关键应用在实时性上无法满足处理的时延需求。现有技术中,由于scm完全异于当前存储介质的特性,目前的cpu内存系统无法完全支持并发挥scm的全部特性,而传统的cpu访问存储器的流程中,cpu通过mmu访问物理内存的访问时延较大,特别是当物理内存中不存在所需的页面数据时,mmu会发生缺页异常,需要在操作系统上进行缺页中断例程调度,缺页中断例程把页面数据从外置盘加载到内存,此过程开销较大,导致存储器的访问时延大。

技术实现要素:

5.本技术实施例提供了一种内存管理方法以及混合内存管理单元,用于降低cpu对存储器的访问时延。

6.本技术实施例第一方面提供了一种内存管理方法,应用于处理器的内存子系统,该内存子系统包括混合内存管理单元hmmu、储存级存储器scm的控制器和动态存储器。在内存管理过程中,hmmu获取处理器cpu发送的存储器访问请求,该存储器访问请求指示hmmu访问动态存储器或scm的物理地址,hmmu基于该存储器访问请求查询页表确定存储访问请求所访问的动态存储器或scm中的物理地址,hmmu访问该物理地址。

7.从以上技术方案可以看出,本技术实施例提供了一种新的内存子系统,该内存子系统中的混合内存管理单元hmmu可以支持访问内置于cpu的动态存储器和储存级记忆体scm,由于动态存储器以及scm的高带宽、低时延特性和本技术实施例提供的内存子系统对动态存储器和scm的适配,降低了cpu访问物理内存的时延。

8.在一种可能的实施方式中,本技术实施例中的动态存储器可以是高带宽存储器

hbm,也可以是动态随机存储器dram,不做限定。

9.结合第一方面,本技术实施例第一方面的第一种实施方式中,scm的控制器、动态存储器与处理器封装在同一块芯片。

10.结合第一方面、第一方面的第一种实施方式,本技术实施例第一方面的第二种实施方式中scm的控制器与动态存储器均内置于处理器。

11.本技术实施例中内存子系统支持访问外置于处理器的scm,而该scm的控制器、hbm以及hmmu与处理封装在同一块芯片上,或者内置于处理器,提升了芯片集成度。

12.结合第一方面、第一方面的第一种至第二种实施方式,本技术实施例第一方面的第三种实施方式中,hmmu的页表可以提供不同粒度的地址映射,地址映射是指逻辑地址与物理地址之间的映射关系,地址映射的粒度可以由物理页的页大小确定,物理页的页大小可以是64字节或者64字节的整数倍,此处不做限定。例如当物理页的页大小为64字节时,对应hmmu的页表的最后一级页表的位数为6位。

13.本技术实施例中页表可以提供多种不同页大小的物理页,提升了物理内存在不同数据粒度场景下的内存利用率,该物理内存可以是hbm、dram或scm,具体不做限定。

14.结合第一方面、第一方面的第一种至第三种实施方式,本技术实施例第一方面的第四种实施方式中,如果hmmu访问的物理地址为scm中的物理地址,hmmu通过scm的控制器访问scm的物理地址。

15.结合第一方面、第一方面的第一种至第四种实施方式,本技术实施例第一方面的第五种实施方式中,hmmu访问所述物理地址为scm中的物理地址,hmmu将物理地址中的数据加载到动态存储器,hmmu访问动态存储器中的该数据。

16.本技术实施例中当hmmu访问的物理地址不是动态存储器的物理地址而是scm的物理地址,hmmu将scm中的数据加载到动态存储器,由于scm相比磁盘具有极短的存取时间,降低了数据从外存加载到动态存储器的时延。

17.结合第一方面、第一方面的第一种至第五种实施方式,本技术实施例第一方面的第六种实施方式中,处理器为中央处理单元cpu。

18.结合第一方面、第一方面的第一种至第六种实施方式,本技术实施例第一方面的第七种实施方式中,页表的页表项包括物理地址、内存类型和有效位。

19.本技术实施例中页表项中新增了内存类型的属性位,hmmu查询快表和页表时可以根据页表项中内存类型判断逻辑地址对应的物理地址位于动态存储器还是scm,提升页表查询速度,减少了内存访问时延。

20.本技术实施例第二方面提供了一种混合内存管理单元hmmu,该hmmu应用于内存子系统,内存子系统包括该hmmu之外,还包括储存级存储器scm的控制器和高带宽存储器动态存储器,hmmu包括:

21.获取单元,用于获取处理器发送的存储器访问请求,存储器访问请求用于访问位于scm或所述动态存储器中的地址。

22.查询单元,用于基于存储器访问请求查询页表确定存储器访问请求所访问的scm或动态存储器中的地址。

23.访问单元,用于访问地址。

24.在一种可能的实施方式中,动态存储器可以是高带宽存储器hbm,也可以是动态随

机存储器dram,不做限定。

25.结合第二方面,本技术实施例第二方面的第一种实施方式中,scm的控制器与动态存储器以及处理器封装在同一块芯片。

26.结合第二方面、第二方面的第一种实施方式,本技术实施例第二方面的第二种实施方式中,scm的控制器与动态存储器均内置于处理器。

27.结合第二方面、第二方面的第一种至第二种实施方式,本技术实施例第二方面的第三种实施方式中,页表可以提供不同粒度的地址映射。

28.结合第二方面、第二方面的第一种至第三种实施方式,本技术实施例第二方面的第四种实施方式中,访问单元具体用于:

29.如果物理地址为scm中的物理地址,访问单元通过scm的控制器访问物理地址。

30.结合第二方面、第二方面的第一种至第四种实施方式,本技术实施例第二方面的第五月种实施方式中,访问单元具体用于:

31.如果物理地址为scm中的物理地址,访问单元将物理地址中的数据加载到动态存储器,访问单元访问动态存储器中的数据。

32.结合第二方面、第二方面的第一种至第五种实施方式,本技术实施例第二方面的第六月种实施方式中,处理器为中央处理单元cpu。

33.结合第二方面、第二方面的第一种至第六种实施方式,本技术实施例第二方面的第七月种实施方式中,页表的页表项包括所述物理地址、内存类型和有效位。

34.本技术实施例第三方面提供了一种芯片,该芯片包含内存子系统,内存系统包括混合内存管理单元hmmu、储存级记忆体scm控制器和动态存储器,其中,hmmu用于执行上述第一方面的方法。

35.本技术实施例第四方面提供了一种电子设备,该电子设备包含上述第三方面的芯片。

36.本技术实施例第五方面提供了一种芯片模组,该芯片模组包含上述第三方面的芯片。

37.本技术实施例第六方面提供了一种集成电路,所述集成电路应用于内存子系统中,所述内存子系统包括混合内存管理单元hmmu、储存级记忆体scm的控制器和动态存储器,其中,所述集成电路用于实现所述hmmu所执行的第一方面的方法。

附图说明

38.图1为本技术实施例提供的一种处理器系统结构示意图;

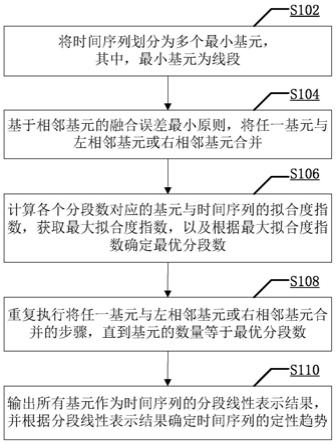

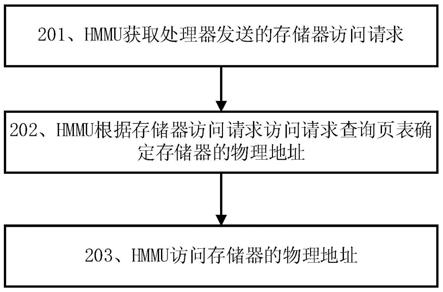

39.图2为本技术实施例提供的一种内存管理方法示意图;

40.图3为本技术实施例提供的一种内存访问流程示意图;

41.图4为本技术实施例提供的一种页表结构示意图;

42.图5为本技术实施例提供的另一种页表结构示意图;

43.图6为本技术实施例提供的一种混合内存管理单元结构示意图;

44.图7为本技术实施例提供的一种电子设备结构示意图。

具体实施方式

45.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。

46.在本技术实施例中,“示例性的”或者“例如”等词用于表示作例子、例证或说明。本技术实施例中被描述为“示例性的”或者“例如”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用“示例性的”或者“例如”等词旨在以具体方式呈现相关概念。

47.以下,对本技术中的部分用语进行解释说明,以便于本领域技术人员理解。

48.高带宽存储器(high bandwidth memory,hbm)是一种利用硅穿孔(through silicon vias,tsv)技术实现同步动态随机存取内存(synchronous dynamic random-access memory,sdram)三维(three dimensional,3d)堆叠的计算机内存,相对当前sdram具有更高密度、更大带宽、更低时延的特性,适用于高存储器带宽需求的应用场合,像是图形处理器、网络交换及转发设备等。

49.储存级记忆体(storage class memory,scm)一种一种同时结合传统储存装置与存储器特性的新型存储技术,兼具sdram的低时延,和闪存(flash)的持久存储特性。按照所构成的材料,一般分为变相存储器(phase change memory,pcm)、磁阻式随机存储器(magnetoresistive random access memory,mram)、电阻式随机存储器(resistive random access memory,reram)、铁电随机存储器(ferroelectric random access memory,feram)、碳纳米管随机存储器(nanotube random access memory,nram)。

50.虚拟内存是计算机系统内存管理的一种技术。它使得应用程序认为它拥有连续的可用的完整的地址空间,而实际上,它通常是被分隔成多个物理内存碎片,还有部分暂时存储在外部磁盘存储器上,在需要时进行数据交换。目前,大多数操作系统都使用了虚拟内存,例如,windows的“虚拟内存”,linux的“交换空间”等。

51.页表是一种特殊的数据结构,放在系统空间的页表区,存放逻辑页与物理页的对应关系,即地址映射,在页表中,一个页码与其对应的物理页码称之为一个页表项。

52.逻辑地址为cpu所生成的地址,cpu产生的逻辑地址分为页码和页内偏移量,页码包含每个页在物理内存中的基址,用来作为页表的索引。页内偏移量与基址相结合,用来确定内存的物理地址。所有逻辑地址的集合成为逻辑地址空间。

53.物理地址为内存的实际地址,与逻辑地址相对应的内存中所有物理地址的集合为物理地址空间。

54.为更好的理解本技术实施例所提供的内存管理方法,以下首先结合图1所示,对本技术所示方法所应用的处理器内存系统进行说明。

55.请参阅图1,图1为本技术实施例提供的一种处理器系统的结构示意图。本技术实施例中的处理器单元包括处理器和内存子系统,内存子系统中集成了混合内存管理单元hmmu、hbm和scm控制器,其中hbm包含hbm的控制器和hbm内存介质。hmmu、hbm和scm控制器采用半导体集成分装工艺与处理器封装在同一块芯片上。示例性的,本发明实施例以处理器为cpu作为示例进行描述。处理器还可以是图形处理单元(graphics processing unit,gpu)等其他处理器,本发明实施例对此不作限定。

56.本技术实施例中的scm外置于cpu芯片,可通过内存总线或串行总线连接cpu单元,

cpu发起的load/store指令可以无需软件驱动通过scm的控制器直接访问scm上的存储内容,scm的控制器内置于cpu芯片。内存子系统内置的scm控制器以及外置scm,提供了相对dram更大的容量以及相对硬盘更低时延的扩展内存空间。

57.本技术实施例中内置于cpu的hbm存储器可以是hbm、hbm2或hbm2e,不做限定,hbm的内存空间可以直接被映射到页表上,hbm与scm的数据交换通过hmmu管理实现。cpu内置的hbm存储器提供基于页表的存储访问以及数据的高速缓存,hbm提供了相对dram更低的时延和更大的带宽。

58.本技术实施例提供的内存子系统中,hmmu是本技术实施例提供的一种新型的内存管理单元,hmmu实现了把hbm、scm进行统一页表管理。hmmu的主要功能包括查找和维护转移后备缓冲区(translation lookaside buffer,tlb)、页表查找的逻辑实现以及页表的页表项维护逻辑实现。在hmmu页表查找的逻辑实现过程中,hmmu采用多级页表通过进程的逻辑地址查找对应的物理地址,物理地址可以是hbm的地址空间,也可以是scm的地址空间,hmmu的页表的最后一级也表的位数可以是6至12位,对应的最后一级页表的页大小为64字节或者64字节的整数倍,因此,hmmu管理的页表可以提供不同粒度的地址映射,即用多种管理粒度进行逻辑地址到物理地址的映射管理,例如,hmmu可以用最小64字节的管理粒度进行逻辑地址到物理地址的映射。

59.在另一个处理器系统的结构示例中,内存子系统包含了hmmu、动态随机存储器dram和scm控制器,其中dram包含dram的控制器和dram内存介质。hmmu、dram和scm控制器采用半导体集成分装工艺与处理器封装在同一块芯片上。

60.本发明实施例中的处理器系统以及内存子系统可以为芯片或芯片模组等,可以应用于各种电子设备中。电子设备可以是存储设备、服务器等,本发明实施例对此不作限定。本发明实施例中的处理器系统以及内存子系统可以由集成电路实现。

61.请参阅图2,图2为本技术实施例提供的内存管理方法的一个实施例示意图。

62.201、hmmu获取处理器发送的储存器访问请求。

63.hmmu获取处理器发送的存储器访问请求,该访问请求中包含应用或进程的逻辑地址,逻辑地址为应用或进程侧所看到的内存地址,hmmu通过对该逻辑地址计算或变换得到存储器中的实际有效地址,即存储器的物理地址。本发明实施例中,以处理器为cpu作为示例进行说明。

64.应用于图1所示的cpu系统,本技术实施例中的存储器访问请求可以是对内置于cpu系统的hbm的访问请求,也可以是外置的scm的访问请求,具体此处不做限定。基于图1所示的实施例,存储器的物理地址可以为hbm的物理地址或scm的物理地址。

65.202、hmmu根据存储器访问请求查询页表确定存储器的物理地址。

66.以下结合图3对本技术实施例中的内存子系统下hmmu根据存储器访问请求查询页表确定存储器的物理地址的过程进行介绍。

67.请参阅图3,图3示出了本技术实施例中hmmu访问hbm和scm流程示意图。hmmu根据cpu发出的逻辑地址查询快表和页表,快表为存放在高速缓冲存储器的部分页表,作为页表的缓存,位于hmmu,快表作用页表相似,但提高了查询效率。该逻辑地址被分成为两个部分,包括页码以及页内偏移量,页码被用于查询上述快表和页表,快表在cpu实现中可以是tlb。

68.hmmu根据cpu发出的逻辑地址优先查询tlb快表,hmmu查询tlb快表结果分为以下

两种情况:

69.1、如果tlb快表命中逻辑地址的页码,则说明要访问的页表项在tlb快表中存储在副本,hmmu确定出该页码对应的物理页码,即图3中的页框码。物理页码与逻辑地址的原页内偏移量拼接成物理地址,如果该物理地址在hbm的物理地址空间,hmmu可以通过该物理地址访问内置于cpu的hbm,如果该物理地址在scm的物理地址空间,hmmu可以通过该物理地址访问外置于cpu的scm。

70.2、如果tlb快表未命中逻辑地址的页码,则hmmu在操作系统维护的页表中查找逻辑地址的页码对应的页表项,相应的,hmmu确定出该页码对应的物理页码,物理页码与逻辑地址的原页内偏移量拼接成物理地址,该物理地址为hmmu所要访问存储器的物理地址。

71.可以理解的是,hmmu在页表中找到相应的页表之后,同时将该页表项加载到tlb快表的空项中,完成tlb快表的更新,以方便hmmu以后可能的再次查询。当tlb快表已满的时候,hmmu按照一定算法对tlb快表中旧的页表项替换。

72.本技术实施例中的tlb快表存放了页表中常用的页表项,由于tlb快表位于hmmu,而页表位于hbm,查询快表耗时较短,若tlb命中逻辑地址的页码,hmmu访问逻辑地址仅需要一次访问内存,引入tlb快表机制体提升了hmmu的逻辑地址查询速度。

73.下面对本技术实施例中hmmu所查询的页表进行介绍,本技术实施例中所提供的页表可以是多级页表,具体此处不做限定。以下分别对本技术实施例中的四级页表和三级页表进行介绍:

74.请参阅图4,图4是本技术实施例中的一种页表结构示意图,该页表结构具有四级页表,最后一级页表的位数是6位,相应的,最后一级页表的的页大小为64字节。图4所示页表结构中,逻辑地址为36位,“bit26~35”的内容为一级页表,“bit16~25”的内容二级页表,“bit6~15”的内容为三级页表,“bit0~5”的内容为四级页表。由于图4所示页表的最后一级页大小为64字节,在该页表机制下,hmmu可以用64字节的管理粒度进行虚拟地址空间到物理地址空间的映射管理。

75.图4所示的四级页表机制可以用多种小数据粒度的场景,例如,联机事务处理过程(on-line transaction processing,oltp)、数据库、图计算、稀疏矩阵或物联网(internet of things,iot)应用,具体不做限定。

76.本技术实施例中hmmu用64字节粒度管理虚拟地址空间到物理地址空间的映射,减少了虚拟内存所占用的物理内存空间开销,节约了物理内存资源。

77.请参阅图5,图5是本技术实施例中的另一种页表结构示意图,该页表结构具有四级页表,最后一级页表的位数是12位,相应的,最后一级页表的的页大小为4096字节。图5所示页表结构中,逻辑地址为32位,“bit22~31”的内容为一级页表,“bit12~21”的内容为二级页表,“bit0~11”的内容为三级页表,在该页表机制下,hmmu可以用64字节的管理粒度进行虚拟地址空间到物理地址空间的映射管理。

78.可以理解的是,本技术实施例多种页表中除了上述页表之外,页表中的最后一级页表的位数可以是6至12位,相应的,最后一级页表的的页大小可以是64字节、128字节、256字节、512字节、1024字节、2048字节或4096字节。

79.本技术实施例中hmmu可以多种页表大小粒度管理虚拟地址空间到物理地址空间的映射,提升了物理内存在不同数据粒度场景下的内存利用率。

80.本技术实施例提供一种新的页表项结构,下面本技术实施例中的页表的页表项结构进行介绍:

81.请参阅表1,表1是本技术实施例中页表的最后一级页表项结构,页表项中“physical memory address”为最后一级页表项指向的物理内存地址,“memory type”为最后一级页表项所指向的物理内存类型,物理内存类型包括hbm、dram或scm,不做限定。“valide”为有效位,指示对应的页表项当前是否有对应的物理内存。物理内存地址、内存类型和有效位都可以称作页表项的属性位。

82.本技术实施例在最后一级页表的表项结构中增加了内存类型的属性位,使得hmmu在进行页表查询时能够判断出页码对应的物理页码为哪一种类型的内存介质上,hmmu查找逻辑地址,读取到对应的的页表项之后,根据跟页表项的属性位分别发起对hbm控制器或scm控制器的数据读写操作指令,数据的读写可以在不用调度软件的情况下一次性在hmmu中完成。

[0083][0084]

表1

[0085]

203、hmmu访问存储器的物理地址。

[0086]

hmmu根据步骤202确定的物理地址对存储器进行访问,下面结合图3对本技术实施例中hmmu访问存储器的物理地址进行介绍:

[0087]

hmmu查询页表的页表项时,可以根据最后一级页表的页表项中的物理内存类型判断所要访问存储器,hmmu访问存储器包括以下几种情况:

[0088]

1、hmmu查询tlb快表或页表确定逻辑地址页码对应的目标页表项,如果该目标页表项的内存类型为hbm,并且该目标页表项中的有效位指示物理地址有效,则hmmu通过hbm控制器直接访问hbm。

[0089]

具体的,hmmu将逻辑地址的页码转换为物理页码,物理页码与逻辑地址的原页内偏移量拼接成物理地址,hmmu通过该物理地址访问内置于cpu的hbm。

[0090]

2、hmmu查询tlb快表或页表确定逻辑地址页码对应的目标页表项,如果该目标页表项的内存类型为scm,并且该目标页表项中的有效位指示物理地址有效,则hmmu通过scm控制器直接访问scm。同时,hmmu可以将位于scm内存范围内的该物理地址对应的数据加载到hbm,具体的,hmmu根据最近最少使用(least recently used,lru)算法将hbm的数据换出到scm,hmmu将页表所命中的scm的物理地址的数据换入到hbm,hmmu将加载后的hbm内存起始地址和内存类型更新到该逻辑地址的页码所对应的页表项,方便hmmu下一次查询页表,并直接发起对hbm的访问。

[0091]

本技术实施例中的访问存储器包括了对存储器数据的读取和写入。

[0092]

本技术实施例中提供的内存系统通过hmmu的内存管理逻辑,在当需要读取的数据未缓存在hbm上时,hmmu在硬件逻辑层完全实现页表查询,以及通过scm控制器实现了cpu对scm访问,由于hmmu可以在不陷入缺页异常的的情况下直接实现scm的读取,消除了由于缺页异常导致的软件上下文切换及软件异常例程的运行,减少了cpu内存系统读取外部内存的时延。

[0093]

本技术实施例还提供一种与图1所示的硬件机制对应的内存子系统,下面对该内存子系统的功能进行介绍,该内存子系统的功能包括:

[0094]

1、维护更新各进程页表,具体的,在进程需要分配或删除物理页面时,例如某一个物理页面在hbm中分配,则把最后一级页表对应页表项的内存类型的属性位设置成hbm,又例如对应的物理页面在scm上,则把最后一级页表对应页表项的内存类型属性位设置成scm,最后页表项的有效位置位成有效。

[0095]

2、进程切换时各进程基地址寄存器的加载,具体的,在需要进行进程切换时把对应待换入的进程的页表基地址加载到页表基地址寄存器。

[0096]

下面对本技术实施例中混合内存管理单元hmmu进行描述:

[0097]

请参阅图6,图6为本技术实施例中混合内存管理单元600的一个示意图,本技术中混合内存管理单元600的一个实施例包括:

[0098]

获取单元601,用于获取处理器发送的存储器访问请求,存储访问请求用于访问位于scm或动态存储器中的物理地址;

[0099]

查询单元602,用于基于存储器访问请求查询页表确定存储访问请求所访问的scm或动态存储器中的物理地址;

[0100]

访问单元603,用于访问所述物理地址。

[0101]

在本技术一些可选的实施例中,scm的控制器与动态存储器与处理器封装在同一块芯片,或者scm的控制器与动态存储器均内置于处理器。

[0102]

在本技术一些可选的实施例中,动态随机存储器可以是hbm。

[0103]

在本技术一些可选的实施例中,页表可以提供不同粒度的地址映射。

[0104]

在本技术一些可选的实施例中,访问单元603具体用于:

[0105]

当物理地址为scm中的物理地址,访问单元603通过scm的控制器访问物理地址。

[0106]

在本技术一些可选的实施例中,访问单元603具体用于:

[0107]

当所述物理地址为scm中的物理地址,访问单元603将物理地址中的数据加载到动态存储器,所述访问单元访问动态存储器中的数据。

[0108]

在本技术一些可选的实施例中,处理器为中央处理单元cpu。

[0109]

在本技术一些可选的实施例中,页表的页表项包括物理地址、内存类型和有效位。

[0110]

本实施例中,混合内存管理单元hmmu可以执行前述图2所示实施例中hmmu所执行的操作,具体此处不再赘述。

[0111]

本技术实施例提供的一种电子设备,电子设备包含处理器系统。示例性的,电子设备结构示意图如图7所示,包含中央处理器701和内存子系统702。进一步的,电子设备还可以包括一个或一个以上电源,一个或一个以上有线或无线网络接口,一个或一个以上输入输出接口等。

[0112]

所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的系统,装置和单元的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

[0113]

在本技术所提供的几个实施例中,应该理解到,所揭露的系统,装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0114]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0115]

另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

[0116]

所述集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。