技术特征:

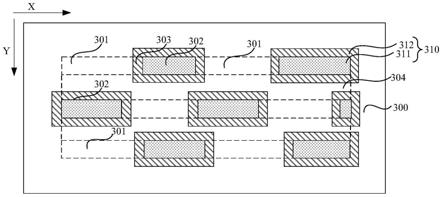

1.一种半导体结构的形成方法,其特征在于,包括:提供基底,所述基底包括沿第一方向交错排布的第一沟槽区和第二沟槽区,以及位于所述第一沟槽区和所述第二沟槽区之间的隔离区;在所述基底上形成图形化的阻挡层,所述阻挡层覆盖所述第二沟槽区和隔离区,暴露所述第一沟槽区;形成图形化的第一掩膜层,所述第一掩膜层暴露所述第一沟槽区的基底,以及所述第二沟槽区和所述隔离区的阻挡层;以所述阻挡层和所述第一掩膜层为掩膜,刻蚀所述基底,形成第一沟槽;形成覆盖所述第一沟槽和所述隔离区,且暴露所述第二沟槽区的第二掩膜层;以所述第一掩膜层和所述第二掩膜层为掩膜,刻蚀所述基底,形成第二沟槽。2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述在所述基底上形成图形化的阻挡层,包括:形成图形化的阻挡层主体,所述阻挡层主体覆盖所述第二沟槽区,暴露所述隔离区和所述第一沟槽区;在所述阻挡层主体的侧壁形成阻挡层侧墙,所述阻挡层侧墙覆盖所述隔离区;其中,以所述阻挡层主体和所述阻挡层侧墙作为所述阻挡层。3.如权利要求2所述的半导体结构的形成方法,其特征在于,所述形成覆盖所述第一沟槽和所述隔离区,且暴露所述第二沟槽区的第二掩膜层,包括:形成覆盖所述第一沟槽的牺牲层;去除所述第一掩膜层暴露的所述阻挡层主体,以所述牺牲层和剩余的阻挡层为第二掩膜层。4.如权利要求2所述的半导体结构的形成方法,其特征在于,所述形成图形化的阻挡层主体,包括:形成覆盖所述基底表面的阻挡主体材料层;在所述阻挡主体材料层上形成图形化的光刻胶层;以所述光刻胶层为掩膜,图形化所述阻挡主体材料层,形成所述阻挡层主体。5.如权利要求2所述的半导体结构的形成方法,其特征在于,所述在所述阻挡层主体的侧壁形成阻挡层侧墙,包括:形成保形覆盖所述阻挡层主体的侧墙材料层;去除所述阻挡层主体顶部和所述基底顶部的侧墙材料层,以剩余的侧墙材料层作为所述阻挡层侧墙。6.如权利要求3所述的半导体结构的形成方法,其特征在于,在形成覆盖所述第一沟槽的牺牲层的步骤中,所述牺牲层的顶面不高于所述阻挡层的顶面。7.如权利要求1所述的半导体结构的形成方法,其特征在于,所述形成第二沟槽之后,还包括:去除所述第一掩膜层和所述第二掩膜层,暴露所述基底和位于所述基底上的第一沟槽和第二沟槽;在所述第一沟槽和第二沟槽内形成导电互连层,所述导电互连层的顶面不高于所述基底表面。

8.如权利要求1所述的半导体结构的形成方法,其特征在于,所述基底包括多个并行的沿第一方向交错排布的第一沟槽区和第二沟槽区,其中,在第二方向上,第一沟槽区和第二沟槽区交错排布,所述第二方向与所述第一方向垂直。9.如权利要求8所述的半导体结构的形成方法,其特征在于,在第一方向上,以位于同一行的第一沟槽区、第二沟槽区和隔离区为一个沟槽区,其中,相邻沟槽区之间还包括沟槽隔断区,在所述形成图形化的阻挡层的步骤中,所述阻挡层还覆盖所述基底的至少部分沟槽隔断区。10.如权利要求1所述的半导体结构的形成方法,其特征在于,所述形成覆盖所述第一沟槽和所述隔离区,且暴露所述第二沟槽区的第二掩膜层,包括:形成覆盖所述基底形成有所述阻挡层一侧的第二掩膜材料层;图形化所述第二掩膜材料层,形成第二掩膜层。11.如权利要求10所述的半导体结构的形成方法,其特征在于,所述以所述第二掩膜层和第一掩膜层为掩膜,刻蚀所述基底,形成第二沟槽,包括:以所述第二掩膜层和所述第一掩膜层为掩膜,刻蚀所述阻挡层,形成暴露所述基底的第二初始沟槽;刻蚀所述第二初始沟槽暴露的基底,形成第二沟槽。12.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一掩膜层的材料为氮化钛、氮化铝或三氧化二铝中的一种或多种,或者,所述第一掩膜层的材料为碳化硅、氮化硅、氮氧化硅或硅中的一种或多种。13.如权利要求2所述的半导体结构的形成方法,其特征在于,所述阻挡层主体的材料为氮化钛、氮化铝或三氧化二铝中的一种或多种;所述阻挡层侧墙的材料为氮化钛、氮化铝、三氧化二铝、碳化硅、氮化硅、氮氧化硅或硅中的一种或多种;并且,所述阻挡层主体的材料不同于所述阻挡层侧墙的材料。14.如权利要求3所述的半导体结构的形成方法,其特征在于,所述牺牲层的材料为不定型硅、不定型碳、有机介电层或旋涂碳层中的一种或多种。

技术总结

本发明实施例提供了一种半导体结构的形成方法,所述方法包括:提供基底;在所述基底上形成图形化的阻挡层,所述阻挡层覆盖所述第二沟槽区和隔离区,暴露所述第一沟槽区;形成图形化的第一掩膜层,所述第一掩膜层暴露所述第一沟槽区的基底,以及所述第二沟槽区和所述隔离区的阻挡层;以所述阻挡层和所述第一掩膜层为掩膜,刻蚀所述基底,形成第一沟槽;形成覆盖所述第一沟槽和所述隔离区,且暴露所述第二沟槽区的第二掩膜层;以所述第一掩膜层和所述第二掩膜层为掩膜,刻蚀所述基底,形成第二沟槽。所述方法降低了半导体结构形成工艺的工艺复杂度和工艺精度。杂度和工艺精度。杂度和工艺精度。

技术研发人员:徐锦心 王楠

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:2020.10.26

技术公布日:2022/5/16

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。