一种易拓展的ai运算加速装置

技术领域

1.本实用新型涉及边缘计算设备领域,特别涉及一种易拓展的ai运算加速装置。

背景技术:

2.目前市场上边缘计算的主控存在ai算力偏弱的特点,如果需要在终端做一些ai的模型训练或者推理,则需要通过通信设备把数据上传到云端,然后再进行训练或者推理。

3.云计算方案中,终端的场景有很多,如果终端的设备数量大,全部都通过通信链路把数据传给云端运算,那么通信链路的带宽压力会非常大,而且延迟比较高,在某些极端的环境中通信链路可能中断,则边缘设备丧失ai计算能力。

技术实现要素:

4.本实用新型的目的在于克服现有技术的缺点与不足,提供一种易拓展的ai运算加速装置。

5.本实用新型的目的通过以下的技术方案实现:

6.一种易拓展的ai运算加速装置,包括处理器,还包括分别与处理器连接的存储器、内存、温度检测单元、加密单元以及复位单元;所述处理器通过金手指连接器与底板通信以及获取电源;所述金手指连接器采用标准的204pin的ddr3的连接器。

7.所述易拓展的ai运算加速装置,还包括集成电源管理电路(pmic);所述金手指连接器的引脚pin184、引脚pin186直接与插口j2连接;所述插口j2用于烧录集成电源管理电路的固件。

8.所述金手指连接器的引脚pin183、引脚pin185直接连接到拨码开关sw1的同一侧,其中引脚pin185对应的pad_bootmode_0的另一侧通过电阻r125上拉到1.8v,引脚pin183对应的pad_bootmode_1的另一侧通过电阻r124下拉到地,用于控制所述易拓展的ai运算加速装置的启动方式。

9.所述金手指连接器的引脚pin170、引脚pin172与调试单元u43的a端连接,通过调试单元u43把1.8v的信号转成b端3.3v的信号,b端分别与电阻r247和电阻r248连接,把转换出来的3.3v串口信号接到连接器con21;调试单元u43的1.8v电源和3.3v电源分别通过电容c271和电容c272滤波,调试单元u43的使能引脚通过电阻r246上拉到1.8v,使b端一直能转换a端的信号。

10.所述处理器型号是寒武纪mlu220,存储器型号是ncemasld-32g,内存型号是mt53d1024m32d4dt-046wt:d,温度检测单元使用的芯片是sgm452,加密单元使用的芯片是rjgt102wdt6,复位单元使用的芯片是sgm811-xxka4。

11.所述底板通过dc-dc降压芯片u38降压给ai运算加速装置供电:12v~26v电源通过电容c218、电容c211滤波后给dc-dc供电,dc-dc降压芯片u38的en引脚通过电阻r203、电阻r207和电容c214拉高使3.3v一直有输出;dc-dc降压芯片u38的mode引脚通过电阻r208和电阻r209控制模式;dc-dc降压芯片u38的bst引脚通过电容c216连接sw引脚形成dcdc内部的

自举电路;dc-dc降压芯片u38的sw引脚接到电感l9,通过电容c57~c60滤波后给ai运算加速装置提供稳定的5v电压,通过电阻r119、电阻r200、电阻r204把输出电压反馈给dc-dc降压芯片u38的fb引脚,而电阻r201、电阻r206、电容c210给电压反馈电路提供斜坡补偿;dc-dc降压芯片u38输出的5v电压经过电容c98~c111滤波后再输入到ai运算加速装置。

12.所述dc-dc降压芯片u38的型号为mp8756gd。

13.所述复位单元包括复位开关sw3、静电管d29,所述复位开关sw3一端接地,另一端经过静电管d29后通过电阻r232上拉到3.3v然后经过电容c260滤波接入复位芯片u42,3.3v电源经过电容c264滤波后给复位芯片u42供电,复位芯片u42的引脚reset通过串联给提供复位信号。

14.所述存储器包括存储控制器u1b和sfc芯片以及emmc芯片u5a;

15.所述存储控制器u1b的引脚bg5、be5、bf4、bh2、bj3、be3分别接到电阻r141~r145、电阻r147,然后分别连接到芯片u4的引脚pin4、pin6、pin5、pin2、pin7、pin1,在芯片u4的引脚pin1~pin3分别接到电阻r151~r153上拉到1.8v,芯片u4的引脚pin8接到电容c436进行电源滤波,存储控制器u1b的引脚aa5接到电阻r148~r149。所述存储控制器u1b的引脚pad_emmc_rstn、pad_emmc_cmd、pad_emmc_data0~pad_emmcdata7分别接到emmc芯片u5a的引脚rst_n、cmd、data0~data7,并且通过电阻r156~r165上拉到1.8v,存储控制器u1b的引脚pad_emmc_strobe通过电阻r167下拉到地,然后再经过电阻r166接入emmc芯片u5a的引脚rclk/ds,存储控制器u1b的引脚pad_emmc_clk通过电阻r146接入emmc芯片u5a的引脚clk,emmc芯片u5a的引脚e6、f5、j10、k9接入电容c437~c439形成3.3v的滤波电路,emmc芯片u5a的引脚c6、m4、n4、p3、p5接入电容c440~c442形成1.8v的滤波电路,电容c443~c444对emmc芯片u5a的引脚c2内部进行滤波。

16.所述内存包括内存控制器u1f、u1g,以及内存芯片u13a、u13b、u15a、u15b;所述内存控制器u1f的引脚ddr1_caa0~ddr1_caa5连接内存芯片u13a的引脚ca0_a~ca0b、ddr1_cab0~ddr1_cab5连接内存芯片u13b的引脚ca0_b~ca5_b,内存控制器u1f的引脚ddr1_dq0~ddr1_dq15连接内存芯片u13a的引脚dq0_a~dq15_a,内存控制器u1f的引脚ddr1_dq16~ddr1_dq31连接到内存芯片u13b的引脚dq0_b~dq15_b;所述内存控制器u1f的引脚ddr1_ckea0、ddr1_ckea1、ddr1_clka_c、ddr1_clka_t、ddr1_csa_n0、ddr1_csa_n1、ddr1_dqs_c0、ddr1_dqs_t0、ddr1_dqs_c1、ddr1_dqs_t1、ddr1_dm0、ddr1_dm1分别接到内存芯片u13a的引脚cke0_a、nc_7、ck_c_a、ck_t_a、cs0_a、nc_6、dqs0_c_a、dqs0_t_a、dqs1_c_a、dqs1_t_a、dmi0_a、dmi1_a,以上信号一一对应,没有交换线序;所述内存控制器u1f的引脚ddr1_ckeb0/、ddr1_ckeb1、ddr1_clkb_c、ddr1_clkb_t、ddr1_csb_n0、ddr1_csb_n1、ddr1_dqs_c2、ddr1_dqs_t2、ddr1_dqs_c3、ddr1_dqs_t3、ddr1_dm2、ddr1_dm3、ddr1_memreset_l分别接到内存芯片u13b的引脚cke0_b、nc_9、ck_c_b、ck_t_b、cs0_b、nc_8、dqs0_c_b、dqs0_t_b、dqs1_c_b、dqs1_t_b、dmi0_b、dmi1_b、reset_n,以上信号一一对应,没有交换线序,内存芯片u13a的引脚odt_ca_a通过电阻r4下拉到地,引脚zq0通过电阻r6上拉到引脚vcc_vddq;内存芯片u13b的引脚odt_ca_b通过电阻r3下拉到地,通过电阻r1上拉到引脚vcc_vddq;内存控制器u1g的引脚ddr0_caa0~ddr0_caa5连接内存芯片u15a的引脚ca0_a~ca0b,内存控制器u1g的引脚ddr0_cab0~ddr0_cab5连接内存芯片u15b的引脚ca0_b~ca5_b,内存控制器u1g的引脚ddr0_dq0~ddr0_dq15连接内存芯片u15a的引脚dq0_a~dq15_a,内存控制器u1g

的引脚ddr0_dq16~ddr0_dq31连接到内存芯片u15b的引脚dq0_b~dq15_b;内存控制器u1g的引脚ddr0_ckea0、ddr0_ckea1、ddr0_clka_c、ddr0_clka_t、ddr0_csa_n0、ddr0_csa_n1、ddr0_dqs_c0、ddr0_dqs_t0、ddr0_dqs_c1、ddr0_dqs_t1、ddr0_dm0、ddr0_dm1分别接到内存芯片u15a的引脚cke0_a、nc_7、ck_c_a、ck_t_a、cs0_a、nc_6、dqs0_c_a、dqs0_t_a、dqs1_c_a、dqs1_t_a、dmi0_a、dmi1_a,以上信号一一对应,没有交换线序;内存控制器u1g的引脚ddr0_ckeb0、ddr0_ckeb1、ddr0_clkb_c、ddr0_clkb_t、ddr0_csb_n0、ddr0_csb_n1、ddr0_dqs_c2、ddr0_dqs_t2、ddr0_dqs_c3、ddr0_dqs_t3、ddr0_dm2、ddr0_dm3、ddr0_memreset_l分别接到内存芯片u15b的引脚cke0_b、nc_9、ck_c_b、ck_t_b、cs0_b、nc_8、dqs0_c_b、dqs0_t_b、dqs1_c_b、dqs1_t_b、dmi0_b、dmi1_b、reset_n,以上信号一一对应,没有交换线序;内存芯片u15a的引脚odt_ca_a通过电阻r4下拉到地,引脚zq0通过电阻r6上拉到引脚vcc_vddq,内存芯片u15b的引脚odt_ca_b通过电阻r3下拉到地,通过电阻r1上拉到引脚vcc_vddq;内存控制器u1f、u1g的引脚pad_bcg_ddrpll_1、pad_bcg_ddrpll_0通过连接电阻r19~r22上拉以及下拉。

17.本实用新型与现有技术相比,具有如下优点和有益效果:

18.1、本实用新型将信号都引到金手指中,通过金手指连接器与底板通信以及获取电源。本实用新型尺寸小,集成度高,算力强,国产化程度高,只需要在底板上加简单的外设即可为主控提供强大的算力,加速ai产品落地。

19.2、本发明基于寒武纪mlu220设计的ai智能模组,内置npu算力高达16tops(int8),支持caffe、tensorflow、mxnet等深度学习框架,用户可面向上述编程框架,便捷地在aim16t上开发和部署深度学习应用。同时,寒武纪人工智能开发平台提供了完整的运行时系统和驱动软件,方便系统快速集成。同时,本发明的视频处理性能优越,支持h264、h265、vp8、vp9编解码,解码最大可支持16路1080@30p,编码最大可支持8路1080@30p。在提供上述强悍性能的基础上,功耗典型值控制在13w以内,而且核心板的面积仅仅为6.76x4.5cm。

附图说明

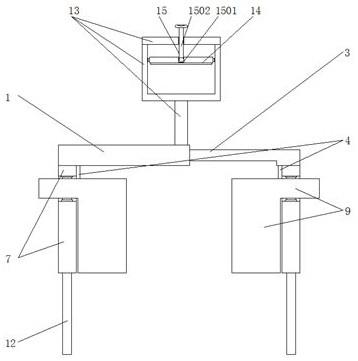

20.图1为本实用新型所述易拓展的ai运算加速装置与主控板(底板)连接的结构示意图。

21.图2-1、2-2、2-3为本实用新型所述dc-dc降压芯片给所述易拓展的ai运算加速装置供电的电路图。

22.图3、4-1、4-2、5为本实用新型所述金手指连接器的部分外围电路图。

23.图6为本实用新型所述复位单元的电路图。

24.图7为本实用新型所述存储控制器的电路图。

25.图8-1为本实用新型所述sfc芯片的电路图。

26.图8-2为本实用新型所述emmc芯片u5a的电路图。

27.图9-1为本实用新型所述内存控制器u1f的电路图。

28.图9-2为本实用新型所述内存控制器u1g的电路图。

29.图10-1为本实用新型所述内存芯片u13a、u13b的电路图。

30.图10-2为本实用新型所述内存芯片u15a、u15b的电路图。

31.图11为本实用新型所述频点设置电路的电路图。

32.图12为本实用新型所述电平转换电路的电路图。

33.图13为本实用新型所述温度检测芯片电路的电路图。

34.图14为本实用新型所述加密芯片电路的电路图。

具体实施方式

35.下面结合实施例及附图对本实用新型作进一步详细的描述,但本实用新型的实施方式不限于此。

36.如图1,一种易拓展的ai运算加速装置,包括处理器,还包括分别与处理器连接的存储器、内存、温度检测单元、加密单元以及复位单元;所述处理器通过金手指连接器与底板通信以及获取电源。

37.如图3,所述金手指连接器采用标准的204pin的ddr3的连接器。标准的204pin的ddr3的连接器包括te的2013289-1。所述金手指连接器的型号是ddr3 sodimm socket 5.2。

38.所述易拓展的ai运算加速装置,还包括集成电源管理电路(pmic);所述金手指连接器的引脚pin184、引脚pin186直接与插口j2连接;所述插口j2用于烧录集成电源管理电路的固件。

39.如图4-1,所述金手指连接器的引脚pin183、引脚pin185直接连接到拨码开关sw1的同一侧,其中引脚pin185对应的pad_bootmode_0的另一侧通过电阻r125上拉到1.8v,引脚pin183对应的pad_bootmode_1的另一侧通过电阻r124下拉到地,用于控制所述易拓展的ai运算加速装置的启动方式。

40.拨码开关sw1和存储器、内存、温度检测单元、加密单元以及复位单元没有连接关系,仅仅用来控制启动方式。

41.如图4-2,所述易拓展的ai运算加速装置内pad_bootmode_0自带下拉,pad_bootmode_1自带上拉,因此所述易拓展的ai运算加速装置不做控制时默认spi启动。

42.如图5,所述金手指连接器的引脚pin170、引脚pin172与调试单元u43的a端连接,通过调试单元u43把1.8v的信号转成b端3.3v的信号,b端分别与电阻r247和电阻r248连接,把转换出来的3.3v串口信号接到连接器con21,用于调试所述易拓展的ai运算加速装置;调试单元u43的1.8v电源和3.3v电源分别通过电容c271和电容c272滤波,调试单元u43的使能引脚通过电阻r246上拉到1.8v,使b端一直能转换a端的信号。

43.调试单元u43的型号为txs0102dctr。

44.连接器con21的型号为con_3001a0-012-3p1。

45.所述处理器型号是寒武纪mlu220,存储器型号是ncemasld-32g,内存型号是mt53d1024m32d4dt-046wt:d,温度检测单元使用的芯片是sgm452,加密单元使用的芯片是rjgt102wdt6,复位单元使用的芯片是sgm811-xxka4。

46.如图2-1、2-2、2-3,所述底板通过dc-dc降压芯片u38降压给ai运算加速装置供电:12v~26v电源通过电容c218、电容c211滤波后给dc-dc供电,dc-dc降压芯片u38的en引脚通过电阻r203、电阻r207和电容c214拉高使3.3v一直有输出;dc-dc降压芯片u38的mode引脚通过电阻r208和电阻r209控制模式;dc-dc降压芯片u38的bst引脚通过电容c216连接sw引脚形成dcdc内部的自举电路;dc-dc降压芯片u38的sw引脚接到电感l9,通过电容c57~c60滤波后给ai运算加速装置提供稳定的5v电压,通过电阻r119、电阻r200、电阻r204把输出电

压反馈给dc-dc降压芯片u38的fb引脚,而电阻r201、电阻r206、电容c210给电压反馈电路提供斜坡补偿;dc-dc降压芯片u38输出的5v电压经过电容c98~c111滤波后再输入到ai运算加速装置。

47.所述dc-dc降压芯片u38的型号为mp8756gd。

48.如图6,所述复位单元包括复位开关sw3、静电管d29,所述复位开关sw3一端接地,另一端经过静电管d29后通过电阻r232上拉到3.3v然后经过电容c260滤波接入复位芯片u42,3.3v电源经过电容c264滤波后给复位芯片u42供电,复位芯片u42的引脚reset通过串联给整个系统提供复位信号,包括本所述易拓展的ai运算加速装置。

49.所述存储器包括存储控制器u1b和sfc芯片(如图8-1)以及emmc芯片u5a(如图8-2);

50.如图7,所述存储控制器u1b的引脚bg5、be5、bf4、bh2、bj3、be3分别接到电阻r141~r145、电阻r147,然后分别连接到芯片u4的引脚pin4、pin6、pin5、pin2、pin7、pin1,在芯片u4的引脚pin1~pin3分别接到电阻r151~r153上拉到1.8v,芯片u4的引脚pin8接到电容c436进行电源滤波,存储控制器u1b的引脚aa5接到电阻r148~r149,选择芯片u4是nand flash还是nor flash,本新型默认u4为nor flash。所述存储控制器u1b的引脚pad_emmc_rstn、pad_emmc_cmd、pad_emmc_data0~pad_emmcdata7分别接到emmc芯片u5a的引脚rst_n、cmd、data0~data7,并且通过电阻r156~r165上拉到1.8v,存储控制器u1b的引脚pad_emmc_strobe通过电阻r167下拉到地,然后再经过电阻r166接入emmc芯片u5a的引脚rclk/ds,存储控制器u1b的引脚pad_emmc_clk通过电阻r146接入emmc芯片u5a的引脚clk,emmc芯片u5a的引脚e6、f5、j10、k9接入电容c437~c439形成3.3v的滤波电路,emmc芯片u5a的引脚c6、m4、n4、p3、p5接入电容c440~c442形成1.8v的滤波电路,电容c443~c444对emmc芯片u5a的引脚c2内部进行滤波。

51.存储控制器u1b的型号为mlu220。

52.芯片u4的型号为mx25u12832fz4i02。

53.所述内存包括内存控制器u1f(如图9-1)、u1g(如图9-2),以及内存芯片u13a、u13b(如图10-1)、u15a、u15b(如图10-2);所述内存控制器u1f的引脚ddr1_caa0~ddr1_caa5连接内存芯片u13a的引脚ca0_a~ca0b、ddr1_cab0~ddr1_cab5连接内存芯片u13b的引脚ca0_b~ca5_b,内存控制器u1f的引脚ddr1_dq0~ddr1_dq15连接内存芯片u13a的引脚dq0_a~dq15_a,内存控制器u1f的引脚ddr1_dq16~ddr1_dq31连接到内存芯片u13b的引脚dq0_b~dq15_b,以上连接为了方便pcb出线,顺序会有所调整,调整结果见图10-1;所述内存控制器u1f的引脚ddr1_ckea0、ddr1_ckea1、ddr1_clka_c、ddr1_clka_t、ddr1_csa_n0、ddr1_csa_n1、ddr1_dqs_c0、ddr1_dqs_t0、ddr1_dqs_c1、ddr1_dqs_t1、ddr1_dm0、ddr1_dm1分别接到内存芯片u13a的引脚cke0_a、nc_7、ck_c_a、ck_t_a、cs0_a、nc_6、dqs0_c_a、dqs0_t_a、dqs1_c_a、dqs1_t_a、dmi0_a、dmi1_a,以上信号一一对应,没有交换线序;所述内存控制器u1f的引脚ddr1_ckeb0/、ddr1_ckeb1、ddr1_clkb_c、ddr1_clkb_t、ddr1_csb_n0、ddr1_csb_n1、ddr1_dqs_c2、ddr1_dqs_t2、ddr1_dqs_c3、ddr1_dqs_t3、ddr1_dm2、ddr1_dm3、ddr1_memreset_l分别接到内存芯片u13b的引脚cke0_b、nc_9、ck_c_b、ck_t_b、cs0_b、nc_8、dqs0_c_b、dqs0_t_b、dqs1_c_b、dqs1_t_b、dmi0_b、dmi1_b、reset_n,以上信号一一对应,没有交换线序,内存芯片u13a的引脚odt_ca_a通过电阻r4下拉到地,引脚zq0通过电阻r6上拉

到引脚vcc_vddq;内存芯片u13b的引脚odt_ca_b通过电阻r3下拉到地,通过电阻r1上拉到引脚vcc_vddq;内存控制器u1g的引脚ddr0_caa0~ddr0_caa5连接内存芯片u15a的引脚ca0_a~ca0b,内存控制器u1g的引脚ddr0_cab0~ddr0_cab5连接内存芯片u15b的引脚ca0_b~ca5_b,内存控制器u1g的引脚ddr0_dq0~ddr0_dq15连接内存芯片u15a的引脚dq0_a~dq15_a,内存控制器u1g的引脚ddr0_dq16~ddr0_dq31连接到内存芯片u15b的引脚dq0_b~dq15_b,以上连接为了方便pcb出线,顺序会有所调整,调整结果见图10-2;内存控制器u1g的引脚ddr0_ckea0、ddr0_ckea1、ddr0_clka_c、ddr0_clka_t、ddr0_csa_n0、ddr0_csa_n1、ddr0_dqs_c0、ddr0_dqs_t0、ddr0_dqs_c1、ddr0_dqs_t1、ddr0_dm0、ddr0_dm1分别接到内存芯片u15a的引脚cke0_a、nc_7、ck_c_a、ck_t_a、cs0_a、nc_6、dqs0_c_a、dqs0_t_a、dqs1_c_a、dqs1_t_a、dmi0_a、dmi1_a,以上信号一一对应,没有交换线序;内存控制器u1g的引脚ddr0_ckeb0、ddr0_ckeb1、ddr0_clkb_c、ddr0_clkb_t、ddr0_csb_n0、ddr0_csb_n1、ddr0_dqs_c2、ddr0_dqs_t2、ddr0_dqs_c3、ddr0_dqs_t3、ddr0_dm2、ddr0_dm3、ddr0_memreset_l分别接到内存芯片u15b的引脚cke0_b、nc_9、ck_c_b、ck_t_b、cs0_b、nc_8、dqs0_c_b、dqs0_t_b、dqs1_c_b、dqs1_t_b、dmi0_b、dmi1_b、reset_n,以上信号一一对应,没有交换线序;内存芯片u15a的引脚odt_ca_a通过电阻r4下拉到地,引脚zq0通过电阻r6上拉到引脚vcc_vddq,内存芯片u15b的引脚odt_ca_b通过电阻r3下拉到地,通过电阻r1上拉到引脚vcc_vddq;内存控制器u1f、u1g的引脚pad_bcg_ddrpll_1、pad_bcg_ddrpll_0通过连接电阻r19~r22上拉以及下拉(如图11),配置锁相环频点,默认设置为00,对应的频点为933mhz。

54.所述温度检测单元包括电平转换电路(如图12)和温度检测芯片电路(如图13);iic信号通过电阻r276、r277上拉到1.8v接入芯片u34,芯片u34的引脚pin4一直通过电阻r2312上拉到1.8v使其一直有效,芯片u34的引脚pin2、pin3通过电阻r279、r280上拉到3.3v实现3.3v的iic信号的转换,芯片u34的引脚pin1、pin8分别通过电容c533、c534接到1.8v、3.3v进行电源滤波;3.3v的iic信号直接接到芯片u35的引脚pin1、pin2,芯片u35的引脚os一直上拉使其一直有效,并通过电阻r282~r284配置芯片u35的iic的地址,芯片u35的引脚pin8通过电容c535与3.3v网络构成滤波电路。

55.所述加密单元包括加密芯片电路(如图14),上述转换后3.3v的iic信号直接接入芯片u36,芯片u36通过电容c305与3.3v网络构成滤波电路,芯片u36的引脚pin3通过电阻r2366给主控提供一个复位信号。

56.所述加密单元与温度检测单元共用同一个电平转换电路。通过上述连接,易拓展的ai运算加速装置可以给任何带pcie3.0的处理器提供高达16t(int8)算力,还支持多块本新型同时使用,非常容易拓展,大大的降低了高算力边缘计算产品的设计难度。

57.而且易拓展的ai运算加速装置还可以给底板提供一组3.3v的电源和一组1.8v的电源,当底板需要用到这两个电压的时候,如果是小电流ic,还可以节省ldo及其外围电路的成本。

58.上述实施例为本实用新型较佳的实施方式,但本实用新型的实施方式并不受上述实施例的限制,其他的任何未背离本实用新型的精神实质与原理下所作的改变、修饰、替代、组合、简化,均应为等效的置换方式,都包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。