1.本公开涉及微电子器件领域。更具体地,本公开涉及微电子器件中的集成电容器。

背景技术:

2.一些微电子器件在高频下进行操作,并使用电容器来调节高频电流。这种电容器应与微电子器件紧密集成以获得更好的性能。然而,电容器需要很大的面积,并且可能会不合需要地增加微电子器件的尺寸。

技术实现要素:

3.本公开介绍了一种微电子器件,其具有带有连接表面的管芯、第一导电支柱和第二导电支柱。这些支柱机械耦合到连接表面。该微电子器件包括电耦合到第一支柱的第一导电延伸头以及电耦合到第二支柱的第二导电延伸头。第一支柱和第二支柱具有相同成分的导电材料,并且第一延伸头和第二延伸头具有相同成分的导电材料。第一延伸头提供微电子器件的凸块垫,并且第二延伸头提供微电子器件的集成电容器的极板的至少一部分。微电子器件通过同时形成第一支柱和第二支柱并且同时形成第一延伸头和第二延伸头来形成。

附图说明

4.图1a至图1g是具有集成电容器的一种示例微电子器件的横截面,其在示例形成方法的各个阶段中描绘。

5.图2a至图2f是具有集成电容器的另一示例微电子器件的横截面,其在另一示例形成方法的各个阶段中描绘。

6.图3a至图3j是具有集成电容器的进一步示例微电子器件的横截面,其在进一步示例形成方法的各个阶段中描绘。

7.图4a至图4g是具有集成电容器的另一示例微电子器件的横截面,其在另一示例形成方法的各个阶段中描绘。

8.图5a至图5c是具有集成电容器的进一步示例微电子器件的横截面,其在进一步示例形成方法的各个阶段中描绘。

具体实施方式

9.参考附图来描述了本公开。这些图不是按比例绘制的,它们仅用于说明本公开。下面参考示例应用来描述本公开的几个方面以用于图示说明。应当理解,阐述了许多具体细节、关系和方法以提供对本公开的理解。本公开不受示出的动作或事件顺序的限制,因为一些动作可能以不同的顺序发生和/或与其他动作或事件同时发生。此外,并非所有示出的动作或事件都是实施根据本公开的方法所必需的。

10.微电子器件具有诸如集成电路、分立半导体器件、微机电系统(mems)器件或微流

体器件的管芯。该管芯具有连接表面。至微电子器件的部件的外部电连接在连接表面处实现。微电子器件包括第一支柱和第二支柱,它们都是导电的,并且机械耦合到连接表面。第一支柱和第二支柱具有相同成分的导电材料。微电子器件包括电耦合到第一支柱的第一延伸头以及电耦合到第二支柱的第二延伸头。第一延伸头和第二延伸头都是导电的,并且具有相同成分的导电材料。第一延伸头提供凸块垫,并且第二延伸头提供微电子器件的集成电容器的第一极板的至少一部分。集成电容器的第二极板可位于第一极板的上方或下方。微电子器件通过同时形成第一支柱和第二支柱并且通过同时形成第一延伸头和第二延伸头来形成。

11.应注意,在本公开中可能使用诸如上方、上面、下方和下面等术语。这些术语不应被解释为限制结构或元件的位置或取向,而应被用于提供结构或元件之间的空间关系。

12.图1a至图1g是具有集成电容器的示例微电子器件的横截面,其在示例形成方法的各个阶段中描绘。参考图1a,微电子器件100包括管芯101。例如,管芯101可实施为集成电路、分立半导体器件、mems器件或微流体器件。本示例的管芯101具有衬底102,该衬底可包括诸如硅的半导体材料或诸如二氧化硅、氮化硅、氧氮化硅、玻璃、蓝宝石、陶瓷的介电材料或诸如聚酰亚胺、硅酮或聚乙烯的聚合物材料。衬底102可为包含额外管芯的晶片或工件的一部分,或者可仅包括管芯101。管芯101具有连接表面103;如图1a所示,衬底102可延伸至连接表面103。

13.本示例的管芯101包括在连接表面103处的第一端子104、第二端子105和第三端子106。第一端子104、第二端子105和第三端子106是导电的,并且可包括例如铝、铜、镍、钯、铂、金、钛或钨。举例来说,第一端子104、第二端子105和第三端子106可实现为凸块键合垫或穿通衬底的通孔。第一端子104、第二端子105和第三端子106可通过通孔107或其他互连元件电耦合到管芯101中的部件。保护外涂(po)层108可设置在连接表面103上方,并具有暴露第一端子104、第二端子105和第三端子106的开口。举例来说,po层108可包含二氧化硅、氮化硅、氮氧化硅或聚酰亚胺。po层108可以可选地作为管芯101的一部分。

14.本示例的管芯101包括集成电容器110的第二极板109。第二极板109可具有与第一端子104、第二端子105和第三端子106类似的导电材料的成分。如图1a所示,第二极板109可被po层108覆盖。第二极板109可通过一个或多个通孔107电耦合到管芯101中的部件。

15.第一界面层111形成在连接表面103上方,并接触端子104、105和106。第一界面层111是导电的。第一界面层111可包含接触po层108和端子104、105和106的粘附子层(在图1a中未示出)。该粘附子层可包含钛或钨,例如用以提供第一界面层111对po层108和端子104、105和106的粘附。第一界面层111可包含在粘附子层上的势垒子层(在图1a中未示出)。例如,该势垒子层可包含镍、钴、钽、氮化钽、钛或氮化钛,例如用以减少铜从第一支柱113、第二支柱114和第三支柱115扩散到管芯101中。铜扩散到管芯101中可降低微电子器件100的性能。第一界面层111可包含在势垒子层上的镀覆种子子层(在图1a中未示出)。该镀覆种子子层可包含铜、镍或金,以提供适合电镀的低电阻层。第一界面层111可通过一系列溅射工艺、蒸发工艺、冷喷涂工艺或其他薄膜沉积工艺来形成。

16.支柱掩模112形成在第一界面层111上。支柱掩模112暴露出用于第一支柱113、第二支柱114和第三支柱115的区域中的第一界面层111。用于第一支柱113的区域位于第一端子104上方,用于第二支柱114的区域位于第二端子105上方,并且用于第三支柱115的区域

位于第三端子106上方。支柱掩模112可包含光刻胶,并且可使用光刻工艺来形成。可替代地,支柱掩模112可通过胶带施加工艺、诸如材料喷射或材料挤压的增材工艺或诸如激光烧蚀的减材工艺来形成。举例来说,支柱掩模112可具有1微米至100微米的厚度。

17.通过使用第一镀液116的第一镀覆工艺,第一支柱113、第二支柱114和第三支柱115在由支柱掩模112暴露的区域中同时形成在第一界面层111上。第一镀液116可包含铜离子,使得支柱113、114和115包含铜。除了铜离子之外,第一镀液116还可包含诸如镍离子或金离子的其他金属离子,使得支柱113、114和115包含镍或金,以在支柱113、114和115中提供期望的机械性能。第一镀覆工艺可以实施为电镀工艺,其中电流从第一镀液116流到第一界面层111,从而提供更一致的镀覆速率。可替代地,第一镀覆工艺可以实施为化学镀工艺,从而降低微电子器件100的制造复杂性。举例来说,支柱113、114和115可具有1微米至100微米的垂直于连接表面103的高度。支柱113、114和115因此通过第一界面层111机械地耦合到连接表面103。在形成支柱113、114和115之后,微电子器件100与第一镀液116分离。支柱掩模112留在原位以用于后续制造步骤。

18.参考图1b,第二界面层117形成在支柱掩模112上方,并且接触支柱113、114和115。第二界面层117是导电的。第二界面层117可包含接触支柱掩模112和支柱113、114和115的粘附子层,并且可包含接触粘附子层的镀覆种子子层。第二界面层117的粘附子层可具有与参考第一界面层111的粘附子层所公开的成分类似的成分。第二界面层117的镀覆种子子层可具有与参考第一界面层111的镀覆种子子层所公开的成分类似的成分。

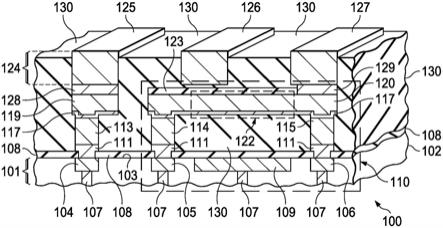

19.头掩模118形成在第二界面层117上方。头掩模118在用于随后形成的第一延伸头119和随后形成的第二延伸头120的区域中暴露出第二界面层117;图1c示出了第一延伸头119和第二延伸头120。返回参考图1b,用于第一延伸头119的区域暴露出第一支柱113上方的第二界面层117,并且在平行于连接表面103的至少一个方向上延伸越过第一支柱113。用于第二延伸头120的区域暴露出第二支柱114和第三支柱115上方的第二界面层117,在平行于连接表面103的至少一个方向上延伸越过第二支柱114,并且在平行于连接表面103的至少一个方向上延伸越过第三支柱115。头掩模118可包含光刻胶,并且可使用光刻工艺来形成。可替代地,头掩模118可通过胶带施加工艺、诸如材料喷射或材料挤压的增材工艺,或诸如激光烧蚀的减材工艺来形成。头掩模118可具有与支柱掩模112不同的成分,或者可通过与用于形成支柱掩模112的工艺不同的工艺来形成。

20.参考图1c,通过使用第二镀液121的第二电镀工艺,第一延伸头119和第二延伸头120在由头掩模118所暴露的区域中同时形成在第二界面层117上。第二镀液121可包含铜离子,使得第一延伸头119和第二延伸头120包含铜。除了铜离子之外,第二镀液121还可以包含诸如镍离子或金离子的其他金属离子,使得第一延伸头119和第二延伸头120包含镍或金,以在第一延伸头119和第二延伸头120中提供期望的机械性能。第二电镀工艺可实施为电镀工艺,其中电流从第二镀液121流到第二界面层117,从而提供更一致的镀覆速率。可替代地,第二电镀工艺可实施为化学镀工艺,从而降低微电子器件100的制造复杂性。举例来说,第一延伸头119和第二延伸头120可具有垂直于连接表面103的1微米至25微米的厚度。第一延伸头119通过第二界面层117电耦合到第一支柱113,并在平行于连接表面103的至少一个方向上延伸越过第一支柱113。第二延伸头120通过第二界面层117电耦合到第二支柱114,并在平行于连接表面103的至少一个方向上延伸越过第二支柱114。在形成第一延伸头

119和第二延伸头120之后,微电子器件100与第二镀液121分离。第二延伸头120位于第二极板109上方。

21.参考图1d,隔离层123形成在第二延伸头120上,覆盖第二延伸头120的第一部分并暴露出第二延伸头120的第二部分。举例来说,隔离层123可实施为焊料掩模,并且可包括例如环氧树脂、聚酯或树脂,并且可通过点胶(dispensing)、丝网印刷或光刻工艺来形成。

22.参考图1e,图1d的头掩模118被去除。头掩模118可通过溶解在有机溶剂中来去除,而将隔离层123留在原处。在去除头掩模118之后,图1d的第二界面层117在由第一延伸头119和第二延伸头120所暴露的地方被去除。第二界面层117可通过使用稀酸水溶液的一种或多种湿法蚀刻工艺来去除。在去除第一延伸头119和第二延伸头120所暴露的第二界面层117之后,去除图1d的支柱掩模112。支柱掩模112可通过溶解在有机溶剂中来去除,而将隔离层123留在原处。支柱掩模112可通过与用于去除头掩模118的工艺类似的工艺来去除。在支柱掩模112被去除之后,图2d的第一界面层111在由第一支柱113、第二支柱114和第三支柱115所暴露的地方被去除。第一界面层111可通过使用稀酸水溶液的一种或多种湿法蚀刻工艺来去除,该湿法蚀刻工艺可类似于用于去除第二界面层117的湿法蚀刻工艺。

23.参考图1f,提供了微电子器件100的引线框架124。引线框架124包括第一引线125、第二引线126和第三引线127。举例来说,引线125、126和127可包含铜、不锈钢或可伐合金(kovar),并且可镀覆有镍、钯或金。第一延伸头119提供微电子器件100的凸块垫。举例来说,凸块垫可实施为焊料凸块垫或粘合凸块垫。第一引线125通过第一焊接连接件128电耦合到第一延伸头119,并且第三引线117通过第二焊接连接件129电耦合到第二延伸头120,该第二焊接连接件129在由隔离层123所暴露的第二延伸头120的第二部分上。在本示例的替代实施方式中,第一引线125可通过导电粘合剂(诸如具有铜或银颗粒的环氧树脂)的第一部分电耦合到第一延伸头119。在此种替代实施方式中,第三引线127可通过导电粘合剂的第二部分电耦合到第二延伸头120。第二引线126通过隔离层123与第二延伸头120电隔离。集成电容器110可用于将来自引线框架124的第三引线127的信号电容耦合到集成电容器110的第二极板109。集成电容器110可形成为有利地具有期望的电容而不消耗管芯101中的区域。

24.参考图1g,封装隔离结构130形成在管芯101上,横向围绕支柱113、114和115、第一延伸头119和第二延伸头120,并接触引线125、126和127。术语“横向”指的是平行于连接表面103的方向,并且同样适用于本文所公开的其他示例。封装隔离结构130是不导电的,并且可包括诸如环氧树脂、硅树脂或苯并环丁烯(bcb)的介电材料,并且可包括诸如二氧化硅颗粒的介电颗粒,以降低封装隔离结构130的热膨胀系数。第二延伸头120和接触第二延伸头120的第二界面层117提供集成电容器110的第一极板122。本示例的封装隔离结构130在集成电容器100的第一极板122和集成电容器110的第二极板109之间延伸,与在电容器极板之间没有封装介电材料的电容器相比,这可有利地提供集成电容器110的更大电容。图1g描绘了完成的微电子器件100。

25.图2a至图2f是具有集成电容器的另一示例微电子器件的横截面,其在另一示例形成方法的各个阶段中描绘。参考图2a,微电子器件200包括管芯201。例如,管芯201可实施为参考图1a的管芯101公开的任何示例。本示例的管芯201具有衬底202,该衬底202可为包括附加管芯的晶片或工件的一部分,或者可仅包括管芯201。管芯201具有连接表面203;如图

2a所示,衬底202可延伸到连接表面203。

26.本示例的管芯201包括连接表面203处的第一端子204、第二端子205和第三端子206。第一端子204、第二端子205和第三端子206是导电的。举例来说,端子204、205和206可实施为凸块键合垫或穿过衬底的通孔。端子204、205和206可通过通孔207电耦合到管芯201中的部件。

27.本示例的管芯201包括集成电容器210的第二极板209。第二极板209是导电的。如图2a所示,第二极板209可延伸至连接表面203。第二极板209可通过一个或多个通孔207电耦合到管芯201中的部件。

28.支柱掩模212形成在连接表面203上。支柱掩模212在用于随后形成的第一支柱213的区域中暴露出第一端子204,在用于随后形成的第二支柱214的区域中暴露出第二端子205,并且在用于随后形成的第三支柱215的区域中暴露出第三端子206。本示例的支柱掩模212可使用光刻工艺由光敏环氧树脂形成。可替代地,本示例的支柱掩模212可包含粘合剂材料中的无机颗粒,通过诸如材料喷射或材料挤压的增材工艺来形成。举例来说,支柱掩模212可具有1微米至100微米的厚度。图2c示出了第一支柱213、第二支柱214和第三支柱215。

29.参考图2b,界面层231形成在支柱掩模212上方,延伸到用于第一支柱213、第二支柱214和第三支柱215的区域内,并接触第一端子204、第二端子205和第三端子206。界面层231是导电的。界面层231可包含接触端子204、205和206的粘附子层(图2b中未示出)。界面层231可包含在粘附子层上的势垒子层(图2b中未示出)。界面层231可包含在势垒子层上的镀覆种子子层(图2b中未示出)。界面层231可通过一系列薄膜沉积工艺来形成。

30.头掩模218形成在界面层231上方。头掩模218在用于随后形成的第一延伸头219和随后形成的第二延伸头220的区域中暴露出界面层231。用于第一延伸头219的区域暴露出第一支柱213上方的界面层231,并在平行于连接表面203的至少一个方向上延伸越过第一支柱213。用于第二延伸头220的区域暴露出第二支柱214和第三支柱215上方的界面层231,在平行于连接表面203的至少一个方向上延伸越过第二支柱214,并在平行于连接表面203的至少一个方向上延伸越过第三支柱215。头掩模218可包含光刻胶,并且可使用光刻工艺来形成。可替代地,头掩模218可通过胶带施加工艺、诸如材料喷射或材料挤压的增材工艺或诸如激光烧蚀的减材工艺来形成。图2c示出了第一延伸头219和第二延伸头220。

31.参考图2c,通过使用镀液232的镀覆工艺,第一支柱213、第二支柱214和第三支柱215在由支柱掩模212所暴露的区域中同时形成在界面层231上。继续进行镀覆工艺以在由头掩模218暴露的区域中同时在第一支柱213上形成第一延伸头219并在第二支柱214和第三支柱215上形成第二延伸头220。第二延伸头220位于第二极板209上方。镀液232可包含铜离子、镍离子或金离子,使得支柱213、214和215以及第一延伸头219和第二延伸头220可包含铜、镍或金。镀覆工艺可实施为电镀工艺或化学镀工艺。支柱213、214和215可具有垂直于连接表面203的1微米至100微米的高度。举例来说,第一延伸头219和第二延伸头220可具有垂直于连接表面203的1微米至25微米的厚度。支柱213、214和215因此通过界面层231机械耦合到连接表面203。第一延伸头219直接电耦合到第一支柱213,并且在平行于连接表面203的至少一个方向上延伸越过第一支柱213。第二延伸头220直接电耦合到第二支柱214,并且在平行于连接表面203的至少一个方向上延伸越过第二支柱214。在形成支柱213、214和215以及第一延伸头219和第二延伸头220之后,微电子器件200与镀液232分离。

32.参考图2d,隔离层223形成在第二延伸头220上。隔离层223可实施为焊料掩模,并且可包括例如环氧树脂、聚酯或树脂,并且可通过点胶、丝网印刷或光刻工艺来形成。在本示例中,隔离层223覆盖由头掩模218暴露出的第二延伸头220。

33.参考图2e,图2d的头掩模218被去除。头掩模218可通过溶解在有机溶剂中来去除,而将隔离层223和支柱掩模212留在原处。在去除头掩模218之后,图2d的界面层231在由第一延伸头219和第二延伸头220暴露出的地方被去除,而将隔离层223和支柱掩模212留在原处。界面层231可通过使用稀酸水溶液的一种或多种湿法蚀刻工艺来去除。该示例的支柱掩模212提供用于支柱213、214和215以及用于第一延伸头219和第二延伸头220的永久支撑。

34.参考图2f,第一延伸头219提供微电子器件200的凸块垫。举例来说,凸块垫可实施为焊料凸块垫或粘合凸块垫。焊料凸块233形成在第一延伸头219上。焊料凸块233可通过将焊膏分配到第一延伸头219上,之后在回流工艺中加热焊膏以在焊料凸块233与第一延伸头219之间提供低电阻界面而形成。

35.第二延伸头220和接触第二延伸头220的界面层213提供集成电容器210的第一极板222。本示例的支柱掩模212在集成电容器210的第一极板222和集成电容器210的第二极板209之间延伸,与在电容器极板之间没有封装介电材料的电容器相比,这可有利地提供集成电容器210的更大电容。图2f描绘了完成的微电子器件200。

36.图3a至图3j是具有集成电容器的进一步示例微电子器件的横截面,其在进一步示例形成方法的各个阶段中描绘。参考图3a,微电子器件300包括管芯301。例如,管芯301可实施为参考图1a的管芯101所公开的任何示例。本示例的管芯301具有衬底302,该衬底302可为包括附加管芯的晶片或工件的一部分,或者可仅包括管芯301。管芯301具有连接表面303;如图3a所示,衬底302可延伸到连接表面303。

37.本示例的管芯301包括在连接表面303处的第一端子304和第二端子334。第一端子304和第二端子334是导电的。举例来说,端子304和334可实施为凸块键合垫或穿过衬底的通孔。端子304和334可通过通孔307电耦合到管芯301中的部件。

38.第一界面层311形成在连接表面303上方,接触端子304和334。第一界面层311可具有类似于图1a的第一界面层111的成分和子层结构。电容器掩模335形成在第一界面层311上方,并且在用于集成电容器310的第二极板309的区域中暴露出第一界面层311。电容器掩模335可包含通过由光刻工艺形成的光刻胶,或者可包含由丝网印刷或增材工艺形成的聚合物。

39.参考图3b,集成电容器310的第二极板309形成在由电容器掩模335暴露出的第一界面层311上。第二极板309通过使用第一镀液336的第一镀覆工艺来形成。第一镀液336可包含铜离子、镍离子或金离子,使得第二极板309可包含铜、镍或金。第一镀覆工艺可实施为电镀工艺或化学镀工艺。举例来说,第二极板309可具有1微米至100微米的厚度。在形成第二极板309之后,微电子器件300与镀液336分离。

40.参考图3c,图3b的电容器掩模335被去除,而将第一界面层311和第二极板309留在原处。例如,电容器掩模335可通过溶解在有机溶剂或有机酸中来去除。用于去除电容器掩模335的其他方法在本示例的范围内。

41.参考图3d,支柱掩模312形成在第一界面层311上,覆盖第二极板309。支柱掩模312在用于第一支柱313、第二支柱314和第三支柱315的区域中暴露出第一界面层311。用于第

一支柱313的区域位于第一端子304上方,用于第二支柱314的区域位于第二极板309的一侧上,并且用于第三支柱315的区域位于第二极板309的另一侧上。支柱掩模312可包含光刻胶,并且可使用光刻工艺来形成。可替代地,支柱掩模312可通过胶带施加工艺、增材工艺或减材工艺来形成。举例来说,支柱掩模312可具有比第二极板309的厚度大1微米至50微米的厚度。

42.参考图3e,通过使用第二镀液316的第二镀覆工艺,第一支柱313、第二支柱314和第三支柱315在由支柱掩模312暴露出的区域中同时形成在第一界面层311上。第二镀液316可包含铜离子、镍离子或金离子,使得支柱313、314和315包含铜、镍或金。第二镀覆工艺可实施为电镀工艺或化学镀工艺。举例来说,支柱313、314和315可具有垂直于连接表面303的比第二极板309的厚度大1微米至50微米的高度。支柱313、314和315因此通过第一界面层311机械耦合到连接表面303。在形成支柱313、314和315之后,微电子器件300与第二镀液316分离。支柱掩模312留在原位以用于后续制造步骤。

43.参考图3f,第二界面层317形成在支柱掩模312上方,并接触支柱313、314和315。第二界面层317是导电的。第二界面层317可包含接触支柱掩模312和支柱313、314和315的粘附子层,并且可包含接触粘附子层的镀覆种子子层。第二界面层317的粘附子层可具有与参考第一界面层311的粘附子层所公开的成分类似的成分。第二界面层317的镀覆种子子层可具有与参考第一界面层311的镀覆种子子层所公开的成分类似的成分。

44.头掩模318形成在第二界面层317上方。头掩模318在用于随后形成的第一延伸头319和随后形成的第二延伸头320的区域中暴露出第二界面层317;图3g示出第一延伸头319和第二延伸头320。返回参考3f,用于第一延伸头319的区域暴露出第一支柱313上方的第二界面层317,并且在平行于连接表面303的至少一个方向上延伸越过第一支柱313。用于第二延伸头320的区域暴露出第二支柱314和第三支柱315上方的第二界面层317,在平行于连接表面303的至少一个方向上延伸越过第二支柱314,并且在平行于连接表面303的至少一个方向上延伸越过第三支柱315。头掩模318可包含光刻胶,并且可使用光刻工艺来形成。可替代地,头掩模318可通过胶带施加工艺、增材工艺或减材工艺来形成。头掩模318可具有与支柱掩模312不同的成分,或者可通过与用于形成支柱掩模312的工艺不同的工艺形成。

45.参考图3g,通过使用第三镀液321的第三镀覆工艺,第一延伸头319和第二延伸头320在由头掩模318暴露的区域中同时形成在第二界面层317上。第三镀液321可包含铜离子、镍离子或金离子,使得第一延伸头319和第二延伸头320包含铜、镍或金。第三镀覆工艺可实施为电镀工艺或化学镀工艺。举例来说,第一延伸头319和第二延伸头320可具有垂直于连接表面303的1微米至25微米的厚度。第一延伸头319通过第二界面层317电耦合到第一支柱313,并且在平行于连接表面303的至少一个方向上延伸越过第一支柱313。第二延伸头320通过第二界面层317电耦合到第二支柱314,并且在平行于连接表面303的至少一个方向上延伸越过第二支柱314。在形成第一延伸头319和第二延伸头320之后,微电子器件300与第三镀液321分离。第二延伸头320位于第二极板309上方。

46.参考图3h,图3g中的头掩模318被去除。头掩模318可通过溶解在有机溶剂或有机酸中来去除,而将第一延伸头319和第二延伸头320留在原处。在去除头掩模318之后,图3g的第二界面层317在由第一延伸头319和第二延伸头320暴露的地方被去除。第二界面层317可通过使用稀酸水溶液的一种或多种湿法蚀刻工艺来去除。在去除由第一延伸头319和第

二延伸头320暴露的第二界面层317之后,图3g的支柱掩模312被去除。支柱掩模312可通过溶解在有机溶剂或有机酸中来去除,而将第一支柱313、第二支柱314、第三支柱315、第一延伸头319和第二延伸头320留在原处。支柱掩模312可通过与用于去除头掩模318的工艺类似的工艺来去除。在支柱掩模312被去除之后,图3g的第一界面层311在由支柱313、314和315以及第二极板309暴露的地方被去除。第一界面层311可通过使用稀酸水溶液的一种或多种湿法蚀刻工艺来去除,该湿法蚀刻工艺可类似于用于去除第二界面层317的湿法蚀刻工艺。如图3h所示,第一界面层311的去除可导致去除在第一延伸头319和第二延伸头320下方的由支柱313、314和315暴露出的第二界面层317。

47.参考图3i,封装隔离结构330形成在管芯301上,横向围绕支柱313、314和315,并且接触第一延伸头319和第二延伸头320。封装隔离结构330是导电的。第二延伸头320提供集成电容器310的第一极板322。本示例的封装隔离结构330在集成电容器310的第一极板322和集成电容器310的第二极板309之间延伸,与在电容器的极板之间没有封装介电材料的电容器相比,这可有利地提供集成电容器310的更大电容。举例来说,封装隔离结构330可通过注射成型或反应注射成型来形成。在形成封装隔离结构330时,第三支柱315可有利地为第二延伸头320提供机械支撑。

48.参考图3j,第一延伸头319提供微电子器件300的凸块垫。举例来说,凸块垫可实施为焊料凸块垫或黏合凸块垫。第一焊料凸块333形成在第一延伸头319上,并且第二凸块垫337形成在第二延伸头320上。第一焊料凸块333和第二焊料凸块337可通过将焊膏分配到第一延伸头319和第二延伸头320上且之后在回流工艺中加热焊膏来形成。图3j描绘了完成的微电子器件300。在本示例中,集成电容器310的第一极板322可通过第二焊料凸块337电耦合到印刷电路板或芯片载体(图3j中未示出)。第一极板通过第一界面层311和第二端子334电耦合到管芯301中的一个或多个部件。

49.图4a至图4g是具有集成电容器的另一示例微电子器件的横截面,其在另一示例形成方法的各个阶段中描绘。参考图4a,微电子器件400包括管芯401。例如,管芯401可实施为参考图1a的管芯101所公开的任何示例。本公开的管芯401具有衬底402,该衬底402可为包括附加管芯的晶片或工件的一部分,或可仅包括管芯401。管芯401具有连接表面403;如图4a所示,衬底402可延伸至连接表面403。本示例的管芯401包括在连接表面403处的第一端子404、第二端子405和第三端子434。举例来说,端子404、405和434是导电的,并且可实施为凸块键合垫或穿过衬底的通孔。端子404、405和434可通过通孔407电耦合到管芯401中的部件。

50.第一界面层411形成在连接表面403上方,并接触端子404、405和434。第一界面层411可具有类似于图1a的第一界面111的成分和子层结构。

51.支柱掩模412形成在第一界面层411上。支柱掩模412在用于集成电容器410的第一支柱413、第二支柱414和第二极板409的区域中暴露出第一界面层411。用于第一支柱413的区域位于第一端子404上方,用于第二支柱414的区域位于第二端子405上方,并且用于第二极板409的区域位于第三端子434上方。支柱掩模412可包含光刻胶,并且可使用光刻工艺来形成,或者可通过胶带施加工艺、增材工艺或减材工艺来形成。举例来说,支柱掩模412可具有1微米至100微米的厚度。

52.参考图4b,通过使用第一镀液416的第一镀覆工艺,第一支柱413、第二支柱414和

第二极板409在由支柱掩模412暴露出的区域中同时形成在第一界面层411上。第一镀液416可包含铜离子、镍离子或金离子,使得支柱413和414以及第二极板409包含铜、镍或金。第一镀覆工艺可实施为电镀工艺或化学镀工艺。举例来说,支柱413和414以及第二极板409可具有垂直于连接表面403的1微米至100微米的高度。支柱413和414因此通过第一界面层411机械耦合到连接表面403。在形成支柱413和414以及第二极板409之后,微电子器件400与第一镀液416分离。支柱掩模412留在原位以用于后续制造步骤。

53.参考图4c,电容器介电层438形成在第二极板409上方。电容器介电层438可包含诸如环氧树脂或聚酰亚胺的有机聚合物、硅酮聚合物或诸如粘合剂材料中的二氧化硅颗粒的无机材料。电容器介电层438可通过光刻工艺、丝网印刷或增材工艺来形成。举例来说,电容器介电层438可具有100纳米至10微米的厚度。

54.参考图4d,第二界面层417形成在支柱掩模412上方,接触支柱413和414,并且在电容器介电层438上方延伸。第二界面层417是导电的。第二界面层417可包含接触支柱掩模412、支柱413和414以及电容器介电层438的粘附子层,并且可包含接触粘附子层的镀覆种子子层。第二界面层417的粘附子层可具有与参考第一界面层411的粘附子层所公开的成分类似的成分。第二界面层417的镀覆种子子层可具有与参考第一界面层411的镀覆种子子层所公开的成分类似的成分。

55.参考图4e,头掩模418形成在第二界面层417上方。头掩模418在用于随后形成的第一延伸头419和随后形成的第二延伸头412的区域中暴露出第二界面层417;图4f示出了第一延伸头419和第二延伸头420。返回参考图4e,用于第一延伸头419的区域暴露出第一支柱413上方的第二界面层417,并在平行于连接表面403的至少一个方向上延伸越过第一支柱413。用于第二延伸头420的区域暴露出第二支柱414和电容器介电层438上方的第二界面层417,并在平行于连接表面403的至少一个方向上延伸越过第二支柱414。头掩模418可包含光刻胶,并且可使用光刻工艺来形成。可替代地,头掩模418可通过胶带施加工艺、增材工艺或减材工艺来形成。头掩模418可具有与支柱掩模412不同的成分,或者可通过与用于形成支柱掩模412的工艺不同的工艺形成。

56.参考图4f,通过使用第二镀液421的第二镀覆工艺,第一延伸头419和第二延伸头420在由头掩模418暴露出的区域中同时形成在第二界面层417上。第二镀液421可包含铜离子、镍离子或金离子,使得第一延伸头419和第二延伸头420包含铜、镍或金。第二镀覆工艺可实施为电镀工艺或化学镀工艺。举例来说,第一延伸头419和第二延伸头420可具有垂直于连接表面403的1微米至25微米的厚度。第一延伸头419通过第二界面层417电耦合到第一支柱413,并且在平行于连接表面403的至少一个方向上延伸越过第一支柱413。第二延伸头420通过第二界面层417电耦合到第二支柱414,并且在平行于连接表面403的至少一个方向上延伸越过第二支柱414。在形成第一延伸头419和第二延伸头420后,微电子器件400与第二镀液421分离。第二延伸头420位于第二极板409上方。

57.参考图4g,图4f的头掩模418被去除,而将第一延伸头419和第二延伸头420留在原位。图4f的第二界面层417在由第一延伸头419和第二延伸头420暴露出的地方被去除。图4f的支柱掩模412被去除,而将第一支柱413、第二支柱414、第二极板409、第一延伸头419和第二延伸头420留在原位。图4f的第一界面层411在由支柱413和414以及第二极板409暴露出的地方被去除。头掩模418、第二界面层417、支柱掩模412和第一界面层411可通过参考本文

其他示例的相应掩模和界面层的去除所公开的工艺来去除。

58.隔离层423可以可选地形成在第二延伸头420上。举例来说,隔离层423可实施为焊料掩模,并且可包含例如环氧树脂、聚酯或树脂,并且可通过点胶、丝网印刷或光刻工艺来形成。隔离层423可以可选地在去除头掩模418之前形成。第一延伸头419提供微电子器件400的凸块垫。举例来说,凸块垫可实施为焊料凸块垫或粘合凸块垫。第一焊料凸块433形成在第一延伸头419上。第一焊料凸块433可通过与参考图2f的焊料凸块233所公开的工艺相似的工艺来形成。

59.图4g描绘了完成的微电子器件400。第二延伸头420和接触第二延伸头420的第二界面层提供集成电容器410的第一极板422。第一极板通过第一界面层411和第二端子414电耦合到管芯401中的一个或多个部件。电容器介电层438将第一极板422与第二极板409分开,这可有利地为本示例的集成电容器410提供高电容值。

60.图5a至图5c是具有集成电容器的进一步示例微电子器件的横截面,其在进一步示例形成方法的各个阶段中描绘。参考图5a,微电子器件200包括管芯501。例如,管芯501可实施为参考图1a的管芯101所公开的任何示例。本示例的管芯501具有衬底502,该衬底502可为包括附加管芯的晶片或工件的一部分,或可仅包括管芯501。管芯501具有连接表面503;如图5a所示,衬底502可延伸到连接表面503。本示例的管芯501包括连接表面503处的第一端子504、第二端子505和第三端子506。举例来说,端子504、505和506是导电的,并且可实施为凸块键合垫或穿过衬底的通孔。端子504、505和506可电耦合到管芯501中的部件。

61.第一支柱513、第二支柱514和第三支柱515分别同时形成在第一端子504、第二端子505和第三端子506上。支柱513、514和515因此机械耦合到连接表面503。支柱513、514和515是导电的。第一延伸头519和第二延伸头520同时形成在支柱513、514和515上。第一延伸头519接触第一支柱513,并在平行于连接表面503的至少一个方向上延伸越过第一支柱513。第二延伸头520接触第二支柱514和第三支柱515,在平行于连接表面503的至少一个方向上延伸越过第二支柱514,并在平行于连接表面503的至少一个方向上延伸越过第三支柱515。支柱513、514和515、第一延伸头519和第二延伸头520可通过本文示例中公开的任何方法来形成。可替代地,支柱513、514和515、第一延伸头519和第二延伸头520可通过诸如三维(3d)金属印刷的增材工艺来形成。在支柱513、514和515通过增材工艺来形成的情况下,支柱513、514和515通过相同的增材工艺来形成,使得支柱513、514和515同时(即在同一操作中或同步)形成。术语“同时”包括在形成第二支柱514的一部分或全部之前形成第一支柱513的一部分或全部的情况,这在使用具有有限数量的打印头或材料分配喷嘴的增材工艺时可能发生,并且对于第一延伸头519和第二延伸头520是类似的。用于同时形成支柱513、514和515以及同时形成第一延伸头519和第二延伸头520的其他方法在本示例的范围内。

62.电容器介电层538形成在第二延伸头520上方,在第二延伸头520的与连接表面503相对的表面上。电容器介电层538可具有成分,并且可通过参考图4c的电容器介电层438所公开的方法来形成。

63.参考图5b,提供了微电子器件500的引线框架524。引线框架524包括第一引线525和第二引线526。引线525和526可包括参考图1f的引线框架124所公开的任何材料。第一延伸头519提供微电子器件500的凸块垫。举例来说,凸块垫可实施为焊料凸块垫或粘合凸块垫。第一引线525通过焊接连接528电耦合到第一延伸头519。第二引线526位于第二延伸头

520上方,并通过电容器介电层538与第二延伸头520电隔离。

64.参考图5c,封装隔离结构530形成在管芯501上,横向围绕支柱513、514和515、第一延伸头519和第二延伸头520,并且接触引线525和526。封装隔离结构530是不导电的,并且可包括参考图1g的封装隔离结构130所公开的任何材料。

65.第二延伸头520提供集成电容器510的第一极板522。第二引线526提供集成电容器510的第二极板509,面对第一极板522的与连接表面503相对的一侧。将第一极板522与第二极板509分开的电容器介电层538可有利地为本示例的集成电容器510提供高电容值。如图5c所示,本示例的封装隔离结构530可以可选地在第一极板522和第二极板509之间延伸。图5c描绘了完成的微电子器件500。

66.本文公开的示例的各种特征可结合在微电子器件的其他表现形式中。例如,任何微电子器件的第一支柱和第二支柱可根据参考图1a至图1g、图2a至图2f、图3a至图3j或图4a至图4g所公开的方法所公开的那样同时形成。类似地,任何微电子器件的第一延伸头和第二延伸头可根据参考图1a至图1g、图2a至图2f、图3a至图3j或图4a至图4g所公开的方法所公开的那样同时形成。任何集成电容器都可具有如图4c或图5c所示的电容器介电层。任何微电子器件的第二延伸头都可如图1g或图3j所示电耦合到外部端子。

67.尽管上面已经描述了本公开的各种实施例,但应该理解它们仅以示例的方式而不是限制的方式呈现。在不偏离本公开的精神或范围的情况下,可根据本文的公开对公开的实施例进行许多改变。因此,本发明的广度和范围不应受任何上述实施例的限制。相反,本公开的范围应根据所附权利要求及其等效物来定义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。