一种dma二维数据传输/清零参数配置方法

技术领域

1.本发明涉及dma二维数据传输技术领域,尤其是一种dma二维数据传输/清零参数配置方法。

背景技术:

2.魂芯,是由中国电子科技集团公司第三十八研究所设计,在一秒钟内能完成千亿次浮点操作运算的高性能通用数字信号处理器。2012年,该所推出高性能浮点通用dsp芯片——“魂芯一号”,性能相当于同期市场同类dsp芯片的4-6倍,可应用于高性能计算的信号处理领域,已经在多款重大装备中成功应用。魂芯二号a,发布于2018年,是中国电子科技集团公司第三十八研究所在信号处理器领域的新突破。dma数据传输可分成一维dma数据传输和dma二维数据传输。针对dma二维数据传输来说,在dma数据传输启动前,需配置dma传输参数,参数包括源端地址、目标端地址、优先级、源端递增/递减步长,目标端递增/递减步长、传输数据长度、传输模式控制等。

3.在现有的“魂芯一号”或“魂芯二号”的处理器设计中,dma传输参数是逐条配置的,每条指令占用一个指令执行行,每个指令执行行耗费1个时钟周期,因此dma参数配置需要多个时钟周期来完成。以如下11行的代码段为例,二维dma参数配置共需11个时钟周期。

4.l1

ꢀꢀ

目标端起始地址:dma0_dsah=0x00000000

5.l2

ꢀꢀ

目标端起始地址:dma0_dsal=xr10

6.l3

ꢀꢀ

目标端x维长度:dma0_dlx=xr16

7.l4

ꢀꢀ

目标端x维步长:dma0_das=xr21

8.l5

ꢀꢀ

目标端y维长度:dma0_dly=xr26

9.l6

ꢀꢀ

源端起始地址:dma0_ssa=xr12

10.l7

ꢀꢀ

源端x维长度:dma0_slx=xr16

11.l8

ꢀꢀ

源端x维步长:dma0_sas=xr21

12.l9

ꢀꢀ

源端y维长度:dma0_sly=xr26

13.l10 dma传输模式控制:dma0_ctl=0x00010203

14.l11 dma传输启动:dma0_start=0x00000001

技术实现要素:

15.针对现有dma二维数据传输前dma传输参数配置耗费多个时间周期的技术问题,本发明提供了一种dma二维数据传输/清零参数配置方法,可在单周期内完成dma传输参数的配置,大大缩短dma启动时间。

16.本发明保护一种dma二维数据传输/清零参数配置方法,dma二维数据传输/清零指令的指令机器码采用64位双字指令,内部包含或者隐含所有dma传输/清零参数;

17.寄存器参数配置方法具体包括以下步骤:

18.步骤1,指令通道分配单元根据输入的指令进行通道分配,dma二维数据传输/清零

指令占用8/5个控制寄存器写通道,分别为4/2个通用寄存器访问控制寄存器通道和4/3个立即数访问控制寄存器通道;

19.步骤2,指令识别单元识别指令行中的dma二维数据传输/清零指令,当指令行中含有dma二维数据传输/清零指令时,识别其中的操作码,并输出dma二维传输/清零的标志信息;指令输出单元监测到dma二维传输/清零的标志信息,通过选择器选出对应的dma二维数据传输/清零指令,输出至dma译码单元;

20.步骤4,条件受控单元根据谓词条件判断的输入,通过逻辑判断得到dma二维数据传输/清零指令的条件受控使能结果,输出至dma译码单元;

21.步骤5,dma译码单元通过dma二维数据传输/清零指令,结合谓词条件受控使能输入,译出dma控制寄存器配置信息;

22.步骤6,控制信号合成单元对dma二维数据传输/清零指令的译出信息与其他控制寄存器通道的译出信息进行合成,输出dma控制寄存器的全部配置信息;

23.步骤7,根据控制信号合成单元输出的dma控制寄存器的全部配置信息,对dma控制寄存器进行写入操作,完成dma传输/清零参数的配置。

24.进一步的,将dma传输模式控制寄存器中的2个位段分别设置为完成一条指令完成二维数据传输/清零的dma设置位,当二维数据传输/清零dma设置位=1(即有效),自动启动dma二维数据传输/清零,处理器流水线执行时,该条指令对dma配置的8/5个控制寄存器的写操作在同一周期内执行完成。

25.进一步的,dma二维数据传输指令占用的4个通用寄存器访问控制寄存器通道传输的数据分别为:

26.控制寄存器与通用寄存器通道x,传输“目标端起始地址”控制寄存器的地址、使能及数据;

27.控制寄存器与通用寄存器通道y,传输“目标端步长”控制寄存器的地址、使能及数据;

28.控制寄存器与通用寄存器通道z,传输“源端起始地址”控制寄存器的地址、使能及数据;

29.控制寄存器与通用寄存器通道t,传输“源端步长”控制寄存器的地址、使能及数据;

30.dma二维数据传输指令占用的4个立即数访问控制寄存器通道传输的数据分别为:

31.控制寄存器立即数通道0,传输“模式”控制寄存器的地址、使能及数据;

32.控制寄存器立即数通道1,传输“源端x维长度”控制寄存器的地址、使能及数据;

33.控制寄存器立即数通道2,传输“源端y维长度”控制寄存器的地址、使能及数据;

34.控制寄存器立即数通道3,传输“目标端x维长度”控制寄存器的地址、使能及数据。

35.dma二维数据传输指令的指令形式为[xrd,yrd,p]=[zrs,trs,n,m]:

[0036]

①

zrs表示存储dma的源地址;

[0037]

②

xrd表示存储dma的目标地址,源地址和目标地址均支持片内或片外地址;

[0038]

③

trs表示存储源端二维数据的宽度,即dma传输中源端y维步长;

[0039]

④

yrd表示存储目标二维数据的宽度,即dma传输中目标端y维步长。

[0040]

⑤

n表示待传输数据在源图像中的列数,即dma传输中源端x维长度,其中x维步长

固定为1;

[0041]

⑥

m表示待传输数据在源图像中的行数,即dma传输中源端y维长度,其中y维步长为trs;

[0042]

⑦

p为待传输数据在目标图像中的列数,即dma传输中目标端x维长度,其中x维步长固定为1;

[0043]

⑧

目标端y维长度为n*m/p,其中y维步长为yrd。

[0044]

dma二维数据清零指令占用的2个通用寄存器访问控制寄存器通道传输的数据分别为:

[0045]

控制寄存器与通用寄存器通道x,传输“目标端起始地址”控制寄存器的地址、使能及数据;

[0046]

控制寄存器与通用寄存器通道y,传输“目标端步长”控制寄存器的地址、使能及数据;

[0047]

dma二维数据清零指令占用的3个立即数访问控制寄存器通道传输的数据分别为:

[0048]

控制寄存器立即数通道0,传输“模式”控制寄存器的的地址、使能及数据;

[0049]

控制寄存器立即数通道1,传输“目标端y维长度”控制寄存器的地址、使能及数据;

[0050]

控制寄存器立即数通道2,传输“目标端x维长度”控制寄存器的地址、使能及数据。

[0051]

dma二维数据清零指令的指令形式为[xrd,yrd,p,w]=0:

[0052]

①

xrd表示存储dma的目标地址,目标地址均支持片内或片外地址;

[0053]

②

yrd表示存储目标二维数据的宽度,即dma传输中目标端y维步长;

[0054]

③

p为待清零数据在目标图像中的列数,即dma传输中目标端x维长度;

[0055]

④

w为待清零数据在目标图像中的行数,即dma传输中目标端y维长度。

[0056]

n、m、p、w均为无符号数,n、m各占8位,p、w各占16位。

[0057]

本发明还保护一种基于上述dma二维数据传输/清零参数配置方法的dma二维数据传输/清零方法,核内dma控制器识别dma传输模式控制寄存器的二维数据传输dma设置位和二维数据清零dma设置位,当值为2’b10或者2’b01时,自动启动dma二维数据传输/清零,直至数据传输/清零结束。

[0058]

本发明还保护一种dma二维数据传输/清零指令译码器,由指令通道分配单元、指令识别单元、指令输出单元、条件受控单元、dma译码单元、控制信号合成单元组成,

[0059]

所述指令通道分配单元,用于根据输入的指令进行通道分配,dma二维数据传输/清零指令占用8/5个控制寄存器写通道,分别为4/2个通用寄存器访问控制寄存器通道和4/3个立即数访问控制寄存器通道;

[0060]

所述指令识别单元,用于识别指令行中的dma二维数据传输/清零指令,当指令行中含有dma二维数据传输/清零指令时,识别其中的操作码,并输出dma二维传输/清零的标志信息;

[0061]

所述指令输出单元,用于监测到dma二维传输/清零的标志信息,通过选择器选出对应的dma二维数据传输/清零指令,输出至dma译码单元;

[0062]

所述条件受控单元,用于根据谓词条件判断的输入,通过逻辑判断得到dma二维数据传输/清零指令的条件受控使能结果,输出至dma译码单元;

[0063]

所述dma译码单元,用于通过dma二维数据传输/清零指令,结合谓词条件受控使能

输入,译出dma控制寄存器配置信息;

[0064]

所述控制信号合成单元,用于对dma二维数据传输/清零指令的译出信息与其他控制寄存器通道的译出信息进行合成,输出dma控制寄存器的全部配置信息。

[0065]

本发明从指令形式设计、指令机器码设计层面,提出一种dma二维数据传输/清零参数配置方法,通过采用单条指令在单个时钟周期完成dma传输/清零参数配置;与“魂芯”处理器现有的dma传输参数配置方式以及其他处理器目前采用多条指令完成dma传输参数配置相比,本发明大大提高了dma传输参数的配置效率,减少了汇编代码体积,缩短了dma控制器启动dma二维数据传输的时间。

附图说明

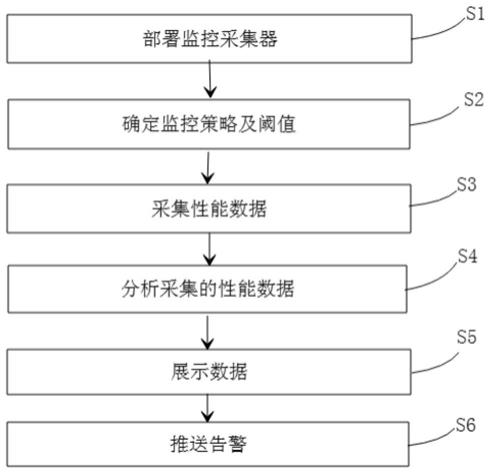

[0066]

图1是dma二维数据传输/清零指令译码器的结构框图。

具体实施方式

[0067]

下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

[0068]

实施例1

[0069]

本发明基于我国自主研发的“魂芯”高性能通用数字信号处理器架构,从指令形式设计、指令机器码设计层面,提出一种dma二维数据传输/清零参数配置方法,通过软硬件相互配合,实现单条指令对dma二维数据传输/清零参数的单周期配置。表1为“魂芯”dsp芯片既有的dma传输模式控制寄存器字段定义表;表2为“魂芯”dsp芯片既有的dma标志寄存器字段定义表,dma标志寄存器在实现dma功能时无需提前配置,属于只读寄存器,用于dma传输配置或者传输过程出错时,对硬件内部装态进行标识。dma运行过程中可以对dma标志寄存器进行读操作,查看dma数据传输的状态信息。

[0070]

[0071][0072]

表1

[0073][0074]

表2

[0075]

dma二维数据传输/清零需要配置的参数较多,本发明中对应的指令机器码采用64位双字指令,内部包含或者隐含所有dma传输/清零参数。

[0076]

隐含的含义有两种:

[0077]

1、将地址存放在通用寄存器中,指令机器码中仅包含该通用寄存器的索引号;

[0078]

2、通过指令机器码中的操作op-code和模式位(参见表3、表4),指令译码器可以直接得到dma传输模式控制寄存器中对应自动启动dma二维数据传输/清零的配置数据。

[0079]

表3、表4分别为本实施例给出的dma二维数据传输指令机器码字段表和dma二维数据清零指令机器码字段表,从中可以看到指令机器码中保存的用于查询地址的通用寄存器

索引。与此相对应的,dma二维数据传输/清零参数配置时,需要占用从寄存器堆到控制寄存器的数据传输通道,实现32位地址的数据传输。

[0080]

位段含义描述63行结束标志62:59保留58:563’b11055:51操作码op-code50:49保留48模式047:44p[15:12]43:38通用寄存器索引rd37:32通用寄存器索引rs31行结束标志30:27参数p[11:8]26:243’b11123:16参数p[7:0]15:8参数n7:0参数m

[0081]

表3

[0082]

位段含义描述63行结束标志62:59保留58:563’b11055:51操作码op-code50:49保留48模式147:44参数p[15:12]43:38通用寄存器索引rd37:32通用寄存器索引rs31行结束标志30:27参数p[11:8]26:243’b11123:16参数p[7:0]15:0参数w

[0083]

表4

[0084]

本实施例为dma二维数据传输指令设计的指令形式为[xrd,yrd,p]=[zrs,trs,n,m]:

[0085]

①

zrs表示存储dma的源地址;

[0086]

②

xrd表示存储dma的目标地址,源地址和目标地址均支持片内或片外地址;

[0087]

③

trs表示存储源端二维数据的宽度,即dma传输中源端y维步长;

[0088]

④

yrd表示存储目标二维数据的宽度,即dma传输中目标端y维步长。

[0089]

⑤

n表示待传输数据在源图像中的列数,即dma传输中源端x维长度,其中x维步长固定为1;

[0090]

⑥

m表示待传输数据在源图像中的行数,即dma传输中源端y维长度,其中y维步长为trs;

[0091]

⑦

p为待传输数据在目标图像中的列数,即dma传输中目标端x维长度,其中x维步长固定为1;

[0092]

⑧

目标端y维长度为n*m/p,其中y维步长为yrd。

[0093]

本实施例为dma二维数据清零指令的指令形式为[xrd,yrd,p,w]=0:

[0094]

①

xrd表示存储dma的目标地址,目标地址均支持片内或片外地址;

[0095]

②

yrd表示存储目标二维数据的宽度,即dma传输中目标端y维步长;

[0096]

③

p为待清零数据在目标图像中的列数,即dma传输中目标端x维长度;

[0097]

④

w为待清零数据在目标图像中的行数,即dma传输中目标端y维长度。

[0098]

n、m、p、w均为无符号数,n、m各占8位,p、w各占16位。

[0099]

从本实施例设计的dma二维数据传输/清零指令形式,可以得出通道需求数量,如下表5所示。根据图像处理领域中数据传输特点,本实施例将源端和目标端的x维步长固定为1,源端和目标端的y维步长为变量,来源于通用寄存器文件。数据传输长度采用立即数的方式进行配置,直接存放在指令机器码中。

[0100]

dma二维数据传输指令中,x、y、z、t这4个运算宏分别占用1个通用寄存器访问控制寄存器通道。通用寄存器索引rd,分别被x宏、y宏使用,可以查询到2个不同的地址xrd、yrd;通用寄存器索引rs,分别被z宏、t宏使用,也可以查询到2个不同的地址zrs和trs。

[0101]

dma二维数据清零指令中,x、y这2个宏运算分别占用1个通用寄存器访问控制寄存器通道。通用寄存器索引rd,分别被x宏、y宏使用,可以查询到2个不同的地址xrd、yrd。

[0102][0103]

表5

[0104]

据此,开始寄存器参数配置,具体包括以下步骤:

[0105]

步骤1,指令通道分配单元根据输入的指令进行通道分配,dma二维数据传输/清零指令占用8/5个控制寄存器写通道,分别为4/2个通用寄存器访问控制寄存器通道和4/3个立即数访问控制寄存器通道(参照表5);

[0106]

步骤2,指令识别单元识别指令行中的dma二维数据传输/清零指令,当指令行中含有dma二维数据传输/清零指令时,识别其中的操作码op-code(参照表3、表4),并输出dma二维传输/清零的标志信息;指令输出单元监测到dma二维传输/清零的标志信息,通过选择器选出对应的dma二维数据传输/清零指令,输出至dma译码单元;

[0107]

步骤4,条件受控单元根据谓词条件判断的输入,通过逻辑判断得到dma二维数据传输/清零指令的条件受控使能结果,输出至dma译码单元;

[0108]

步骤5,dma译码单元通过dma二维数据传输/清零指令,结合谓词条件受控使能输入,译出dma控制寄存器配置信息;

[0109]

步骤6,控制信号合成单元对dma二维数据传输/清零指令的译出信息(参照表5第三列)与其他控制寄存器通道的译出信息进行合成,输出dma控制寄存器的全部配置信息;

[0110]

步骤7,根据控制信号合成单元输出的dma控制寄存器的全部配置信息,对dma控制寄存器进行写入操作,完成dma传输/清零参数的配置。

[0111]

每款处理器都包含众多控制寄存器和标志寄存器的读写通道,不同厂家处理器的读写通道设置也不同。此处的控制信号合成,是指将dma二维传输/清零指令占用的通道控制信号与其他非该指令占用的控制信号合成。

[0112]“魂芯”处理器中共有x、y、z、t 4个运算宏,每个运算宏含有2条通用寄存器写控制寄存器通道,宏外4个立即数写控制寄存器通道,因此一共有12个写通道。本实施例中,dma二维传输指令占用8个写通道,剩余4个写通道也可以被占用,还可以有其他非dma类的控制寄存器写入。因此,有必要合成其他控制寄存器通道的译出信息。

[0113]“魂芯”处理器的统一地址空间中设置有32位dma传输模式控制寄存器(参照表1),本实施例采用连续的2个保留位(第15和第14位),分别作为一条指令完成二维数据传输dma设置位和一条指令完成二维数据清零dma设置位,如表6所示。

[0114]

15采用一条指令完成二维数据传输的dma设置位1’b1:有效,1’b0:无效14采用一条指令完成二维数据清零的dma设置位1’b1:有效,1’b0:无效

[0115]

表6

[0116]“魂芯”处理器采用多级流水线同步时钟设计,在流水线执行时,每个指令行的指令都是在1个时钟周期内执行完成的。由于dma二维传输/清零指令所涉及的8/5个控制寄存器的已经在同一条指令中,因此,处理器流水线执行时,该条指令对dma配置的8/5个控制寄存器的写操作在同一周期内执行完成。

[0117]

实施例2

[0118]

一种基于实施例1所述的dma二维数据传输/清零参数配置方法的dma二维数据传输/清零方法,核内dma控制器识别dma传输模式控制寄存器的二维数据传输dma设置位和二维数据清零dma设置位。

[0119]

实施例1中,将dma传输模式控制寄存器的第15位作为一条指令完成二维数据传输dma设置位,第14位作为一条指令完成二维数据清零dma设置位。因此,当两个位段的值为2’b10,即第15位值为1,第14位值为0,则自动启动dma二维数据传输,直至数据传输结束;当两

个位段的值为2’b01,即第15位值为0,第14位值为1,则自动启动dma二维数据清零,直至数据清零结束。

[0120]

结合实施例1中,隐含的第2种含义,当指令机器码中的操作op-code和模式位均对应dma二维数据传输指令,则配置dma传输模式控制寄存器的第15位为1,第14位为0,继而自动启动dma二维数据传输;当指令机器码中的操作op-code和模式位均对应dma二维数据清零指令,则配置dma传输模式控制寄存器的第15位为0,第14位为1,继而自动启动dma二维数据清零。因此,此处的dma二维数据传输/清零都是自动启动,无需如背景技术l11,需要单独设置dma传输启动控制寄存器。

[0121]

实施例3

[0122]

用户采用“魂芯”指令集编写汇编程序,其中二维dma数据传输/清零指令采用实施例1公开的指令形式进行编写,每个指令行512位,可以并行多条32/64位指令。

[0123]

汇编程序通过软件汇编工具链及软件规则检查器,检查指令编写是否符合汇编指令书写规则要求。二维dma数据传输/清零指令的检查项目为:1、参数p,n,m,w是否符合位宽要求;2、控制寄存器占用通道总数是否符合要求;3、针对二维dma数据传输指令,检查n*m能否被p整除,若不能整除,则报错。汇编程序经过汇编工具链得到硬件输入机器码。

[0124]

二维dma数据传输/清零指令功能涉及到的硬件电路主要包括程序存储、指令catch、指令取指、指令译码、指令执行多个流水线处理模块,其中程序存储模块、指令catch模块、指令取指模块与其他双字指令处理方式相同,不在本发明核心创新点之列,在此不再赘述,本发明主要涉及指令译码模块和指令执行模块。

[0125]

一种dma二维数据传输/清零指令译码器,由指令通道分配单元、指令识别单元、指令输出单元、条件受控单元、dma译码单元、控制信号合成单元组成,如图1所示。

[0126]

所述指令通道分配单元,用于根据输入的指令进行通道分配,dma二维数据传输/清零指令占用8/5个控制寄存器写通道,分别为4/2个通用寄存器访问控制寄存器通道和4/3个立即数访问控制寄存器通道。

[0127]

所述指令识别单元,用于识别指令行中的dma二维数据传输/清零指令,当指令行中含有dma二维数据传输/清零指令时,识别其中的操作码,并输出dma二维传输/清零的标志信息。

[0128]

所述指令输出单元,用于监测到dma二维传输/清零的标志信息,通过选择器选出对应的dma二维数据传输/清零指令,输出至dma译码单元。

[0129]

所述条件受控单元,用于根据谓词条件判断的输入,通过逻辑判断得到dma二维数据传输/清零指令的条件受控使能结果,输出至dma译码单元。

[0130]

所述dma译码单元,用于通过dma二维数据传输/清零指令,结合谓词条件受控使能输入,译出dma控制寄存器配置信息。

[0131]

所述控制信号合成单元,用于对dma二维数据传输/清零指令的译出信息与其他控制寄存器通道的译出信息进行合成,输出dma控制寄存器的全部配置信息,完成dma二维数据传输/清零指令译码。

[0132]

显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。