1.本发明属于模拟集成电路参数优化技术领域,涉及基于机器学习的模拟集成电路的设计参数优化领域,特别涉及一种模拟集成电路参数优化方法及系统。

背景技术:

2.随着工艺节点的进步与电源电压的降低,模拟集成电路的非理想响应显著增加,使得电路的设计愈发具有挑战性,也愈发费时费力。在产品周期的压力及需求下,模拟集成电路的自动化设计愈发受到人们的关注。

3.随着人工智能的发展与计算资源的提升,基于机器学习的模拟集成电路参数优化方法近些年来受到了广泛的关注;当下基于机器学习的模拟集成电路优化方法是将电路设计参数优化的问题转为最优化问题,即将电路视作一个黑盒函数,将设计参数输入到电路仿真器中后,基于电路仿真器的输出进而调整输入值,达到不断提升电路性能的目的;示例性的,已被应用的算法有贝叶斯优化、深度强化学习、遗传算法、粒子群算法、模拟退火等。

4.然而,已有的技术中采取的均是直接优化晶体管的宽度与长度的方式;由于晶体管的宽度、长度与电路性能之间的关系是间接、非线性的,故直接优化晶体管宽度与长度的方式效率十分低下,在复杂电路优化任务中优化算法也难以收敛。

技术实现要素:

5.本发明的目的在于提供一种模拟集成电路参数优化方法及系统,以解决上述存在的一个或多个技术问题。本发明的方法相当于在电路的特征空间对电路进行优化,能够显著提高算法的优化效果与加速收敛速度。

6.为达到上述目的,本发明采用以下技术方案:

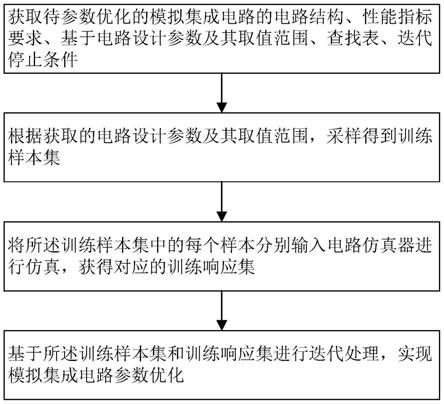

7.本发明提供的一种模拟集成电路参数优化方法,包括以下步骤:

8.获取待参数优化的模拟集成电路的电路结构、性能指标要求、基于gm/id设计方法学的电路设计参数及其取值范围、id/w-gm/id查找表、迭代停止条件;其中,w为晶体管宽度值,gm为晶体管的跨导,id为晶体管的沟道电流,id/w的物理含义为电流密度,gm/id的物理含义为跨导效率;

9.根据获取的所述基于gm/id设计方法学的电路设计参数及其取值范围,采样得到训练样本集,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流;

10.基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值后,将各个样本中所有晶体管的宽度值、沟道长度分别代入电路仿真器中进行电路仿真,获得对应的训练响应集;

11.基于所述训练样本集和训练响应集进行迭代处理,实现模拟集成电路参数优化;

12.其中,所述迭代处理的每一轮迭代包括:

13.采用预设启发式优化算法输出若干个样本,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流;

14.基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值;

15.将各个样本中所有晶体管的宽度值、长度值分别代入电路仿真器中进行电路仿真,获得样本响应;其中,若样本响应达到性能指标要求或满足迭代停止条件,则退出迭代,否则更新训练样本集和训练响应集进入下一轮迭代。

16.本发明方法的进一步改进在于,所述基于gm/id设计方法学的电路设计参数及其取值范围中,电路设计参数包括晶体管的沟道电流、gm/id值和沟道长度。

17.本发明方法的进一步改进在于,所述预设启发式优化算法为贝叶斯优化方法或nsga-ii算法。

18.本发明方法的进一步改进在于,所述基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值的步骤具体包括:

19.对于每个样本中的每个晶体管,基于id/w-gm/id查找表进行查表操作,获得电流密度;通过沟道电流除以电流密度,获得晶体管的宽度值。

20.本发明方法的进一步改进在于,所述否则更新训练样本集和训练相应集进入下一轮迭代的步骤具体包括:

21.将采用预设启发式优化算法输出的若干个样本与训练样本集合并,获得更新后的训练样本集;将采用预设启发式优化算法输出的若干个样本对应的样本响应与训练响应集合并,获得更新后的训练响应集。

22.本发明提供的一种模拟集成电路参数优化系统,包括:

23.初始化模块,用于获取待参数优化的模拟集成电路的电路结构、性能指标要求、基于gm/id设计方法学的电路设计参数及其取值范围、id/w-gm/id查找表、迭代停止条件;其中,w为晶体管宽度值,gm为晶体管的跨导,id为晶体管的沟道电流,id/w的物理含义为电流密度,gm/id的物理含义为跨导效率;

24.训练样本集获取模块,用于根据获取的所述基于gm/id设计方法学的电路设计参数及其取值范围,采样得到训练样本集,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流;

25.训练响应集获取模块,基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值后,将各个样本中所有晶体管的宽度值、沟道长度分别代入电路仿真器中进行电路仿真,获得对应的训练响应集;

26.参数优化模块,用于基于所述训练样本集和训练响应集进行迭代处理,实现模拟集成电路参数优化;

27.其中,所述迭代处理的每一轮迭代包括:

28.采用预设启发式优化算法输出若干个样本,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流;

29.基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值;

30.将各个样本中所有晶体管的宽度值、长度值分别代入电路仿真器中进行电路仿真,获得样本响应;其中,若样本响应达到性能指标要求或满足迭代停止条件,则退出迭代,否则更新训练样本集和训练响应集进入下一轮迭代。

31.本发明系统的进一步改进在于,所述基于gm/id设计方法学的电路设计参数及其取值范围中,电路设计参数包括晶体管的沟道电流、gm/id值和沟道长度。

32.本发明系统的进一步改进在于,所述预设启发式优化算法为贝叶斯优化方法或nsga-ii算法。

33.本发明系统的进一步改进在于,所述基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值的步骤具体包括:对于每个样本中的每个晶体管,基于id/w-gm/id查找表进行查表操作,获得电流密度;通过沟道电流除以电流密度,获得晶体管的宽度值。

34.本发明系统的进一步改进在于,所述否则更新训练样本集和训练相应集进入下一轮迭代的步骤具体包括:将采用预设启发式优化算法输出的若干个样本与训练样本集合并,获得更新后的训练样本集;将采用预设启发式优化算法输出的若干个样本对应的样本响应与训练响应集合并,获得更新后的训练响应集。

35.与现有技术相比,本发明具有以下有益效果:

36.本发明中,结合模拟集成电路gm/id设计方法学提出了一套优化算法,可显著提高算法的优化效果与加速收敛速度;需要指出的是,本发明提出的基于gm/id的优化方法不需要额外的专家知识。具体解释性的,相较已有方法,本发明方法最显著的特点是改变了电路设计参数的搜索空间,即不再是直接优化晶体管的宽度与长度,而是晶体管的gm/id值、沟道电流与沟道长度,进而通过id/w-gm/id查找表得到晶体管的电流密度,通过电流密度与沟道电流计算得到最终的晶体管宽度(其中,w为晶体管的宽度,gm为晶体管的跨导,id为晶体管的沟道电流,id/w的物理含义为电流密度,gm/id的物理含义为跨导效率);由于gm、id与gm/id在电路设计中有明确的物理含义,故而这种方法相当于在电路的特征空间对电路进行优化,可以显著提高算法的优化效果与加速收敛速度。

附图说明

37.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面对实施例或现有技术描述中所需要使用的附图做简单的介绍;显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来说,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

38.图1是本发明实施例的一种基于gm/id方法学的模拟集成电路参数优化方法的流程示意框图;

39.图2是本发明实施例针对单目标优化的实施例,为折叠式共源共栅放大器示意图;

40.图3是本发明实施例中,针对单目标优化的优化结果示意图;

41.图4是本发明实施例针对多目标优化的实施例,为两级放大器电路示意图;

42.图5是本发明实施例中,针对多目标优化的优化结果示意图。

具体实施方式

43.为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

44.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

45.下面结合附图对本发明做进一步详细描述:

46.请参阅图1,本发明实施例提供的一种模拟集成电路的参数优化方法,具体是一种基于gm/id方法学的模拟集成电路参数自动化优化方法,包括以下步骤:

47.获取待参数优化的模拟集成电路的电路结构、性能指标要求、基于gm/id设计方法学的电路设计参数(即各晶体管的沟道电流、gm/id值、沟道长度)及其取值范围、id/w-gm/id查找表、迭代停止条件;示例性解释的,id/w-gm/id查找表是根据gm/id设计方法学提前生成的,在此不再赘述;

48.基于获取的设计参数及其取值范围,采样得到训练样本集;

49.基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值,将各个样本中所有晶体管的宽度值、长度值分别代入电路仿真器中进行电路仿真,获得对应的训练响应集;

50.完成了上述训练样本集与训练响应集的获取后,进入迭代过程:

51.(1)在每次迭代时,采用预设启发式优化算法输出一个新的样本x

t

或若干个样本x

t

。每个样本均包括预设数量的晶体管长度值、gm/id值、沟道电流;

52.(2)获取每一个晶体管的宽度值;示例性的,对x

t

或x

t

中的每一个晶体管进行查找表操作,获得电流密度;第i个晶体管的电流密度(id/w)i通过id/w-gm/id查找表得到,对应的宽度wi通过电流除以电流密度(id/w)i得到;

53.(3)将查找表后得到的晶体管宽度与及x

t

或x

t

中的对应的长度代入电路仿真器中进行电路仿真,进而得到其响应y

t

或y

t

。样本的响应;该响应值达到了性能指标的要求或满足迭代停止条件,则退出迭代,否则更新训练样本,进入下一轮迭代。具体示例性的,对y

t

或y

t

中每一个样本判断,是否达到电路的指标要求。若达到指标要求,则终止迭代。若未达到指标要求,则将x

t

或x

t

与原始训练样本集合并构成新的训练样本集,将y

t

或y

t

与原始训练响应集合并构成新的训练响应集。

54.本发明实施例提供的方法具有的显著进步总结为:其一,由于gm、id与gm/id在电路设计中有明确的物理含义,故而本发明提出的这种方法相当于在电路的特征空间对电路进行优化后再变换到原始空间,故而取得的效果更佳显著;其二、gm/id取值大约为4~25(具体值与工艺有关),具有天然的归一化属性,有利于算法的处理;其三,gm、id与gm/id在电路设计中有明确的物理含义,故而可以根据电路性能指标,通过限制设计参数搜索范围,更直接的对电路优化加以约束,加快收敛速度;其四,在gm/id设计方法学中,电路的偏置电路的设计是基于规则的,故而降低了优化变量的维度,一定程度缓解了维数灾难。

55.本发明实施例提供参数优化方法的具体阐述如下:

56.1.实验设定步骤s1:给定待优化电路结构、电路的指标要求、基于gm/id设计方法

学的电路设计参数电路设计参数(即各晶体管的沟道电流、gm/id值、沟道长度)及其取值范围、迭代停止条件。

57.2.初始化步骤s2:初始化n个样本,构成训练样本集x=[x1,x2,...xi,...xn],xi代表第i个样本,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流。基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值,将各个样本中所有晶体管的宽度值、长度值分别代入电路仿真器中进行电路仿真,得到训练样本集x的训练响应集y,y为各指标的打分结果,用于评价每个指标的好坏。其中,x为n

×

d维的矩阵,y为n

×

k的矩阵,d代表设计变量的维度,k代表电路指标的个数,x中的每一个元素包含了电路中每一个晶体管的gm/id值、长度与值与id值。此后进入迭代步骤s3至s6,每一次迭代产生一个新的样本x

t

或若干样本x

t

,与新的样本对应的响应y

t

或y

t

,故而样本集x与y随着迭代进行不断的扩充。

[0058]

3.算法输出步骤s3:在第t次迭代时,优化算法输出一个新的样本x

t

或若干个样本x

t

。

[0059]

4.查找表步骤s4:对x

t

或x

t

中的每一个晶体管进行查找表操作,通过gm/id值、长度值与id值得到对应的宽度值。第i个晶体管的电流密度(id/w)i通过id/w-gm/id查找表得到,如公式(1)所示,对应的的宽度wi通过电流除以电流密度(id/w)i得到。

[0060]

(id/w)i=f

lut

(gm/i

di

,li)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0061][0062]

其中,f

lut

(

·

)代表查找表操作,l为对应晶体管的长度,查找表操作是gm/id设计方法学的基础操作,在此不在赘述。

[0063]

5.仿真评估步骤s5:将步骤s4查找表后得到的晶体管宽度及x

t

或x

t

中的对应的长度代入仿真器中进行电路仿真,进而得到其响应y

t

或y

t

。

[0064]

6.迭代判断步骤s6:对y

t

或y

t

中每一个样本判断,是否达到电路的指标要求。若达到指标要求,则终止迭代。若未达到指标要求,则x

t

或x

t

与原训练样本集x合并,y

t

与y

t

与原训练响应集y合并,返回步骤s3继续迭代。

[0065]

具体实施例1,基于本发明实施例提出的优化方法框架,采用贝叶斯优化算法对图1中的实施例进行参数优化。

[0066]

请参阅图2和图3,图2中以折叠式共源共栅放大器为例,包括主支路与偏置电路,该放大器的电源电压为1.8v,其负载为10pf的电容。

[0067]

本发明实施例采用贝叶斯优化方法,基于gm/id模拟集成电路参数的单目标自动优化方法,该优化方法为迭代执行的方式,包括以下步骤:实验设定步骤s1、初始化步骤s2、算法输出步骤s3、查找表步骤s4、仿真评估步骤s5、迭代判断步骤s6。其中步骤s3至步骤s5迭代执行,每次迭代后,步骤s3输出一组设计变量,步骤s5来判断该设计变量是否达到电路指标要求,进而选择是否退出迭代步骤。

[0068]

实验设定步骤s1:1)给定电路结构如图2所示;2)给定电路指标要求:电路指标要求由公式(3)描述,其中iq为静态电路,gain为直流增益,ugb为单位增益带宽,no为输出噪声,sr为压摆率,psrr为电源抑制比。期望iq越小越小,其余指标只需大于或小于某一个阈值即可,具体数值大小如公式(3)所述;3)基于gm/id设计方法学的电路设计参数电路设计

参数及其取值范围:考虑到电路的匹配性,本实施例中待设计参数有13个,每个晶体管的gm/id的宽度取值范围为4~25,长度的取值范围位0.18um-4um,每条支路的电流的取值范围为小于100ua。4)给定迭代停止条件:迭代200次停止。

[0069]

minimize iq[0070]

s.t.iq《100ua

[0071]

gain》60db

[0072]

ugb》1mhz

[0073]

sr》10v/us

[0074]

no《350uv/sqrt(hz)@1khz

[0075]

psrr》60db≤1khz

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0076]

初始化步骤s2:随机采样30个样本,构成训练样本集x,由于该电路设计参数数目为13,因此x为30

×

13的矩阵。通过hspice进行电路仿真,得到仿真结果后进行打分得到训练响应集y。由于考虑的电路指标有6个,y为30

×

6的矩阵。打分按照公式(4)所述。

[0077][0078]

其中,qc用于表征每一个指标的好坏,wi为每一项的权重,默认值为1。下面阐述qc的计算方式。对于某一指标c,若期望该指标需要大于某一阈值,qc由公式(5)计算;若期望该指标需要小于某一阈值,由公式(6)计算。若期望该指标越大越好,qc由(7)式计算,若期望该指标越小越好,由(8)式计算。

[0079][0080][0081][0082][0083]

其中mc为电路仿真后的指标大小,为该指标期望值。需要指出的是,对于(7)式与(8)式对应的指标,当其未达到指标要求前,该指标的qc由(5)或(6)来计算,当其达到指标要求后,该指标的qc由(7)或(8)来计算。

[0084]

算法输出步骤s3:在第t次迭代时,贝叶斯优化算法根据历史数据点训练样本集x与训练响应集y构建高斯过程,最大化采集函数后输出一个最具潜力的样本点x

t

。高斯过程的构建与最大化采集函数是贝叶斯优化领域内的通用步骤,在此不在赘述。

[0085]

查找表操作s4:对x

t

中的每一个晶体管进行查找表操作,通过gm/id值、长度与值与id值得到对应的宽度值。第i个晶体管的电流密度(id/w)i通过id/w-gm/id查找表得到,如公式(1)所示,对应的宽度wi通过电流除以电流密度(id/w)i得到,如公式(2)所述。id/w-gm/id查找表是根据gm/id设计方法学提前生成的,在此不再赘述。

[0086]

仿真评估步骤s5:将步骤s4查找表后得到的晶体管宽度及x

t

中的每一个晶体管的长度代入仿真器中进行电路仿真,进而得到其响应y

t

。

[0087]

迭代判断步骤s6:判断迭代是否进行了200次,若到达200次则终止迭代,否则返回步骤s3继续迭代。则x

t

与原训练样本集x合并,y

t

与原训练响应集y合并,返回步骤s3继续迭

代。

[0088]

由于算法具有随机性,故而将实验重复进行了10次,将实验结果求平均,绘制学习曲线如图3所示,横坐标为迭代次数,纵坐标为fom值。由于本实施例有6个指标,因此黑色虚线(y=6.0)可以用于判断优化是否满足指标要求。从图3可以看出,当搜索变量为gm/id时,无论初始化结果还是最终的得分都显著提高。

[0089]

具体实施例2,基于本发明提出的优化方法框架,采用nsga-ii算法的多目标优化方法实施例。请参阅图4和图5,图4中以两级放大器为例,包括主支路、偏置电路与补偿网络,该放大器的电源电压为1.8v,其负载为10pf的电容。

[0090]

本发明实施例的采用nsga-ii算法、基于gm/id模拟集成电路参数的单目标自动优化方法,该优化方法为迭代执行的方式,包括以下步骤:实验设定步骤s1、初始化步骤s2、算法输出步骤s3、查找表步骤s4、仿真评估步骤s5、迭代判断步骤s6。其中步骤s3至步骤s5迭代执行,每次迭代后,步骤s3输出一组设计变量,步骤s5来判断该设计变量是否达到电路指标要求,进而选择是否退出迭代步骤。

[0091]

实验设定步骤s1:1)给定电路结构如图4所示;2)给定电路指标要求如公式(9)所示,其中iq为静态电路,gain为直流增益,ugb为单位增益带宽,pm为相位裕度。即要求最大化增益、最大化单位增益带宽、最小化电流,限制相位裕度在52.5度以内。3)基于gm/id设计方法学的电路设计参数电路设计参数及其取值范围:考虑到电路的匹配性,本实施例中待设计参数有12个,每个晶体管的gm/id的宽度取值范围为4~25,长度的取值范围位0.18um-4um,每条支路的电流的取值范围小于200ua。4)给定迭代停止条件:迭代30代后停止。

[0092]

maximize(gain,ugb,-iq)

[0093]

s.t.pm》52.5

°ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(9)

[0094]

初始化步骤s2:设定种群大小为50,对种群随机初始化,构成训练样本集x,由于该电路设计参数数目为12,因此x为30

×

12的矩阵。对x中,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流,基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值,将各个样本中所有晶体管的宽度值、沟道长度值分别代入电路仿真器中进行电路仿真,得到对应的性能指标响应集y。

[0095]

算法输出步骤s3:在第t次迭代时,nsga-ii算法进行交叉、变异与选择操作,种群完成进化,得到新的训练样本集xt。行交叉、变异与选择操作是多目标优化领域内的通用步骤,在此不再赘述。

[0096]

查找表步骤s4:对x

t

中的每一个晶体管进行查找表操作,通过gm/id值、长度与值与id值得到对应的宽度值。第i个晶体管的电流密度(id/w)i通过id/w-gm/id查找表得到,如公式(1)所示,对应的宽度wi通过电流除以电流密度(id/w)i得到,如公式(2)所述。id/w-gm/id查找表是根据gm/id设计方法学提前生成的,在此不再赘述。

[0097]

仿真评估步骤s5:将步骤s4查找表后得到的晶体管宽度及x

t

中的每一个晶体管的长度代入仿真器中进行电路仿真,进而得到其响应集y

t

。

[0098]

迭代判断步骤s6:判断种群是否迭代是否进行了30次,若到达30次则终止迭代,否则返回步骤s3继续迭代。

[0099]

实验重复进行了5次,将找到的帕累托前沿绘制到了图5中,图例中,gm/id表示优化变量为gm/id,w表示优化变量为宽度。从图5可以看出,本框架中找到的帕累托前沿(三角

形点集)分布更广且更均匀,明显优秀直接优化晶体管宽度得到的帕累托前沿(五角星点集)。

[0100]

下述为本发明的装置实施例,可以用于执行本发明方法实施例。对于装置实施例中未纰漏的细节,请参照本发明方法实施例。

[0101]

本发明再一实施例中,本发明实施例提供的一种模拟集成电路参数优化系统,包括:

[0102]

初始化模块,用于获取待参数优化的模拟集成电路的电路结构、性能指标要求、基于gm/id设计方法学的电路设计参数及其取值范围、id/w-gm/id查找表、迭代停止条件;其中,w为晶体管宽度值,gm为晶体管的跨导,id为晶体管的沟道电流,id/w的物理含义为电流密度,gm/id的物理含义为跨导效率;

[0103]

训练样本集获取模块,用于根据获取的所述基于gm/id设计方法学的电路设计参数及其取值范围,采样得到训练样本集;

[0104]

训练响应集获取模块,用于将所述训练样本集中的每个样本分别输入电路仿真器进行仿真,获得对应的训练响应集;

[0105]

参数优化模块,用于基于所述训练样本集和训练响应集进行迭代处理,实现模拟集成电路参数优化;

[0106]

其中,所述迭代处理的每一轮迭代包括:

[0107]

采用预设启发式优化算法输出若干个样本,每个样本均包括若干个晶体管的沟道长度、gm/id值、沟道电流;

[0108]

基于id/w-gm/id查找表进行查表并计算,获取每个样本中每个晶体管的宽度值;

[0109]

将各个样本中所有晶体管的宽度值、长度值分别代入电路仿真器中进行电路仿真,获得样本响应;其中,若样本响应达到性能指标要求或满足迭代停止条件,则退出迭代,否则更新训练样本集和训练响应集进入下一轮迭代。

[0110]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0111]

本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0112]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0113]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计

算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0114]

最后应当说明的是:以上实施例仅用以说明本发明的技术方案而非对其限制,尽管参照上述实施例对本发明进行了详细的说明,所属领域的普通技术人员应当理解:依然可以对本发明的具体实施方式进行修改或者等同替换,而未脱离本发明精神和范围的任何修改或者等同替换,其均应涵盖在本发明的权利要求保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。