1.本发明属于运用fpga pcie加速标准板卡对数据进行加密解密的技术领域,尤其涉及一种基于主控加速引擎的加密存储卡固件设计方法。

背景技术:

2.随着信息产业的飞速发展,硬盘由于容量大、使用方便,逐渐成为人们存储信息的主要介质,同时也带来了另外一个重大问题——信息安全。对信息加密有两种方式,软件加密和硬件加密。软件加密耗费cpu和内存,且速度慢、安全性不高;硬件加密速度快、安全性高。

3.传统的计算机加解密方法均是运用cpu资源对数据进行加解密,其最大的缺点:一方面是效率低,消耗cpu的计算资源过多;另一方面是速率上不去,最高速率测试到15gb/s,而用fpga pcie加速标准板卡最大可以做到60gb/s,效率提了300%,在一些大数据,低延迟场合非常适合应用。

技术实现要素:

4.本发明提供一种基于主控加速引擎的加密存储卡固件设计方法,旨在解决传统的计算机加解密方法通过运用cpu资源对数据进行加解密导致效率低,消耗cpu的计算资源过多,同时速率上不去,最高速率测试到15gb/s的问题。

5.本发明是这样实现的,一种基于主控加速引擎的加密存储卡固件设计方法,包括如下步骤:

6.步骤s1:在pc或服务器pcie插槽插入一个或者多个fpga pcie加速标准板卡;

7.步骤s2:pc或者服务器内的cpu与fpga pcie加速标准板卡内的dma 控制器相连接;

8.步骤s3:在数据加解密时,cpu将需要加解密处理的数据进行分类编号后,移交给fpga pcie加速标准板卡进行处理;

9.步骤s4:该fpga pcie加速标准板卡中的dma控制器对数据进行加解密;

10.步骤s5:数据加解密完成时,fpga pcie加速标准板卡中的dma控制器将加解密的结果反馈给cpu,并由cpu检查操作和读取加解密完成后的数据进行后续数据处理操作,

11.其中,cpu负责管理fpga pcie加速标准板卡,具体的加解密计算开销由fpga pcie加速标准板卡来完成,fpga pcie加速标准板卡随时向cpu报告状态进度情况。

12.优选的,在步骤s1中的fpga pcie加速标准板卡架构为fpga: xcvu13p(3780k cells),

13.ddr43200mhz 4gb*4,

14.pcie:pcie gen3.0*16。

15.优选的,在步骤s3中包括如下步骤:

16.步骤s31、cpu判断数据需要处理的类型;

17.步骤s32、cpu对数据分类并编号排序;

18.步骤s33、cpu将需要处理的数据发送给fpga pcie加速标准板卡,并由 fpga pcie加速标准板卡中的dma控制器作具体处理;

19.步骤s34、fpga pcie加速标准板卡中的dma控制器将同一个大数据包进行分包切割,分成若干个小数据包并按照切割顺序进行逐个编号;

20.步骤s35、fpga pcie加速标准板中的各个核心同步对上述若干个小数据包进行逐个的加解密处理,每个核心处理完一个小数据包后自动分配下一个小数据包直至所有的小数据包全部处理完成。

21.优选的,在步骤s32中进一步包括如下步骤:

22.步骤s321、cpu将数据按照加密数据或者解密数据进行分类;

23.步骤s322、cpu对同一个类型中的数据进行编号并排序。

24.优选的,在步骤s4中包括如下细分步骤:

25.步骤s41、dma控制器按照先加密后解密的顺序对两个类型的数据进行处理;

26.步骤s42、dma控制器在同一个类型内按照编号顺序进行逐个的解密;

27.步骤s43、dma控制器按照编号顺序将各个加解密完成的小数据包进行组合形成大数据包。

28.优选的,在步骤s5中包括如下步骤:

29.步骤s51、fpga pcie加速标准板卡中的dma控制器将加解密的结果反馈给cpu;

30.步骤s52、cpu检查dma控制器的加解密操作是否合规;

31.步骤s53、cpu读取加解密完成后的大数据包进行后续数据操作。

32.优选的,在步骤s52中cpu检查dma控制器的加解密操作是否合规;

33.若合规,则cpu读取加解密完成后的数据进行后续操作;

34.若不合规,则cpu对该数据进行重新的加解密操作。

35.优选的,fpga pcie加速标准板卡内部搭载有用于对数据进行加密或者解密的驱动和软件。

36.与现有技术相比,本发明的有益效果是:本发明的一种基于主控加速引擎的加密存储卡固件设计方法,本技术通过在pc或服务器的pcie插槽插入一个或者多个fpga pcie加速标准板卡,通过fpga pcie加速标准板卡内部的驱动和软件把本来要在cpu计算的数据移动这个fpga pcie加速标准板卡做计算,从而cpu负责管理fpga pcie加速标准板卡,具体的加解密计算开销由 fpga pcie加速标准板卡来完成,fpga pcie加速标准板卡随时向cpu报告状态进度情况,把cpu的计算资源释放出来,去做其它的事情,这样就可以克服传统的计算机加解密方法效率低,消耗cpu的计算资源过多,速率上不去的问题了,由于传动的采用cpu的加解密最高速率测试到15gb/s,而用fpgapcie加速标准板卡最大可以做到60gb/s,效率提了300%,在一些大数据,低延迟场合非常适合应用,整个的设置解放了cpu,增加cpu的运行效率以及提高加解密的速度。

附图说明

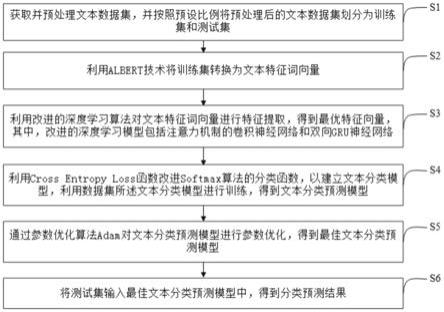

37.图1为本发明的步骤示意图;

38.图2为本发明中fpga pcie加速标准板卡工作原理拓扑图;

具体实施方式

39.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

40.请参阅图1-2,本发明提供一种技术方案:一种基于主控加速引擎的加密存储卡固件设计方法,包括如下步骤:

41.步骤s1:在pc或服务器pcie插槽插入一个或者多个fpga pcie加速标准板卡;

42.步骤s2:pc或者服务器内的cpu与fpga pcie加速标准板卡内的dma 控制器相连接;

43.步骤s3:在数据加解密时,cpu将需要加解密处理的数据进行分类编号后,移交给fpga pcie加速标准板卡进行处理;

44.步骤s4:该fpga pcie加速标准板卡中的dma控制器对数据进行加解密;

45.步骤s5:数据加解密完成时,fpga pcie加速标准板卡中的dma控制器将加解密的结果反馈给cpu,并由cpu检查操作和读取加解密完成后的数据进行后续数据处理操作,

46.其中,cpu负责管理fpga pcie加速标准板卡,具体的加解密计算开销由fpga pcie加速标准板卡来完成,fpga pcie加速标准板卡随时向cpu报告状态进度情况。

47.在本实施方式中,首先将一个或者多个fpga pcie加速标准板卡插入在 pc或服务器pcie插槽上,然后pc或服务器内部的cpu与fpga pcie加速标准板卡内部的dma控制器相连接配合,完成fpga pcie加速标准板卡的加载和初始化过程。

48.在数据需要加密时,cpu先对数据按照加密类型进行分类,并对数据包进行编号排序,之后将数据包转发交给fpga pcie加速标准板卡,该fpga pcie 加速标准板卡内的dma控制器接收待处理的数据包,并对cpu分配好的需要加密的大数据包按照顺序对其进行切割分包,形成一个个小数据包并按照分割顺序进行编号,再将一个个小数据包按照编号顺序分配给fpga pcie加速标准板卡中的各个核心进行逐个小数据包的加密,fpga pcie加速标准板卡中的各个核心通过内部的加密算法对各个小数据包进行加密的操作,当各个小数据包全部加密完成后,dma控制器再将各个小数据按照编号顺序重新合在一起组成一个个大数据包,之后dma控制器将加密结果反馈给cpu,cpu对加密过程进行检查,若检查出问题,则由cpu重新进行加密,若检查一切正常,则由 cpu对加密完成的数据包进行读取,再进行后续的数据操作。

49.在数据需要解密时,cpu先对数据按照解密类型进行分类,并对数据包进行编号排序,之后将数据包转发交给fpga pcie加速标准板卡,该fpga pcie 加速标准板卡内的dma控制器接收待处理的数据包,并对cpu分配好的需要解密的大数据包按照顺序对其进行切割分包,形成一个个小数据包并按照分割顺序进行编号,再将一个个小数据包按照编号顺序分配给fpga pcie加速标准板卡中的各个核心进行逐个小数据包的解密,fpga pcie加速标准板卡中的各个核心通过内部的解密算法对各个小数据包进行解密的操作,当各个小数据包全部解密完成后,dma控制器再将各个小数据按照编号顺序重新合在一起组成一个个大数据包,之后dma控制器将解密结果反馈给cpu,cpu对解密过程进行检查,若检查出问题,则由cpu重新进行解密,若检查一切正常,则由 cpu对解密完成的数据包进行读取,再进行后续的数据操作

50.在步骤s1中的fpgapcie加速标准板卡架构为fpga:xcvu13p(3780kcells),

51.ddr43200mhz4gb*4,

52.pcie:pciegen3.0*16。

53.在本实施方式中,根据实际计算,单个通道的计算速度是3.2gb/s,故将运用算法将fpga分成16个核来处理加解密,3.2gb*16=51.2gb速率;同时接口采用的是pciegen3*16,故接口速率:8gb*16=128gb/s,也完全符合速率要求,pcie接口数据采用最新的以保证数据传输的速率。

54.在步骤s3中包括如下步骤:

55.步骤s31、cpu判断数据需要处理的类型;

56.步骤s32、cpu对数据分类并编号排序;

57.步骤s33、cpu将需要处理的数据发送给fpgapcie加速标准板卡,并由fpgapcie加速标准板卡中的dma控制器作具体处理;

58.步骤s34、fpgapcie加速标准板卡中的dma控制器将同一个大数据包进行分包切割,分成若干个小数据包并按照切割顺序进行逐个编号;

59.步骤s35、fpgapcie加速标准板中的各个核心同步对上述若干个小数据包进行逐个的加解密处理,每个核心或者线程处理完一个小数据包后自动分配下一个小数据包直至所有的小数据包全部处理完成。

60.在本实施方式中,cpu对需要处理的数据按照加密、解密分为两大类,且在每个类型中按照加密的方式和解密的方式对其进行进一步的分类,并在同一类型中进行编号排序,通过类型将数据放好,之后cpu将待处理的数据包移交给dma控制器,dma控制器将大数据包按照编号顺序进行逐个的切割分包,形成各个小数据包,并对各个小数据包进行编号,之后逐个的分配给fpgapcie加速标准板卡中各个核心,fpgapcie加速标准板卡中各个核心对各个小数据包进行同步的处理,最后将各个小数据包处理的结果按照编号顺序重新进行合并形成大数据包,从而得到加密或者解密的结果。

61.在步骤s4中包括如下细分步骤:

62.步骤s41、dma控制器按照先加密后解密的顺序对两个类型的数据进行处理;

63.步骤s42、dma控制器在同一个类型内按照编号顺序进行逐个的解密;

64.步骤s43、dma控制器按照编号顺序将各个加解密完成的小数据包进行组合形成大数据包。

65.在本实施方式中,该dma控制器若加密和解密都有,则先通过内部的加密算法对数据进行加密,之后再通过解密算法对数据进行解密操作,若只有加密或者只有解密,则通过对应加密或者解密算法进行操作即可。

66.在步骤s5中包括如下步骤:

67.步骤s51、fpgapcie加速标准板卡中的dma控制器将加解密的结果反馈给cpu;

68.步骤s52、cpu检查dma控制器的加解密操作是否合规;

69.步骤s53、cpu读取加解密完成后的大文件数据包进行后续数据操作;

70.在本实施方式中,当解密完成后,dma控制器将数据加解密的结果反馈给cpu,cpu对加解密过程进行检查,若检查出问题,则由cpu重新进行加解密,若检查一切正常,则由cpu对加解密完成的大数据进行读取,之后对大数据包进行后续的操作。

71.fpga pcie加速标准板卡内部搭载有用于对数据进行加密或者解密的驱动和软件。

72.在本实施方式中,fpga pcie加速标准板卡内部搭载有用于对数据进行加密或者解密的驱动和软件,用于应对各种不同类型的加密或者解密的数据文件,保证对各种类型的文件均可以进行加解密,以帮助cpu进行分担压力。

73.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。