技术特征:

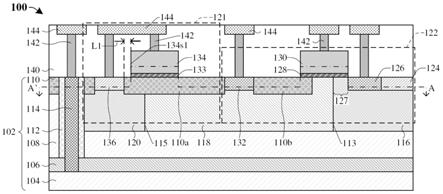

1.一种集成芯片,包括:半导体衬底,包括位于处理衬底上面的器件衬底以及设置在所述器件衬底和所述处理衬底之间的绝缘层;栅电极,位于漏极区域和源极区域之间的所述器件衬底上面;导电通孔,延伸穿过所述器件衬底和所述绝缘层以接触所述处理衬底;第一隔离结构,设置在所述器件衬底内并且包括横向设置在所述栅电极和所述导电通孔之间的第一隔离段;接触区域,设置在所述第一隔离段和所述导电通孔之间的所述器件衬底内;以及导电栅电极,直接位于所述第一隔离段上面,其中,所述导电栅电极电耦接至所述接触区域。2.根据权利要求1所述的集成芯片,还包括:第一阱区域,设置在所述器件衬底内;第二阱区域,设置在所述器件衬底内并且在第一界面处邻接所述第一阱区域,其中,所述第二阱区域包括第一掺杂类型,并且所述第一阱区域包括与所述第一掺杂类型相反的第二掺杂类型,并且其中,所述栅电极直接位于所述第一界面上面;以及第三阱区域,设置在所述器件衬底内并且在第二界面处邻接所述第二阱区域,其中,所述第三阱区域包括所述第二掺杂类型,并且其中,所述导电栅电极直接位于所述第二界面上面。3.根据权利要求2所述的集成芯片,其中,所述漏极区域设置在所述第二阱区域内,所述源极区域设置在所述第一阱区域内,并且所述接触区域设置在所述第三阱区域内,从而使得所述导电栅电极经由接触区域电耦接至所述第三阱区域。4.根据权利要求3所述的集成芯片,其中,所述源极区域和所述漏极区域包括所述第一掺杂类型,并且所述接触区域包括所述第二掺杂类型,其中,所述第一掺杂类型是p型,并且所述第二掺杂类型是n型。5.根据权利要求1所述的集成芯片,其中,所述第一隔离段从所述接触区域的侧壁连续延伸至所述漏极区域的侧壁,并且其中,所述导电栅电极横向间隔在所述第一隔离段的外部相对侧壁之间。6.根据权利要求1所述的集成芯片,其中,所述导电栅电极是环形的,并且横向围绕所述漏极区域和所述栅电极。7.根据权利要求6所述的集成芯片,其中,所述接触区域是环形的,从而使得所述接触区域包围所述导电栅电极。8.根据权利要求1所述的集成芯片,还包括:第二隔离结构,设置在所述器件衬底内并且横向围绕所述导电通孔,其中,所述第二隔离结构从所述器件衬底的顶面连续延伸至所述绝缘层的顶面。9.一种集成芯片,包括:器件衬底和处理衬底,所述器件衬底位于绝缘层上面并且所述处理衬底位于所述绝缘层下面;第一阱区域、第二阱区域和第三阱区域,设置在所述器件衬底内,其中,所述第二阱区域横向间隔在所述第一阱区域和所述第三阱区域之间;

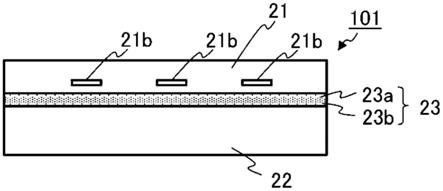

高压晶体管,设置在所述器件衬底上,包括栅电极、源极区域和漏极区域,其中,所述栅电极设置在所述源极区域和所述漏极区域之间,其中,所述栅电极直接位于所述第一阱区域和所述第二阱区域之间的第一界面上面;导电通孔,设置在所述器件衬底内并且电耦接至所述处理衬底,其中,所述导电通孔与所述第三阱区域相邻;以及导电终端结构,设置在所述导电通孔和所述高压晶体管之间的所述器件衬底上,其中,所述导电终端结构包括设置在所述第三阱区域内的接触区域以及位于所述第二阱区域和所述第三阱区域之间的第二界面上面的导电栅电极,其中,所述导电栅电极经由所述接触区域电耦接至所述第三阱区域。10.一种用于制造集成芯片的方法,所述方法包括:在器件衬底中形成第一隔离结构,其中,所述器件衬底位于绝缘层上面,并且处理衬底位于所述绝缘层下面;形成穿过所述器件衬底延伸至所述处理衬底的导电通孔;掺杂所述器件衬底以在所述器件衬底内形成第一阱区域、第二阱区域和第三阱区域,其中,所述第二阱区域横向间隔在所述第一阱区域和所述第三阱区域之间;在所述器件衬底上方形成栅电极,从而使得所述栅电极位于所述第一阱区域和所述第二阱区域之间的第一界面上面;在所述第一隔离结构上方形成导电栅电极;以及掺杂所述器件衬底以在所述器件衬底内形成源极区域、漏极区域和接触区域,其中,所述栅电极设置在所述源极区域和所述漏极区域之间,并且其中,所述接触区域设置在所述导电通孔和所述导电栅电极之间的所述第三阱区域内。

技术总结

本发明的各个实施例针对集成芯片。集成芯片包括:半导体衬底,具有位于处理衬底上面的器件衬底以及设置在器件衬底和处理衬底之间的绝缘层。栅电极位于漏极区域和源极区域之间的器件衬底上面。导电通孔延伸穿过器件衬底和绝缘层以接触处理衬底。第一隔离结构设置在器件衬底内并且包括横向设置在栅电极和导电通孔之间的第一隔离段。接触区域设置在第一隔离段和导电通孔之间的器件衬底内。导电栅电极直接位于第一隔离段上面并且电耦接至接触区域。本申请的实施例还涉及制造集成芯片的方法。本申请的实施例还涉及制造集成芯片的方法。本申请的实施例还涉及制造集成芯片的方法。

技术研发人员:蒋昕志 林东阳 柳瑞兴 雷明达

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:2022.01.11

技术公布日:2022/4/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。