1.本发明涉及定点数据截位处理技术领域,尤其是一种用于存算融合式处理器架构的定点数据动态截位方法。

背景技术:

2.数字信号处理(dsp)技术的不断发展,具有高速的数据处理能力和强大的指令系统,能够快速、实时地实现各种数字信号处理运算,在各个领域得到应用。定点dsp芯片相较于浮点dsp芯片,还具有价格较低、运算速度较快、占用内存单元较少等特点,应用更为广泛。

3.定点dsp芯片的处理器架构内部采用二进制补码表示数据,若不经过特殊处理,数据就是定点形式。在数字信号处理过程中,大量乘、加运算会导致数据位宽的增加,从而需要增加硬件逻辑单元数量,需要对数据进行截位。

4.目前,在定点数据截位电路中,为提高有效数据的精度,还需对截掉的尾数进一步进行舍入处理,而现有定点数据截位电路存在定点舍入模式单一的缺点。此外,现有的定点数据截位采用截取位宽固定的静态截位方式,当截取位宽需要根据需求变化时,便无法满足需求,存在不具有可扩展性、通用性低的缺点。

技术实现要素:

5.针对现有定点数据截位处理方式存在的上述问题,本发明提供了一种用于存算融合式处理器架构的定点数据动态截位方法。

6.一种用于存算融合式处理器架构的定点数据动态截位方法,将输入的定点数据d_in中的截位数据d_cut,根据舍入模式向定点数据d_in高位的有效数据d_valid进行舍入进位处理,再对舍入进位处理后的精确值d_precise的低out_w位进行饱和处理后输出,得到定点数据d_in截位后的输出值d_out。

7.进一步的,舍入进位处理由定点数据d_in的二进制整数部分加上进位值完成,进位值由二进制小数部分与特殊值相加形成,不同舍入模式对应不同特殊值。

8.进一步的,舍入进位处理具体包括以下步骤:

9.步骤a1,将定点数据d_in算术右移cut_n位,并在高位补上定点数据d_in的符号位,得到有效数移位值d_arsht,其中cut_n为截取位宽;

10.步骤a2,将定点数据d_in的低cut_max位逻辑左移cut_max-cut_n位,低位补0,得到的截位值d_llsht,其中cut_max=in_w-out_w为最大截取位宽,in_w为输入位宽,out_w为输出位宽;

11.步骤a3,对截位值d_llsht进行数据压缩,将其从cut_max位压缩至2位,得到截位压缩值d_cut_zip,压缩算法为d_cut_zip[1]=d_llsht[cut_max-1],d_cut_zip[0]等于d_llsht低cut_max-1位数据进行位或运算的结果值;

[0012]

步骤a4,将截位压缩值与特殊值相加,得到进位值(0或1);

[0013]

步骤a5,将有效数移位值d_arsht与进位值相加,得到精确值d_precise。

[0014]

进一步的,饱和处理方式为:

[0015]

当精确值d_precise为正数且其值超出out_w位所能表示的正数范围时,则发生上溢,输出值d_out等于out_w位的011

…

1;

[0016]

当精确值d_precise为负数且其值超出out_w位所能表示的负数范围时,则发生下溢,输出值d_out等于out_w位的100

…

0;

[0017]

当精确值d_precise的值未超出out_w位所能表示的数据范围时,输出值d_out等于d_precise[out_w-1:0]。

[0018]

本发明的有益效果:1、兼容ieee 754中的五种标准舍入模式,解决了现有定点数据截位方法定点舍入模式单一的问题;2、实现定点数据截取位宽变化地动态截位需求,极大地提高了定点数据截位电路的通用性,具有良好的可扩展性;3、通过对截位数据进行压缩,以及采用超前进位加法器中的进位算法,降低了路径时延,减少了硬件逻辑单元数量。

附图说明

[0019]

图1为实施例1所述的定点输入数据结构图;

[0020]

图2为实施例1所述的定点输入数据算术右移后结果;

[0021]

图3为实施例1所述的定点输入数据逻辑左移后结果;

[0022]

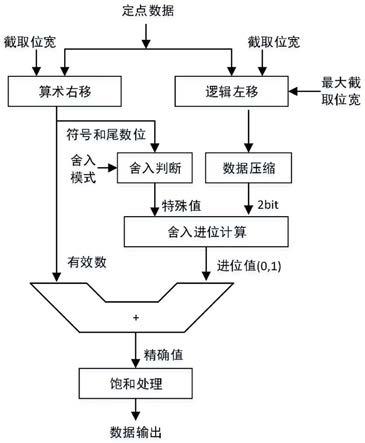

图4为实施例1所述的定点数据动态截位方法流程图。

具体实施方式

[0023]

下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

[0024]

实施例1

[0025]

一种用于存算融合式处理器架构的定点数据动态截位方法,将输入的定点数据d_in中的截位数据d_cut,根据舍入模式向定点数据d_in高位的有效数据d_valid进行舍入进位处理,再将舍入进位处理后的精确值d_precise的低out_w位进行饱和处理后输出,得到定点数据d_in截位后的输出值d_out。

[0026]

下面结合表1对不同舍入模式对应不同的舍入进位处理进行说明。表1中的输入数据分别通过十进制数和二进制数表示。二进制数总位宽为7位,整数部分4位,小数部分3位,整数和小数之间以下划线分隔,数据带有符号,以补码的形式显示;十进制数为该行二进制数据对应的十进制表示,若二进制整数部分为i(x),小数部分为f(x),则定点数据为x=i(x) f(x)。例如,7位二进制正数0001_111,整数部分i(x)=0001,对应十进制为 1,小数部分f(x)=111,对应十进制为 0.875(0.5 0.25 0.125),因而x=i(x) f(x)=1 0.875= 1.875;7位二进制负数1110_111,整数部分i(x)=1110,对应十进制为-2;小数部分f(x)=111,对应十进制为 0.875,因而x=i(x) f(x)=-2 0.875=-1.125。

[0027][0028]

表1

[0029]

表1中包含ieee 754中五种标准舍入模式:

[0030]

(1)向负无穷舍入,即将十进制数取其不大于该数的最大整数;

[0031]

(2)向正无穷舍入,即将十进制数取其不小于该数的最小整数;

[0032]

(3)向零舍入,即当为正数时,十进制数取不大于该数的最大整数;当为负数时,十进制数取不小于该数的最小整数;

[0033]

(4)就近向远离零舍入,即当十进制数小数不等于0.5时,进行四舍五入操作;当十进制数小数等于0.5时,若为正数,则向整数舍入进1,若为负数,则向整数舍入进-1;

[0034]

(5)就近向偶数舍入,即当十进制数小数不等于0.5时,进行四舍五入操作;当十进制数小数等于0.5时,则向整数舍入使其等于其最接近的偶数。

[0035]

通过十进制数的舍入计算可以得到,其对应二进制数据的进位值。通过表1中二进制数的规律可知,若引入一个与舍入模式相关的特殊值,且使其位宽与二进制小数部分位宽相同,再将该特殊值与二进制小数部分f(x)相加,则得到一个向整数部分的进位值(0或1),最后将二进制整数部分i(x)加上该进位值,即可完成舍入进位运算,从而能够兼容ieee 754中的五种标准舍入模式,解决了现有定点数据截位方法定点舍入模式单一的问题。

[0036]

为实现定点数据截取位宽变化地动态截位需求,本实施例通过对定点数据d_in进行移位处理,以消除截取位宽变化对数据索引的影响。下面结合舍入进位处理流程进行阐述。

[0037]

1、定点数据d_in的结构图如图1所示,将定点数据d_in算术右移cut_n位,并在高位补上定点数据d_in的符号位,得到有效数移位值d_arsht,如图2所示,其中cut_n为截取位宽,cut_n位的sign_ext是有效数据符号位的扩展,值为d_in[in_w-1]。

[0038]

通过算数右移使得有效数据d_valid的低位对应d_arsht的低位,消除变量cut_n对数据索引的影响。d_arsht的最高位符号sign=d_arsht[in_w-1]和最低位尾数tail=d_arsht[0],在后续舍入进位中用到。

[0039]

2、将定点数据d_in的低cut_max位逻辑左移cut_max-cut_n位,低位补0,得到的截位值d_llsht,如图3所示,其中cut_max=in_w-out_w为最大截取位宽,in_w为输入位宽,out_w为输出位宽。

[0040]

通过逻辑左移使得截位数据d_cut处于d_llsht高位的固定位置,过滤掉除截位数据外的其他部分,消除变量cut_n对数据索引的影响。

[0041]

步骤2与步骤1可并行执行,使得电路时延更短。

[0042]

3、由于舍入进位处理的硬件开销随着数据位宽的增大而增大,为了降低硬件开销且不改变最终舍入结果,本实施例采用数据压缩的方式将截位值压缩至2bit,同时将引入的特殊值也对应为2bit位宽,从而极大减少硬件单元数和路径时延,降低了硬件开销,提高电路性能。

[0043]

压缩的具体操作为:对截位值d_llsht进行数据压缩,将其从cut_max位压缩至2位,得到截位压缩值d_cut_zip,压缩算法为d_cut_zip[1]=d_llsht[cut_max-1],d_cut_zip[0]等于d_llsht低cut_max-1位数据进行位或运算的结果值。

[0044]

五种标准舍入模式对应的特殊值分别为:

[0045]

(1)向负无穷舍入,特殊值round=2’b00;

[0046]

(2)向正无穷舍入,特殊值round=2’b11;

[0047]

(3)向零舍入,若符号位sign=0(正数),则特殊值round=2’b00;若符号位sign=1(负数),则特殊值round=2’b11;

[0048]

(4)就近向远离零舍入,若符号位sign=0(正数),则特殊值round=2’b10;若符号位sign=1(负数),则特殊值round=2’b01;

[0049]

(5)就近向偶数舍入,若尾数位tail=0(偶数),则特殊值round=2’b01;若尾数位tail=1(奇数),则特殊值round=2’b10。

[0050]

4、将截位压缩值d_cut_zip与特殊值round相加,得到进位值carry(0或1)。为减少逻辑单元数量和时序,本实施例采用超前进位加法器中的进位算法,具体计算过程如下:

[0051]

生成信号:gi=d_cut_zip[i]&round[i];

[0052]

传播信号:pi=d_cut_zip[i]|round[i];

[0053]

进位信号:ci 1=gi|pi&ci,其中c0=0;

[0054]

进位值carry=c2=g1|p1&g0|p1&p0&c0=g1|p1&g0。

[0055]

5、将有效数移位值d_arsht与进位值相加,得到精确值d_precise。由于此处精确值d_precise的位宽与d_arsht位宽相同,不用考虑加法后向更高位进位的问题,因为当d_arsht为正数时,其最高位为0,加1bit数据后不会向更高位进位;当d_arsht为负数时,加1bit数据后也在数据所能表示范围内。

[0056]

对精确值d_precise的低out_w位进行饱和处理后输出定点数据d_in截位后的输出值d_out,具体饱和处理方式为:

[0057]

当精确值d_precise为正数且其值超出out_w位所能表示的正数范围时,则发生上溢,输出值d_out等于out_w位的011

…

1;

[0058]

当精确值d_precise为负数且其值超出out_w位所能表示的负数范围时,则发生下溢,输出值d_out等于out_w位的100

…

0;

[0059]

当精确值d_precise的值未超出out_w位所能表示的数据范围时,输出值d_out等

于d_precise[out_w-1:0]。

[0060]

综合本实施例中提及的方法步骤,其定点数据动态截位方法流程图如图4所示。经过图4所示的定点数据动态截位方法,即可完整实现高精度、低时延、少逻辑的定点数据动态截位方案。

[0061]

显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。