一种soc芯片复位处理方法、装置、soc芯片及介质

技术领域

1.本技术涉及芯片设计技术领域,特别涉及一种soc芯片复位处理方法、装置、soc芯片及介质。

背景技术:

2.随着芯片技术的高速发展,芯片的功能越来越强大,从而其复杂度也越来越高,其需要支持的复位类型也越来越多。芯片复位类型主要包括:cold reset(即冷复位),debug reset(即调试复位),software reset(即软件复位),watchdog reset(即看门狗复位)reset,pcie(即peripheral component interconnect express reset,高速串行计算机扩展总线标准)reset等。

3.当前,在大部分芯片设计中,cpu reset vector(即cpu(即central processing unit,中央处理器)复位向量)地址空间会放置一块片上rom(即read only memory,随机存储器),其内容为bootrom程序(即处理器在上电或复位时执行的第一段代码)。芯片在复位发生后,cpu会从reset vector地址开始读取指令并执行,bootrom开始执行,对于复位的处理是在bootrom程序中完成的,bootrom程序会先判断当前发生复位的类型,并进入相对于的复位处理分支,再针对此复位类型进行相应的处理。由于bootrom程序是固化在片上rom中的,芯片流片后,其不能再被修改,这意味着复位处理的代码在流片后也是不能修改的,不具备灵活性。另外,芯片复位发生后,bootrom程序需要重新执行,而bootrom程序的执行需要时间,尤其是bootrom程序中加解密算法的执行需要大量的时间,从而导致需要花费宝贵的时间来处理芯片的复位。

技术实现要素:

4.有鉴于此,本技术的目的在于提供一种soc芯片复位处理方法、装置、soc芯片及介质,能够提升芯片复位处理的灵活性,并节约芯片处理非冷复位的时间。其具体方案如下:

5.第一方面,本技术公开了一种soc芯片复位处理方法,包括:

6.从片上ram的起始地址开始,将复位处理程序写入所述片上ram;

7.将所述片上ram的起始地址映射至cpu复位向量地址;

8.当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。

9.可选的,执行所述复位处理程序,以进行相应的复位处理,包括:

10.执行所述复位处理程序,并在执行过程中读取复位状态寄存器的寄存器值,基于所述寄存器值判断当前复位的复位类型,根据该复位类型执行该复位类型对应的复位处理子程序,以进行相应的复位处理。

11.可选的,所述将所述片上ram的起始地址映射至cpu复位向量地址,包括:

12.操作预设片上ram映射寄存器,以将所述片上ram的起始地址映射至cpu复位向量地址。

13.可选的,所述预设片上ram映射寄存器在soc芯片发生冷复位时复位为默认值;

14.其中,若soc芯片的片上rom的起始地址与所述cpu复位向量地址一致,则所述预设片上ram映射寄存器的默认值表示不对所述片上ram的起始地址进行映射;若所述片上rom的起始地址与所述cpu复位向量地址不一致,则所述预设片上ram映射寄存器的默认值表示将所述片上rom的起始地址映射至所述cpu复位向量地址。

15.可选的,还包括:

16.当soc芯片发生冷复位,从片上rom的起始地址开始读取并执行bootrom程序;

17.执行完成所述bootrom程序后,执行bootloader程序,并在执行bootloader程序过程中,从片上ram的起始地址开始,将复位处理程序写入所述片上ram,以及将所述片上ram的起始地址映射至cpu复位向量地址。

18.可选的,在所述将所述片上ram的起始地址映射至cpu复位向量地址之后,还包括:

19.操作预设片上rom控制寄存器,以关闭片上rom的电源和时钟。

20.可选的,所述预设片上rom控制寄存器在soc芯片发生冷复位时复位为默认值,该默认值表示使能所述片上rom的电源和时钟。

21.第二方面,本技术公开了一种soc芯片复位处理装置,包括:

22.复位处理程序写入模块,用于从片上ram的起始地址开始,将复位处理程序写入所述片上ram;

23.ram地址映射模块,用于将所述片上ram的起始地址映射至cpu复位向量地址;

24.soc芯片复位处理模块,用于当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。

25.第三方面,本技术公开了一种soc芯片,包括:

26.存储器,用于保存计算机程序;

27.处理器,用于执行所述计算机程序,以实现前述的soc芯片复位处理方法。

28.第四方面,本技术公开了一种计算机可读存储介质,用于保存计算机程序,所述计算机程序被处理器执行时实现前述的soc芯片复位处理方法。

29.可见,本技术先从片上ram的起始地址开始,将复位处理程序写入所述片上ram,并将所述片上ram的起始地址映射至cpu复位向量地址,当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。也即,本技术实施例将片上ram地址空间映射到cpu复位向量地址空间,并在片上ram的起始位置开始,写入了复位处理程序,当soc芯片发生非冷复位,cpu便会从片上ram的起始地址开始读取并执行复位处理程序,以进行复位处理。由于ram中的内容是可以修改的,所以在芯片流片回片后,根据芯片调试需要,在ram中可以反复写入不同的复位处理程序进行调试,找出最终可交付的程序,这样,提升了芯片复位处理的灵活性,并且,对于非冷复位,不需要bootrom再次执行,而是直接通过复位处理程序执行,节约了芯片处理非冷复位的时间。

附图说明

30.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据

提供的附图获得其他的附图。

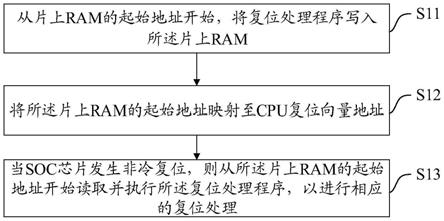

31.图1为本技术公开的一种soc芯片复位处理方法流程图;

32.图2为本技术公开的一种具体的地址映射示意图;

33.图3为本技术公开的另一种具体的地址映射示意图;

34.图4为本技术公开的一种具体的soc芯片复位处理流程示意图;

35.图5为本技术公开的一种soc芯片复位处理装置结构示意图;

36.图6为本技术公开的一种soc芯片结构图。

具体实施方式

37.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

38.当前,在大部分芯片设计中,cpu reset vector地址空间会放置一块片上rom(即read only memory,随机存储器),其内容为bootrom程序。芯片在复位发生后,cpu会从reset vector地址开始读取指令并执行,bootrom开始执行,对于复位的处理是在bootrom程序中完成的,bootrom程序会先判断当前发生复位的类型,并进入相对于的复位处理分支,再针对此复位类型进行相应的处理。由于bootrom程序是固化在片上rom中的,芯片流片后,其不能再被修改,这意味着复位处理的代码在流片后也是不能修改的,不具备灵活性。另外,芯片复位发生后,bootrom程序需要重新执行,而bootrom程序的执行需要时间,尤其是bootrom程序中加解密算法的执行需要大量的时间,从而导致需要花费宝贵的时间来处理芯片的复位。为此,本技术提供了一种soc(即system on chip,片上系统)芯片复位方案,能够提升芯片复位处理的灵活性,并节约芯片处理非冷复位的时间。

39.参见图1所示,本技术实施例公开了一种soc芯片复位处理方法,包括:

40.步骤s11:从片上ram(即random access memory,随机存储器)的起始地址开始,将复位处理程序写入所述片上ram。

41.也即,本技术实施例中,将复位处理程序写入片上ram,并且,从片上ram的起始地址开始写入。

42.步骤s12:将所述片上ram的起始地址映射至cpu复位向量地址。

43.需要指出的是,cpu复位向量地址为cpu复位后,读取第一条指令所在的地址,将片上ram的起始地址映射至cpu复位向量地址,cpu复位后,读取第一条指令所在的地址即为片上ram的起始地址。

44.在具体的实施方式中,操作预设片上ram映射寄存器,以将所述片上ram的起始地址映射至cpu复位向量地址。

45.其中,所述预设片上ram映射寄存器在soc芯片发生冷复位时复位为默认值;并且,若soc芯片的片上rom的起始地址与所述cpu复位向量地址一致,则所述预设片上ram映射寄存器的默认值表示不对所述片上ram的起始地址进行映射;若所述片上rom的起始地址与所述cpu复位向量地址不一致,则所述预设片上ram映射寄存器的默认值表示将所述片上rom的起始地址映射至所述cpu复位向量地址。

46.需要指出的是,在soc芯片架构设计时,根据其所选用cpu的类型来确定cpu reset vector在地址空间总线上所分配的地址。以arm公司的cpu来举例,一般其cpu reset vector地址设置为0x00000000,但是也可根据实际情况,使用其他的地址。并为片上rom分配其在地址总线上的地址空间,此地址空间的起始地址可以与cpu reset vector地址一致,也可以与cpu reset vector地址不一致,具体如何选择则根据芯片设计需求而定。根据芯片对于片上ram的需求,为芯片配置一块片上ram或者多块片上ram,并为片上ram分配地址空间。如是多块片上ram,则选择其中一块为主ram,在使用地址映射功能时所用。在为片上rom和片上ram分配地址空间时,也要结合所选cpu的类型来进行,因为当前的cpu一般都会采用relaxed memory model,而有些cpu默认地对其总线地址空间进行了区域划分,并对这些区域的配置了相应的memory访问类型。

47.进一步的,本技术设计了一个片上ram映射寄存器,用于把片上ram地址空间映射到cpu reset vector地址。在芯片设计中,当片上rom起始地址与cpu reset vector地址一致时,此映射寄存器默认值表示不使能片上ram映射功能,当操作此寄存器使能ram映射功能后,片上ram的起始地址则会映射到cpu reset vector地址,当访问cpu reset vector地址及其后片上ram大小空间地址时,访问的内容为片上ram的内容,而不是片上rom的内容。在芯片设计中,当片上rom起始地址与cpu reset vector地址不一致时,片上ram映射寄存器默认值表示把片上rom起始地址映射到cpu reset vector地址,当操作此寄存器使能ram映射功能后,片上ram的起始地址则会映射到cpu reset vector地址,而之前片上rom起始地址映射到cpu reset vector地址的功能会被取消。

48.例如,参见图2所示,图2为本技术实施例公开的一种具体的地址映射示意图,图2中,rom的起始地址与cpu reset vector地址一致,参见图3所示,图3为本技术实施例公开的另一种具体的地址映射示意图,图3中,rom的起始地址与cpu reset vector地址不一致。

49.另外,本技术在将所述片上ram的起始地址映射至cpu复位向量地址之后,操作预设片上rom控制寄存器,以关闭片上rom的电源和时钟。

50.其中,所述预设片上rom控制寄存器在soc芯片发生冷复位时复位为默认值,该默认值表示使能所述片上rom的电源和时钟。

51.也即,本技术设计了一个片上rom控制寄存器,用于控制片上rom的power(即电源)和clock(即时钟),其默认值表示使能power和clock。该寄存器有两个作用,其一,当power和clock不使能时,片上rom不能被访问,保护了其内容不能被读取,因为片上rom中固化的是芯片的bootrom程序,其是整个芯片的信任根所在,是芯片安全的基石;其二,当power和clock不使能时,片上rom不产生功耗,其降低了整个芯片的功耗,此在低功耗芯片设计中尤为重要。

52.可以理解的是,本技术在在设计芯片复位功能时,对于不同的复位类型的设计,其对片上ram映射功能寄存器和片上rom控制寄存器的作用效果不同。当cold reset复位发生后,片上ram映射寄存器和片上rom控制寄存器会被复位到默认值,其所控制的功能同时会被复位到默认状态。当非cold reset复位发生后,片上ram映射寄存器和片上rom控制寄存器所设置的值会被保存,而不会被复位到默认值,其所控制的功能同样会保持其当前状态,不会被复位到默认状态。

53.步骤s13:当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行

所述复位处理程序,以进行相应的复位处理。

54.在具体的实施方式中,执行所述复位处理程序,并在执行过程中读取复位状态寄存器的寄存器值,基于所述寄存器值判断当前复位的复位类型,根据该复位类型执行该复位类型对应的复位处理子程序,以进行相应的复位处理。

55.并且,本技术实施例,当soc芯片发生冷复位,从片上rom的起始地址开始读取并执行bootrom程序;执行完成所述bootrom程序后,执行bootloader程序,并在执行bootloader程序过程中,从片上ram的起始地址开始,将复位处理程序写入所述片上ram,以及将所述片上ram的起始地址映射至cpu复位向量地址。

56.可以理解的是,本技术根据芯片设计中支持的所有非冷复位的复位类型,编写复位处理程序,在复位处理程序中,通过读取芯片复位状态寄存器来判断当前发生复位的类型,然后再跳转到此复位类型的分支处理代码进行处理。本技术实施例复位处理程序从片上ram的起始地址处开始放置,保障复位处理程序的入口地址与cpu reset vector地址一致。并且,在bootloader程序中,在其对芯片初始化阶段,本技术实施例将复位处理程序代码拷贝到片上ram的起始地址及之后的地址空间,拷贝完成后,通过操作片上ram映射功能寄存器把片上ram地址空间映射到cpu reset vector地址。然后通过操作片上rom控制寄存器,关闭片上rom的power和clock。

57.例如,参见图4所示,本技术实施例公开了一种芯片boot即复位发生后的处理流程示意图。在soc芯片设计中,设计一种把片上ram地址空间映射到cpu的reset vector地址空间的机制,通过寄存器控制此机制,此映射机制生效后,其只能被cold reset复位,不能被其他类型的reset复位。另外,为片上rom设置一个寄存器来控制其power和clock,此寄存器默认值是使能rom的power和clock,同样,当此寄存器关闭rom的power和clock后,其只能被cold reset复位,不能被其他类型的reset复位。当芯片发生cold reset复位后,cpu从reset vector开始读取指令并执行,bootrom程序开始执行,执行完成后,跳转到下一级bootloader程序执行,在bootloader程序中,在ram起始地址处写入相应的复位处理程序,再通过操作映射寄存器使能ram地址空间映射机制,同时通过rom寄存器关闭rom的power和clock,当芯片产生除了cold reset之外的复位后,cpu则会从ram的起始地址开始读取指令并执行,也就是执行ram起始地址处之前写入的复位处理程序。当芯片产生cold reset复位后,cpu则会从rom的起始地址开始读取指令并执行,也即开始执行bootrom程序。

58.可见,本技术实施例先从片上ram的起始地址开始,将复位处理程序写入所述片上ram,并将所述片上ram的起始地址映射至cpu复位向量地址,当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。也即,本技术实施例将片上ram地址空间映射到cpu复位向量地址空间,并在片上ram的起始位置开始,写入了复位处理程序,当soc芯片发生非冷复位,cpu便会从片上ram的起始地址开始读取并执行复位处理程序,以进行复位处理。由于ram中的内容是可以修改的,所以在芯片流片回片后,根据芯片调试需要,在ram中可以反复写入不同的复位处理程序进行调试,找出最终可交付的程序,这样,提升了芯片复位处理的灵活性,并且,对于非冷复位,不需要bootrom再次执行,而是直接通过复位处理程序执行,节约了芯片处理非冷复位的时间。

59.并且,当片上ram映射后,可以关闭片上rom的power和clock,节省了芯片的功耗,保障了rom中内容的安全性。

60.参见图5所示,本技术实施例公开了一种soc芯片复位处理装置,包括:

61.复位处理程序写入模块11,用于从片上ram的起始地址开始,将复位处理程序写入所述片上ram;

62.ram地址映射模块12,用于将所述片上ram的起始地址映射至cpu复位向量地址;

63.soc芯片复位处理模块13,用于当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。

64.可见,本技术实施例先从片上ram的起始地址开始,将复位处理程序写入所述片上ram,并将所述片上ram的起始地址映射至cpu复位向量地址,当soc芯片发生非冷复位,则从所述片上ram的起始地址开始读取并执行所述复位处理程序,以进行相应的复位处理。也即,本技术实施例将片上ram地址空间映射到cpu复位向量地址空间,并在片上ram的起始位置开始,写入了复位处理程序,当soc芯片发生非冷复位,cpu便会从片上ram的起始地址开始读取并执行复位处理程序,以进行复位处理。由于ram中的内容是可以修改的,所以在芯片流片回片后,根据芯片调试需要,在ram中可以反复写入不同的复位处理程序进行调试,找出最终可交付的程序,这样,提升了芯片复位处理的灵活性,并且,对于非冷复位,不需要bootrom再次执行,而是直接通过复位处理程序执行,节约了芯片处理非冷复位的时间。

65.soc芯片复位处理模块13,具体用于执行所述复位处理程序,并在执行过程中读取复位状态寄存器的寄存器值,基于所述寄存器值判断当前复位的复位类型,根据该复位类型执行该复位类型对应的复位处理子程序,以进行相应的复位处理。

66.ram地址映射模块12,具体用于操作预设片上ram映射寄存器,以将所述片上ram的起始地址映射至cpu复位向量地址。

67.其中,所述预设片上ram映射寄存器在soc芯片发生冷复位时复位为默认值;若soc芯片的片上rom的起始地址与所述cpu复位向量地址一致,则所述预设片上ram映射寄存器的默认值表示不对所述片上ram的起始地址进行映射;若所述片上rom的起始地址与所述cpu复位向量地址不一致,则所述预设片上ram映射寄存器的默认值表示将所述片上rom的起始地址映射至所述cpu复位向量地址。

68.进一步的,所述装置还用于:当soc芯片发生冷复位,从片上rom的起始地址开始读取并执行bootrom程序;执行完成所述bootrom程序后,执行bootloader程序,并在执行bootloader程序过程中,从片上ram的起始地址开始,将复位处理程序写入所述片上ram,以及将所述片上ram的起始地址映射至cpu复位向量地址。

69.进一步的,所述装置还包括rom的电源和时钟控制模块,用于操作预设片上rom控制寄存器,以关闭片上rom的电源和时钟。

70.其中,所述预设片上rom控制寄存器在soc芯片发生冷复位时复位为默认值,该默认值表示使能所述片上rom的电源和时钟。

71.参见图6所示,本技术实施例公开了一种soc芯片,包括处理器21和存储器22;其中,所述存储器22,用于保存计算机程序;所述处理器21,用于执行所述计算机程序,前述实施例公开的soc芯片复位处理方法。

72.关于上述soc芯片复位处理方法的具体过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

73.进一步的,本技术实施例还公开了一种计算机可读存储介质,用于保存计算机程

序,其中,所述计算机程序被处理器执行时实现前述实施例公开的soc芯片复位处理方法。

74.关于上述soc芯片复位处理方法的具体过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

75.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

76.以上对本技术所提供的一种soc芯片复位处理方法、装置、soc芯片及介质进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的一般技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。