1.本发明涉及电子电路技术领域,特别涉及一种高压集成电路。

背景技术:

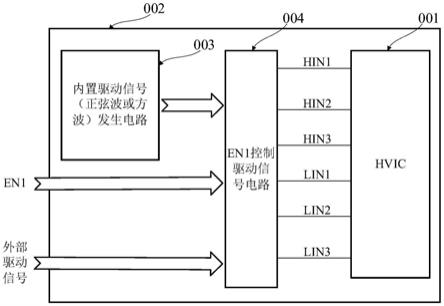

2.高压集成电路,即hvic,是一种把mcu信号转换成驱动igbt信号的集成电路产品。hvic把pmos管、nmos管、三极管、二极管、稳压管、电阻、电容集成在一起,形成斯密特、低压levelshift、高压levelshift、脉冲发生电路、延时电路、滤波电路、过电流保护电路和过热保护电路、欠压保护电路、自举电路等电路。hvic一方面接收mcu的控制信号,驱动后续igbt或mos工作,另一方面将系统的状态检测信号送回mcu,是ipm内部的关键芯片。hvic的基本拓扑结构如图1所示,其中,hin1、hin2、hin3为高侧驱动电路信号输入端;vb1、vb2、vb3为高侧驱动电路浮动电源端;vs1、vs2、vs3为高侧驱动电路浮动地;ho1、ho2、ho3为高侧驱动电路驱动信号输出端;vcc是低侧驱动电路供电电源;lin1、lin2、lin3为低侧驱动电路信号输入端;lo1、lo2、lo3为低侧驱动电路驱动信号输出端;en连接高侧驱动电路和低侧驱动电路,控制hin1、hin2、hin3、lin1、lin2、lin3是否有效;fo为hvic故障信号输出端。传统的hvic,在应用时,均需要外部输入逻辑驱动信号,无法采用自带信号驱动,功能较为单一,应用范围较小。

技术实现要素:

3.本发明要解决的技术问题在于,针对现有技术的上述缺陷,提供一种高压集成电路,通过内置驱动信号发生电路,同时兼顾从外部输入逻辑驱动信号功能,通过en1输入端输出的高低电平控制选择采用内部逻辑驱动信号还是从外部输入逻辑驱动信号,功能多样化,应用范围广,提升了hvic应用的多元化。

4.为了解决上述技术问题,本发明的技术方案是:

5.一种高压集成电路,包括hvic电路、内置驱动信号发生电路、en1控制驱动信号电路、en1输入端及外部驱动信号输入端,所述en1控制驱动信号电路分别与所述内置驱动信号发生电路、en1输入端、外部驱动信号输入端及hvic电路电性连接,当en1输入端为高电平时,所述hvic电路由内置驱动信号发生电路进行驱动;当en1输入端为低电平时,所述hvic电路由外部驱动信号输入端进行驱动。

6.优选地,所述内置驱动信号发生电路用于输出正弦波信号或方波信号。

7.优选地,所述en1控制驱动信号电路包括与非门电路、第一非门电路、第二非门电路、与门电路及或门电路,所述与非门电路分别与所述第一非门电路及第二非门电路电性连接,所述与门电路分别与所述第一非门电路及或门电路电性连接,所述或门电路分别与所述与门电路及第二非门电路电性连接。

8.优选地,所述内置驱动信号发生电路与所述与非门电路电性连接,所述en1输入端分别与所述与非门电路及第一非门电路电性连接,所述外部驱动信号输入端与所述与门电路电性连接,所述或门电路与所述hvic电路电性连接。

9.优选地,当所述en1输入端的输入信号为高电平时,所述与非门电路输出与所述输入信号相反的逻辑信号,所述第二非门电路输出与所述与非门电路输入相同的逻辑信号,所述第一非门电路输出低电平,所述与门电路输出低电平,所述或门电路输出的逻辑电平与所述内置驱动信号发生电路的逻辑电平一致。

10.优选地,当所述en1输入端的输入信号为低电平时,所述与非门电路输出高电平,所述非门电路输出低电平,所述第一非门电路输出高电平,所述与门电路输出高电平,所述或门输出的逻辑电平与外部驱动信号输入端的逻辑电平一致。

11.优选地,所述与非门电路的输入端与所述外部驱动信号输入端与所述内置驱动信号发生电路的输出端电性连接,所述与门电路的输入端与所述外部驱动信号输入端的输出端电性连接。

12.优选地,所述或门电路的输出端与所述hvic电路的高侧驱动电路信号输入端及低侧驱动电路信号输入端电性连接。

13.采用上述技术方案,本发明提供的一种高压集成电路,具有以下有益效果:该高压集成电路中的en1控制驱动信号电路分别与内置驱动信号发生电路、en1输入端、外部驱动信号输入端及hvic电路电性连接,当en1输入端为高电平时,hvic电路由内置驱动信号发生电路进行驱动;当en1输入端为低电平时,hvic电路由外部驱动信号输入端进行驱动,通过内置驱动信号发生电路,同时兼顾从外部输入逻辑驱动信号功能,通过en1输入端输出的高低电平控制选择采用内部逻辑驱动信号还是从外部输入逻辑驱动信号,功能多样化,应用范围广,提升了hvic应用的多元化。

附图说明

14.图1为现有的hvic的基本拓扑结构图;

15.图2为本发明的基本拓扑结构图;

16.图3为本发明实施例一的内部拓扑结构示意图;

17.图中,001-hvic电路、002-高压集成电路、003-内置驱动信号发生电路、004-en1控制驱动信号电路、005-与非门电路、006-第一非门电路、007-第二非门电路、008-与门电路、009-或门电路。

具体实施方式

18.下面结合附图对本发明的具体实施方式作进一步说明。在此需要说明的是,对于这些实施方式的说明用于帮助理解本发明,但并不构成对本发明的限定。此外,下面所描述的本发明各个实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互组合。

19.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

20.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者

隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

21.如图1-图3所示,该高压集成电路002包括hvic电路001、内置驱动信号发生电路003、en1控制驱动信号电路004、en1输入端及外部驱动信号输入端,该en1控制驱动信号电路004分别与该内置驱动信号发生电路003、en1输入端、外部驱动信号输入端及hvic电路001电性连接,当en1输入端为高电平时,该hvic电路001由内置驱动信号发生电路003进行驱动;当en1输入端为低电平时,该hvic电路001由外部驱动信号输入端进行驱动。可以理解的,该内置驱动信号发生电路003用于输出正弦波信号或方波信号。

22.具体地,该en1控制驱动信号电路004包括与非门电路005、第一非门电路006、第二非门电路007、与门电路008及或门电路009,该与非门电路005分别与该第一非门电路006及第二非门电路007电性连接,该与门电路008分别与该第一非门电路006及或门电路009电性连接,该或门电路009分别与该与门电路008及第二非门电路007电性连接;该内置驱动信号发生电路003与该与非门电路005电性连接,该en1输入端分别与该与非门电路005及第一非门电路006电性连接,该外部驱动信号输入端与该与门电路008电性连接,该或门电路009与该hvic电路001电性连接;该与非门电路005的输入端与该外部驱动信号输入端与该内置驱动信号发生电路003的输出端电性连接,该与门电路008的输入端与该外部驱动信号输入端的输出端电性连接;该或门电路009的输出端与该hvic电路001的高侧驱动电路信号输入端及低侧驱动电路信号输入端电性连接。

23.可以理解的,该高压集成电路002的工作原理:当en1输入端为高电平1时,与非门电路005输出与输入相反逻辑信号,第二非门电路007输出与该与非门电路005输入相同的逻辑信号,第一非门电路006输出0,与门电路008输出0,即当en1输入端为1时,或门电路009输出逻辑电平与该内置驱动信号发生电路003一致;当en1输入端为低电平0时,与非门电路005输出1,第二非门电路007输出0,第一非门电路006输出1,与门电路008输出与外部驱动信号输入端的逻辑电平信号一致,即当en1输入端为0时,或门电路009输出逻辑电平与外部驱动信号输出一致。各电路输出真值表如下:

24.[0025][0026]

可以理解的,本发明通过en1控制驱动信号发生电路004和内置驱动信号发生电路003设计,采用cadence的virtuoso进行版图设计和mmsim进行drc和lvs查错;把en1控制驱动信号发生电路和内置驱动信号(正弦波或方波)发生电路集成到hvic内部,进行hvic完整电路的电路功能仿真和mmsim进行drc和lvs查错;en1控制驱动信号模块和内置驱动信号(正弦波或方波)发生电路版图集成到hvic版图中,版图电路连接按电路原理图进行连接,可实现通过en1端的高低电平控制选择采用内部逻辑驱动信号还是从外部输入逻辑驱动信号,提升了hvic应用的多元化。

[0027]

以上结合附图对本发明的实施方式作了详细说明,但本发明不限于所描述的实施方式。对于本领域的技术人员而言,在不脱离本发明原理和精神的情况下,对这些实施方式进行多种变化、修改、替换和变型,仍落入本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。