一种减小fpga芯片静态功耗的系统架构

技术领域

1.申请实施例涉及芯片领域,特别涉及一种减小fpga芯片静态功耗的系统架构。

背景技术:

2.fpga制造工艺进入90ns以后为了确保fpga的高性能,芯片设计厂商通常降低晶体管的门槛电压,使得晶体管快速开关达到减小传播延时的目的。门槛电压的降低导致晶体管泄露电流呈指数增加,这样会使芯片静态功耗大大增加。

3.相关技术中,降低fpga芯片的功耗,在向fpga芯片烧录文件时,提前对fpga芯片内部的逻辑资源进行规划,以资源最大化利用fpga颗粒,避免不必要的功耗损失。

技术实现要素:

4.本技术提供了一种减小fpga芯片静态功耗的系统架构,解决fpga芯片逻辑资源静态功耗的问题。

5.所述fpga芯片包含最小逻辑资源块、io管脚和功率控制网络;

6.所述功率控制网络将所述最小逻辑资源块之间的逻辑器件互相连接,用于控制所述最小逻辑资源块的供电;

7.所述功率控制网络与所述fpga芯片的控制电源连接,并根据接收的控制信号控制所述控制电源对所述最小逻辑资源块的供电。

8.具体的,所述功率控制网络由功率控制线组成;所述功率控制线连接到所述最小逻辑资源块和所述控制电源之间,所述功率控制线之间互相连接组成所述功率控制网络。

9.具体的,所述控制电源至少包括所述fpga芯片结构的内核电源、io电路主电源以及io电源;

10.所述内核电源与所述fpga芯片的专用管脚连接,用于提供内核电压,并通过所述功率控制线连接到所述最小逻辑资源块;

11.所述io电路主电源与所述fpga芯片的io管脚及内部布线资源连接,用于向布线资源提供电压,所述功率控制线连接到所述最小逻辑资源块;

12.所述逻辑块内部电源与所述fpga芯片的供电电压轨连接,用于提供供电电压。

13.具体的,所述功率控制网络由所述fpga的控制信号进行控制,当所述功率控制网络未接收到控制信号时,所述最小逻辑资源块与所述控制电源处于连接状态;

14.当所述功率控制网络接收到控制信号时,所述最小逻辑资源块与所述控制电源处于断开状态。

15.具体的,所述控制信号基于烧写所述fpga芯片的电路文件产生,当向所述fpga芯片烧录电路文件时,所述功率控制网络根据电路结构断开未布局的所述最小逻辑资源块上的所述功率控制线;同时保持布局的所述最小逻辑资源块上的所述功率控制线处于连通状态。

16.本技术提供的技术方案带来的有益效果至少包括:通过在fpga芯片内部引入功率

控制网络,用功率控制线控制最小逻辑资源块与控制电源的连接状态,以确保在未部署状态下处于断开状态,不会因泄漏电流产生静态功耗,同时对于未部署的io管脚,也可以减少静态功耗产生,提高fpga的资源利用率和执行效率。

附图说明

17.图1是本技术实施例提供的fpga内部结构示意图;

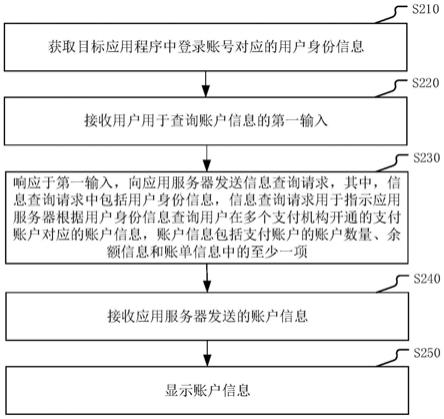

18.图2是本技术实施例提供的减小fpga芯片静态功耗的系统架构图;

19.图3是本技术实施例提供的烧录电路文件部署最小逻辑资源块的示意图。

具体实施方式

20.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施方式作进一步地详细描述。

21.在本文中提及的“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。

22.fpga芯片的制造技术在进入到90nm以后,为了确保fpga的高性能,芯片制造商通常会降低晶体管的门槛电压,而门槛电压的降低会导致晶体管泄露电流呈现指数增加,导致芯片产生静态功耗。尤其是fpga芯片中未使用的逻辑资源块,虽然逻辑块未处理相关功能,但依然存在接入电压,也即逻辑资源块存在静态功耗。此外,工艺的提升会导致fpga芯片的io管脚也越来越多,io管脚同样也会产生相应的静态功耗。

23.图1是构成fpga芯片是内部结构图。包括大量的最小逻辑资源块11、可编程i/o单元12和布线资源13等。fpga结构中包括大量的可编程最小逻辑资源块11,最小逻辑资源块11是实现用户功能的基本单元,通过和布线资源13的连接可以形成可查找和可编辑的逻辑电路,完成相应的执行功能,特别针对cnn网络和图像处理等功能等。当实现的计算功能越复杂,则需要部署fpga中更多的逻辑资源。最小逻辑资源块11是至少2个查找表、1块8kb ram、8个触发器、1个进位链和一个dsp逻辑资源的集合。fpga芯片由海量的最小逻辑资源块组合执行复杂的计算功能。而对于每个最小逻辑资源块来说,在未接收指令执行相应计算功能时,电路结构仍然会有泄露电流和电压,不可避免的会增加fpga芯片的静态功耗。

24.图2是本发明提供的减小fpga芯片静态功耗的系统架构图,其中的最小资源块和io端口之间通过布线资源实现连接,每个最小资源逻辑块都接入有控制电源,包括内核电源、io电路主电源以及逻辑块内部电源中的至少一种。fpga芯片结构内核电压由内核电源提供,通过专用管脚v

ccint

连接到最小资源逻辑块内部的逻辑门和触发器。vcco是io电路的主电源,所有vcco管脚必须连接到开发板上相同的外部供电电压,其内部与fpga芯片的io管脚及内部布线资源连接,提供相应的电压。逻辑块内部电源与fpga芯片的供电电压轨连接,用于提供供电电压。考虑fpga芯片所有的最小逻辑资源块都会连接这几种控制电源(图中为示例,每个最小逻辑资源块都会连接几种控制电源)。选择在生产fpga芯片架构时在内部部署功率控制网络,功率控制网络是由海量的功率控制线组成,功率控制线取代了以往电路结构中各个控制电源的连接线,且将功率控制线采用网络化布局形成功率控制网络,功率控制网络将各个最小逻辑资源块和之间的供电器件连接,以使各个控制电源通过功率

控制线向最小逻辑资源块供电。

25.功率控制网络根据控制信号来控制各个控制电源与最小逻辑资源块之间的通断与连接。功率控制网络在未接收到控制信号时,最小逻辑资源块与控制电源处于连接状态,此时的最小逻辑资源块处于部署状态,也即能够参与执行指令和任务;当功率控制网络接收到控制信号时,最小逻辑资源块断开与控制电源的连接,此时的最小逻辑资源块处于未部署状态,同时也无法执行指令任务,避免产生静态功耗。其中,控制指令是在向fpga芯片烧录电路文件时输入,该电路文件中不仅包含待部署最小资源逻辑块的资源布局外,还包括对功率控制线的通断控制指令,其中过包括对待部署最小资源逻辑块的导通指令和未部署最小资源逻辑块的断开指令,导通指令用于将待部署最小资源逻辑块和控制电源之间的功率控制线导通,形成回路,完成资源部署;断开指令用于将未部署最小资源逻辑块和控制电源之间的功率控制线断开,避免产生静态功耗。同理,对于io管脚,当fpga芯片用于执行特定功能仅需部分最小资源逻辑块和对应的io管脚时,断开控制电源与io管脚之间的连接,减少了io管脚产生的静态功耗。通过降低fpga芯片静态功耗的方式可以减少电能损耗,且可以有效提高芯片资源利用率和任务的执行效率。

26.如图3所示,当需要改变fpga芯片执行的功能或任务时,需要根据具体执行的任务设计并部署电路文件,在设计电路文件时须充分考虑fpga自身的可利用逻辑资源量和执行具体任务所需的逻辑资源量。确定逻辑资源量后,生成可部署的电路文件并进行烧录。其中,待部署的最小资源逻辑块组合的逻辑资源应大于执行具体任务所需的逻辑资源量,同时还应保留一定的余量,确保执行的可靠性。烧录完成后,未部署的最小逻辑资源块之间的功率控制线断开,不会产生静态功耗,已部署的最小逻辑资源块之间的功率控制线导通,用于执行响应的指令任务。

27.综上所述,本技术实施例提供的系统架构,通过在fpga芯片内部引入功率控制网络,用功率控制线控制最小逻辑资源块与控制电源的连接状态,以确保在未部署状态下处于断开状态,不会因泄漏电流产生静态功耗,同时对于未部署的io管脚,也可以减少静态功耗产生,提高fpga的资源利用率和执行效率。

28.以上对本发明的较佳实施例进行了描述;需要理解的是,本发明并不局限于上述特定实施方式,其中未尽详细描述的设备和结构应该理解为用本领域中的普通方式予以实施;任何熟悉本领域的技术人员,在不脱离本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例,这并不影响本发明的实质内容;因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。