1.本发明涉及电装技术领域,尤其涉及一种低空洞率、高导热纳米银导电胶烧结工艺。

背景技术:

2.功率芯片高可靠焊接主要有共晶焊接技术和纳米银浆焊接技术两种。 共晶焊接具有连接电阻小、焊接强度高等特点,但是这种方式焊接温度较高,焊接中需要施加压力,在实际工程生产中,需要极高的操作技术水平,难度较大,并且需针对不同类型、尺寸芯片定制专用工装或仪器设备,工艺难度大、成本高。且传统的auge、ausn共晶焊料热导率一般在40~50w/mk,而纳米银的热导率理论上可以高达200 w/mk以上,可实现低温烧结,因此,低温烧结高温服役的纳米银导电胶成为芯片焊接的理想热界面材料,在大功率器件装配领域具有较高的应用价值。

3.纳米银材料目前在消费电子产品中有一定的应用,而在军工产品及其他可靠性要求较高的场景下少有应用,一方面是由于纳米银材料用于热界面材料时,由于烧结后内部残留空洞,实际得到的导热性能相对于金锡焊料烧结后的导热性能未表现出明显优势。

技术实现要素:

4.本发明旨在提供一种低空洞率、高导热纳米银导电胶烧结工艺,能够实现纳米银导电胶组装芯片的低空洞率、高导热率。

5.为达到上述目的,本发明是采用以下技术方案实现的:本发明公开一种低空洞率、高导热纳米银导电胶烧结工艺,包括以下步骤:a、转印,将纳米银导电胶转移至载体形成覆盖区域;b、贴装,将硅片贴装在所述覆盖区域制备成样品,贴装过程中对硅片相对于覆盖区域进行画圈摩擦操作;c、烧结,将所述样品置于加热装置中加热至200

±

5℃后保持温度固化90

±

10min。

6.优选的,所述覆盖区域为连续覆盖区域,覆盖区域的面积为待贴装的硅片的底面积的90%~100%。

7.优选的,步骤a中采用针转印方法将纳米银导电胶转移至载体。

8.进一步的,步骤b中,在对硅片相对于覆盖区域进行画圈摩擦操作直至纳米银导电胶从芯片四周溢出后,对硅片相对于载体施加按压力至硅片平整。

9.优选的,步骤a中采用手工针转印方法将纳米银导电胶转移至载体,所述针为钨针,所述画圈摩擦操作以及施加按压力均采用手工方式。

10.优选的,步骤c中,所述加热装置为电热鼓风干燥箱,在常温状态下将样品放入电热鼓风干燥箱,固化后取出自然冷却。

11.进一步优选的,步骤c中将所述样品在200℃下固化90min。

12.作为一种优选的,所述载体为钼铜载板。

13.进一步优选的,所述硅片尺寸不大于3mm

×

3mm,所述载体为镀金/镀银钼铜载板、镀金/镀银钨铜载板、镀金/镀银无氧铜载板、镀金/镀银铜质壳体、镀金/镀银铝合金制腔体。

14.进一步的,步骤a之前,从冷冻环境中将纳米银导电胶取出后解冻1小时以上。

15.本发明的有益效果如下:1、本发明能够实现纳米银导电胶组装芯片的低空洞率、高导热率。

16.2、本发明无需专用控温设备、无需设置温度梯度,操作简单易实现、成本低。

17.3、本发明贴放芯片时采用画圈摩擦手法,后续烧结时无需专用工装进行加压,有利于芯片保护和成本节约。

附图说明

18.图1为实施例1中按照90%芯片面积点胶后样品照片。

19.图2为实施例2中按照100%芯片面积点胶后样品照片。

20.图3为实施例3中按照95%芯片面积点胶后样品照片。

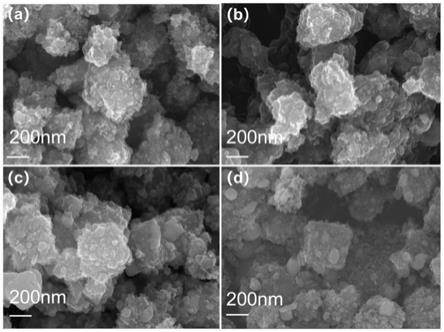

21.图4为实施例1中样品烧结后的x光照片。

22.图5为对比例1中样品贴放时未加画圈摩擦后的样品照片。

23.图6为对比例1中样品烧结后的x光照片。

24.图7为对比例2中样品烧结后的x光照片。

25.图8为(k)系数测试拟合曲线。

26.图9为纳米银装片电路热阻测试结构函数曲线及热阻处理结果示意图。

27.图10为金锡装片电路与热沉干接触进行测试,对比纳米银装片电路干接触的结构函数示意图。

28.图11为干接触时两颗电路热阻测试结构示意图。

具体实施方式

29.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图,对本发明进行进一步详细说明。

30.实施例1将京瓷ct2700r7品牌纳米银导电胶从冷冻冰柜中取出,解冻1h待用;当然,也可以采用其他纳米银导电胶。

31.将钼铜载板固定在带粘性的芯片盒中,使用钨针蘸取纳米银导电胶并转移至钼铜载板2,用镊子夹取硅片贴放至钼铜载板已点纳米银导电胶的覆盖区域,并进行画圈摩擦,观察到硅片四周溢出纳米银导电胶时,轻轻按压,使硅片平整完成贴放,其中,画圈摩擦是指在硅片与覆盖区域接触的情形下,周向移动硅片。

32.将样品在常温下放置在电热鼓风干燥箱中,随后电热鼓风干燥箱温度设置为200℃,待电热鼓风干燥箱温度稳定后保温固化90min,固化完成后取出样品自然冷却即完成纳米银导电胶烧结。

33.其中,纳米银导电胶转移按照90%硅片面积点胶,如图1所示,外观可见芯片1贴放后四周可见溢出纳米银导电胶3,符合gjb548b-2005中目检接收标准。

34.如图4所示,可见芯片范围内有分散的小空洞,无贯穿大空洞。剪切力测试失效模式为硅片碎裂,界面完好,测试合格。烧结出的样品可实现空洞率小于10%,剪切力大于芯片材料强度。

35.温度升至200℃后,保温90min的烧结工艺适用于3mm*3mm及以下尺寸的芯片组装至镀金/镀银钼铜载板、镀金/镀银钨铜载板、镀金/镀银无氧铜载板、镀金/镀银铜质壳体体、镀金/镀银铝合金制腔体等。

36.实施例2本实施例与实施例1的区别之处在于:纳米银导电胶转移按照100%硅片面积点胶;其他操作相同,故不赘述。

37.如图2所示,本实施例外观可见硅片贴放后四周可见溢出纳米银导电胶,符合gjb548b-2005中目检接收标准。

38.烧结后的样品,其芯片范围内有分散的小空洞,无贯穿大空洞。剪切力测试失效模式为硅片碎裂,界面完好,测试合格。烧结出的样品可实现空洞率小于10%,剪切力大于芯片材料强度。

39.实施例3本实施例与实施例1、2的区别之处在于:纳米银导电胶转移按照95%硅片面积点胶;其他操作相同,故不赘述。

40.如图3所示,本实施例外观可见硅片贴放后四周可见溢出纳米银导电胶,符合gjb548b-2005中目检接收标准。

41.烧结后的样品,其芯片范围内有分散的小空洞,无贯穿大空洞。剪切力测试失效模式为硅片碎裂,界面完好,测试合格。烧结出的样品可实现空洞率小于10%,剪切力大于芯片材料强度。

42.对比例1将京瓷ct2700r7品牌纳米银导电胶从冷冻冰柜中取出,解冻1h待用。将钼铜载板2固定在带粘性的芯片盒中,使用钨针蘸取纳米银导电胶并转移至钼铜载板,用镊子夹取硅片1贴放至已点纳米银导电胶区域,轻轻按压中心位置,使硅片平整完成贴放。将样品在常温下放置在电热鼓风干燥箱中,随后电热鼓风干燥箱温度设置为200℃,待电热鼓风干燥箱温度稳定后保温固化90min,固化完成后取出样品自然冷却即完成纳米银导电胶烧结。

43.图5为贴片完成后的外观照片,可见未经摩擦同样可达到四周溢出纳米银导电胶3的效果,外观检验合格。

44.图6为未经摩擦的样品烧结后x光形貌,可见图中空洞数量较多,且面积较大,右下角部分可见明显分界面疑似未接触纳米银导电胶。

45.与实施例1、2、3对比可见,画圈摩擦的的贴放手法可使硅片受力均匀,充分接触纳米银导电胶,有利于空洞减少,提高烧结质量。

46.对比例2将京瓷ct2700r7品牌纳米银导电胶从冷冻冰柜中取出,解冻1h待用。将钼铜片固定在带粘性的芯片盒中,使用钨针蘸取纳米银导电胶并转移至钼铜载板,用镊子夹取硅片贴放至已点纳米银导电胶区域,并进行画圈摩擦,观察到硅片四周溢出纳米银导电胶时,轻轻按压,使硅片平整完成贴放。将电热鼓风干燥箱设置为200℃使其升温,待温度稳定后将

样品放置在电热鼓风干燥箱中保温固化90min,固化完成后取出样品自然冷却即完成纳米银导电胶烧结。

47.图7 为直接在200℃下固化烧结的样品x光照片,可见在硅片中间区域有大面积空洞并且非常集中,与图4相比,烧结质量下降严重。由于样品从常温下放入200℃电热鼓风干燥箱中,样品升温速率很快,因此纳米银导电胶中的有机物受热产生的气体没有足够的时间排出从而在中间位置形成空洞。

48.与实施例1、2、3对比可见,在常温下将样品放入电热鼓风干燥箱,使样品随炉升温的烧结方法可降低样品的升温速率,留出足够的排气时间,从而降低烧结后空洞率,提高烧结质量。

49.实施例4本实施例是热阻测试报告,具体如下:1 、 测试要求对纳米银装片电路与金锡装片电路进行热阻测试,利用结构函数剥离装片材料的热阻。

50.2 、 测试原理及测试设备2.1 测试原理根据 jedec jesd51-1、jesd51-14 热测试标准进行。

51.2.2 测试设备t3ster2000 热阻测试仪。

52.3 、 电路信息根据输入信息表,将器件电源与地反接,所构成的寄生二极管作为温敏二极管,对器件正向通电使之工作发热,反向利用寄生二极管测温。二极管正向压降作为温敏参数(k 系数)。

53.4 、 温敏系数(k 系数)测试将器件的电源及地反接,作为温敏二极管,二极管正向压降作为温敏参数(k系数)。

54.4.1 测试环境采用 t3ster 干式温控仪提供恒温环境,如下图 3 所示,将样品放到数字干式恒温槽中,温控仪可控温度范围-25℃~125℃。

55.4.2 测试参数环境温度:30℃~70℃,每 10℃采集一次二极管正向压降。

56.4.3 测试结果图 8 为测试电路 k 系数测试拟合曲线,测得金锡装片电路温敏系数(k)为-1.4379mv/℃,纳米银装片电路温敏系数为-1.4427mv/℃。

57.5 、 热阻测试5.1 测试方法根据 jedec jesd51-14 结构函数热阻测试方法。首先将纳米银装片电路进行两次测试,第一次与热沉干接触,第二次与热沉通过导热硅脂接触,通过对比结构函数分离点得到外壳到环境的热阻。再将金锡装片电路与热沉干接触进行测试,对比纳米银装片电路

干接触的结构函数,剥离出两种装片材料的自身热阻。

58.5.2 测试结果将纳米银装片电路进行干接触与硅脂接触测试,测试电流为 0.6a。如图9 所示,干接触测试得到的结构函数为蓝色,硅脂接触得到的结构函数为红色,分离点在外壳与热沉之间。故分离点之后的为壳到环境的热阻,分离点之前的为结到壳的热阻。从图中能够看出:壳到环境的热阻为 0.7204℃/w。

59.将金锡装片电路与热沉干接触进行测试,对比纳米银装片电路干接触的结构函数,如图 10、图11所示。

60.由于两颗电路外壳尺寸、测试热沉尺寸都相同,故此处认为两颗电路壳到环境的热阻相同,都为 0.7204℃/w。

61.a1 与 b1 为芯片与装片材料(金锡或纳米银)的接触界面;该点之前都是芯片内部的热阻,由 a1 与 b1 点之后斜率出现明显差异判定该点位置。

62.a2 与 b2 为外壳与热沉的接触界面;该点由结构函数最终点向前减去壳到环境热阻 0.7204℃/w 得到。

63.a3 与 b3 为装片材料与外壳的接触界面。由于装片材料与热沉热导率有一定差距,故在结构函数上呈现出不同的斜率,该点位置由 a1/b1 与 a2/b2 之间斜率突变位置确定。

64.故经计算,金锡材料的热阻为 a1 到 a3 之间的热阻为:0.603 0.496 0.7204 0.555=2.3744℃/w纳米银材料的热阻为 b1 到 b3 之间的热阻为 0.603℃/w。

65.上述测试说明了纳米银装片电路的高导热率。

66.当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。