1.本发明涉及加法器技术领域,特别是涉及一种21比特浮点加法器。

背景技术:

2.加法运算是其他运算的基础,通过提高加法器的运算性能,可以更有效地提高整个运算电路的性能,从而提高卷积神经网络的速度和能效,最终提高芯片性能。目前,加法器的运算性能还有待提高。

技术实现要素:

3.本发明的目的是提供一种21比特浮点加法器,提高了加法器的工作频率。

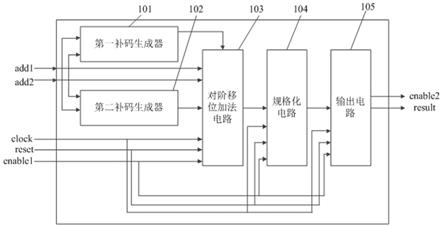

4.为实现上述目的,本发明提供了如下方案:一种21比特浮点加法器,包括:对阶移位加法电路、规格化电路和输出电路;所述对阶移位加法电路的输出连接所述规格化电路的输入,所述规格化电路的输出连接所述输出电路的输入;所述对阶移位加法电路用于对加数和被加数进行对阶移位加法,获得临时加法结果;所述规格化电路用于根据所述临时加法结果进行符号位计算和整数部分的移位,获得临时输出结果;所述输出电路用于对所述临时输出结果进行规格化后输出;所述加数和所述被加数均为21比特数,所述21比特数按位从高到低依次包括1位符号位、6位阶码、4位整数部分和10位小数部分;所述21比特数的十进制表达式为:;其中,mix21

(10)

表示所述21比特数的十进制,s表示符号位,e表示阶码,i表示整数部分,m表示小数部分。

5.可选地,所述对阶移位加法电路对所述加数和所述被加数进行对阶移位加法,获得临时加法结果,具体包括:将所述加数的阶码和所述被加数的阶码中最大阶码记为第三阶码;若所述加数的阶码小于所述被加数的阶码,则所述加数的对阶移位拼接结果为所述加数的整数部分和小数部分的拼接右移所述加数的阶码与所述被加数阶码的差值,所述被加数的对阶移位拼接结果为所述被加数的整数部分和小数部分的拼接;若所述加数的阶码大于所述被加数的阶码,则所述加数的对阶移位拼接结果为所述加数的整数部分和小数部分的拼接,所述被加数的对阶移位拼接结果为所述被加数的整数部分和小数部分的拼接右移所述加数的阶码与所述被加数阶码的补码之和;若所述加数的阶码等于所述被加数的阶码,则所述加数的对阶移位拼接结果为所述加数的整数部分和小数部分的拼接,所述被加数的对阶移位拼接结果为所述被加数的整数部分和小数部分的拼接;

若所述加数的符号位与所述被加数的符号位相同,则临时加法结果为所述加数的对阶移位拼接结果与所述被加数的对阶移位拼接结果之和;若所述加数的符号位为0,则所述加数的对阶移位拼接结果的补码等于所述加数的对阶移位拼接结果,若所述加数的符号位为1,则所述加数的对阶移位拼接结果的补码为所述加数的对阶移位拼接结果取反加1;若所述被加数的符号位为0,则所述被加数的对阶移位拼接结果的补码等于所述被加数的对阶移位拼接结果,若所述被加数的符号位为1,则所述被加数的对阶移位拼接结果的补码为所述被加数的对阶移位拼接结果取反加1;若所述加数的符号位与所述被加数的符号位不相同,则临时加法结果为所述加数的对阶移位拼接结果的补码与所述被加数的对阶移位拼接结果的补码之和。

6.可选地,所述规格化电路根据所述临时加法结果进行符号位计算和整数部分的移位,获得临时输出结果,具体包括:当所述加数和所述被加数均为正数时,待计算符号位为0;当所述加数和所述被加数均为负数时,待计算符号位为1;当所述加数和所述被加数为一个正数一个负数时,待计算符号位为所述加数的符号位、所述被加数的符号位和所述临时加法结果最高位的和;当所述加数的符号位和所述被加数的符号位相同时,若所述临时加法结果的最高位为1且所述第三阶码为111111时,所述临时输出结果为所述临时加法结果,若所述临时加法结果的最高位为1且所述第三阶码不是111111时,所述临时输出结果为所述临时加法结果向右移4位;当所述加数的符号位和所述被加数的符号位不相同时,若所述临时加法结果的最高位为1,所述临时输出结果为所述临时加法结果向右移4位;当所述加数的符号位和所述被加数的符号位不相同时,若所述临时加法结果的最高位不为1,判断所述临时加法结果中从次高位开始的低4位是否为0,若为0,则所述临时输出结果为所述临时加法结果向左移4位,若不为0,则所述临时输出结果为所述临时加法结果。

7.可选地,所述输出电路对所述临时输出结果进行规格化后输出,具体包括:若所述临时输出结果的低14位都为0,则所述输出电路的输出为0_000000_0000_0000000000;若所述临时输出结果的低14位不全为0,且当待计算符号位和临时输出结果的最高位均是0时,则所述输出电路的输出为待计算符号位、所述第三阶码与所述临时输出结果的低14位的拼接;若所述临时输出结果的低14位不全为0,且当待计算符号位为0和临时输出结果的最高位是1时,则所述输出电路的输出为0_111111_0000_0000000000;若所述临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的最高位是0,所述加数的符号位与所述被加数的符号位相同时,所述输出电路的输出为待计算符号位、所述第三阶码与所述临时输出结果的低14位的拼接;若所述临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的最高位是0,所述加数的符号位与所述被加数的符号位不相同时,所述输出电路的输出为待计算符号位、所述第三阶码与所述临时输出结果的低14位取反加1的拼接;若所述临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的

最高位是1,所述输出电路的输出为1_111111_0000_0000000000。

8.可选地,还包括第一补码生成器和第二补码生成器;所述第一补码生成器的输出和所述第二补码生成器的输出均连接所述对阶移位加法电路,所述第一补码生成器用于计算加数的整数部分与小数部分拼接的补码,所述第一补码生成器还用于计算被加数的整数部分与小数部分拼接的补码;所述第二补码生成器用于计算被加数阶码的补码。

9.可选地,还包括时钟信号,所述时钟信号分别连接所述对阶移位加法电路、所述规格化电路和所述输出电路。

10.可选地,还包括使能输入信号,所述使能输入信号分别连接所述对阶移位加法电路、所述规格化电路和所述输出电路。

11.可选地,还包括复位信号,所述复位信号分别连接所述对阶移位加法电路、所述规格化电路和所述输出电路。

12.根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明加数和被加数均为21比特数,21比特数按位从高到低依次包括1位符号位、6位阶码、4位整数部分和10位小数部分,使得指数位更少,移位次数更少,速度更快,从而提高了加法器的工作频率。

附图说明

13.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

14.图1为本发明一种21比特浮点加法器结构示意图;图2为本发明一种21比特浮点加法器操作过程示意图。

具体实施方式

15.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

16.本发明的目的是提供一种21比特浮点加法器,提高了加法器的工作频率。

17.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

18.图1为本发明一种21比特浮点加法器结构示意图,如图1所示,一种21比特浮点加法器,包括:对阶移位加法电路103、规格化电路104和输出电路105;对阶移位加法电路的输出连接规格化电路104的输入,规格化电路104的输出连接输出电路105的输入;对阶移位加法电路103用于对加数和被加数进行对阶移位加法,获得临时加法结果;规格化电路104用于根据临时加法结果进行符号位计算和整数部分的移位,获得临时输出结果;输出电路105用于对临时输出结果进行规格化后输出。

19.加数和被加数均为21比特数,21比特数按位从高到低依次包括1位符号位、6位阶

码、4位整数部分和10位小数部分。

20.21比特数的十进制表达式为:;其中,mix21

(10)

表示21比特数的十进制,s表示符号位,e表示阶码,i表示整数部分,m表示小数部分。

21.一种21比特浮点加法器还包括第一补码生成器101、第二补码生成器102,第一补码生成器101的输出和第二补码生成器102的输出均连接对阶移位加法电路103,第一补码生成器101用于计算加数的整数部分与小数部分拼接的补码,第一补码生成器101还用于计算被加数的整数部分与小数部分拼接的补码;第二补码生成器102用于计算被加数阶码的补码。

22.一种21比特浮点加法器还包括时钟信号,时钟信号分别连接对阶移位加法电路103、规格化电路104和输出电路105。

23.一种21比特浮点加法器还包括使能输入信号,使能输入信号分别连接对阶移位加法电路103、规格化电路104和输出电路105。

24.一种21比特浮点加法器还包括复位信号,复位信号分别连接对阶移位加法电路103、规格化电路104和输出电路105。

25.输入信号包括时钟信号clock、复位信号reset、使能信号enable1、两个21位的加数add1和被加数add2,输出信号包括使能输出信号enable2和加法结果result。21比特浮点加法器包括5个组成部分:第一补码生成器101、第二补码生成器102、对阶移位加法电路103、规格化电路104和输出电路105。

26.对阶移位加法电路103的功能是进行阶码移位操作、整数小数移位操作、符号位计算以及得到加法结果。

27.规格化电路104的功能是针对整数部分为0进行阶码相加、尾数移位。

28.输出电路105的功能是根据第二步规格化的结果进行边界情况的讨论,进而得到整个21bit加法器电路的加法结果信号和输出使能信号。

29.21比特浮点加法器(21bit加法器)用mix21加法器表示。21bit加数或21bit被加数定义为mix21数据类型,mix21数据类型如表1所示,21bit共分为四部分,符号位(s)、阶码(e)、整数部分(i)和小数部分(m),最高位是符号位,0表示正数,1表示负数;19位到14位是阶码;13位到10位是整数部分;低10位是小数部分。

30.表1 mix21数据类型类型seimbit2019:1413:109:0位宽16410定义符号位阶码整数部分小数部分条件任意数值任意数值任意非0值任意数值根据表1的数据类型,可以计算出mix21的十进制表达式:;

也就是:。

31.例如,mix21数据类型表示一个数字为:0_100001_0001_1000000000,根据表1可以知道:s=1,e=100001,i=0001,m=1000000000,则:针对表1中mix21的数据类型条件:s为任意数值,e为任意数值,i为任意非0值,m为任意数值。在此情况下,对于mix21的数据类型表达出现歧义的有6种边界情况。

32.例如十进制数0,表达为表1中mix21的数据类型时,s为任意值,e为任意值,i为0,m为0。会出现1_100001_0000_0000000000和0_100101_0000_0000000000都表示0的情况,在此固定0表示为0_000000_0000_0000000000。

33.再例如当一个十进制正数值大于mix21的最大正数表示范围时(2

124

×

15.9990234),此时s为0,e为最大值63,i为最大值15,m为最大值1023都无法表示该数字。则将这个数固定为 infinity表示为0_111111_0000_0000000000。

34.设置mix21的数据类型的边界表达如下:0仅能表达为以下表2格式。

35.表2 mix21的数据类型中0的表达类型seim数值0000nan,用于表示该数非有效值,如表3所示。用于跳过运算。

36.表3 mix21的数据类型中nan的表达类型seim数值03200 infinity,即无法用该类型表示的正上溢值,任意正数除以0可得该值, infinity如表4所示。

37.表4 mix21的数据类型中 infinity的表达类型seim数值06300-infinity,即无法用该类型表示的负上溢值,任意负数除以0可得该值,-infinity如表5所示。

38.表5 mix21的数据类型中-infinity的表达

类型seim数值16300 min,即无法用该类型表示的正下溢值,如表6所示。

39.表6 mix21的数据类型中 min的表达类型seim数值0100-min,即无法用该类型表示的负下溢值,如表7所示。

40.表7 mix21的数据类型中-min的表达类型seim数值1100本发明21比特浮点加法器的操作过程如图2所示,加法实际运算过程通过最少三个周期完成操作,每一步操作都是在时钟信号的上升沿进行。

41.本发明21比特浮点加法器首先到初始化状态(3’d111),根据时钟信号、复位信号、使能信号、两个21位的加数和被加数来初始化加数的符号位(s1)、阶码(e1)、整数部分(i1)、小数部分(m1),被加数的符号位(s2)、阶码(e2)、整数部分(i2)、小数部分(m2)。

42.本发明21比特浮点加法器实际运算的过程包含三个周期为3’d001,3’d010,3’b100。

43.第一个周期(3’d001)进行对阶移位加法电路103计算,即阶码的计算、根据阶码计算结果进行整数和小数的移位操作。

44.对阶移位加法电路103对加数和被加数进行对阶移位加法,获得临时加法结果,具体包括:将加数的阶码e1和被加数的阶码e2中最大阶码记为第三阶码e3。

45.若加数的阶码e1小于被加数的阶码e2。则加数的对阶移位拼接结果reg_a为加数的整数部分i1和小数部分m1的拼接后,右移加数的阶码e1与被加数阶码e2的补码之和,即reg_a为i1和m1拼接后向右移位e1与e2的差值位得到。被加数的对阶移位拼接结果reg_b为被加数的整数部分i2和小数部分m2的拼接。

46.若加数的阶码e1大于被加数的阶码e2。则加数的对阶移位拼接结果reg_a为被加数的整数部分i1和小数部分m1的拼接。被加数的对阶移位拼接结果reg_b为加数的整数部分i2和小数部分m2的拼接后,右移加数的阶码e1与被加数阶码e2的补码之和,即reg_b为i2和m2拼接后向右移位e1与e2的差值位得到。

47.若加数的阶码e1等于被加数的阶码e2。则加数的对阶移位拼接结果reg_a为被加数的整数部分i1和小数部分m1的拼接。被加数的对阶移位拼接结果reg_b为被加数的整数部分i2和小数部分m2的拼接。

48.根据加数的对阶移位拼接结果reg_a计算其补码com_a,根据被加数的对阶移位拼接结果reg_b计算其补码com_b。

49.若加数的符号位s1为0,则其补码com_a等于本身reg_a,即com_a=reg_a,若加数的符号位s1为1,则其补码com_a为reg_a取反加1;同样地,若被加数的符号位s2为0,则com_b=reg_b。若被加数的符号位s2为1,则com_b为reg_b取反加1。

50.若加数的符号位s1与被加数s2的符号位相同,则临时加法结果temp_add为加数的

对阶移位拼接结果reg_a与加数的对阶移位拼接结果reg_a之和。

51.若加数的符号位s1与被加数的符号位s2不相同,则临时加法结果temp_add为加数的对阶移位拼接结果reg_a的补码com_a与被加数的对阶移位拼接结果reg_a的补码com_b之和。

52.第二个周期(3’d010)是规格化状态,进行符号位计算、规格化整数部分的移位操作、阶码累加的操作。

53.规格化电路104根据临时加法结果进行符号位计算和整数部分的移位,获得临时输出结果,具体包括:当加数和被加数均为正数时,待计算符号位s3为0;当加数和被加数均为负数时,待计算符号s3位为1;当加数和被加数为一个正数一个负数时,待计算符号位s3为加数的符号位s1、被加数的符号位s2和临时加法结果最高位的和。

54.当加数的符号位s1和被加数的符号位s2相同时,若临时加法结果的最高位为1且第三阶码e3为111111时,临时输出结果为临时加法结果,若临时加法结果的最高位为1且第三阶码e3不是111111时,临时输出结果为临时加法结果向右移4位。

55.当加数的符号位s1和被加数的符号位s2不相同时,若临时加法结果的最高位为1,临时输出结果为临时加法结果向右移4位。

56.当加数的符号位s1和被加数的符号位s2不相同时,若临时加法结果的最高位不为1,判断临时加法结果中从次高位开始的低4位是否为0,若为0,则临时输出结果为临时加法结果向左移4位,若不为0,则临时输出结果为临时加法结果。

57.第三个周期(3’d100)是输出状态,进行规格化输出,由于数据类型中边界情况的讨论和对整数部分的定义,需要针对临时加法的结果再进行规格化的输出得到最终结果f。

58.输出电路105对临时输出结果进行规格化后输出,具体包括:若临时输出结果的低14位都为0,则输出电路105的输出为0_000000_0000_0000000000。

59.若临时输出结果的低14位不全为0,且当待计算符号位和临时输出结果的最高位均是0时,则输出电路105的输出为待计算符号位、第三阶码与临时输出结果的低14位的拼接。

60.若临时输出结果的低14位不全为0,且当待计算符号位为0和临时输出结果的最高位是1时,则输出电路105的输出为0_111111_0000_0000000000。

61.若临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的最高位是0,加数的符号位与被加数的符号位相同时,输出电路105的输出为待计算符号位、第三阶码与临时输出结果的低14位的拼接。

62.若临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的最高位是0,加数的符号位与被加数的符号位不相同时,输出电路105的输出为待计算符号位、第三阶码与临时输出结果的低14位取反加1的拼接。

63.若临时输出结果的低14位不全为0,且当待计算符号位为1和临时输出结果的最高位是1,输出电路105的输出为1_111111_0000_0000000000。

64.下面简述本发明21比特浮点加法器实际运算的三个周期。

65.第一个周期(3’d001)进行阶码的计算、根据阶码计算结果进行整数和小数的移位

操作。

66.对阶移位加法阶段,计算加法结果的阶码为e1和e2中较大的一个,记为e3。对加数的整数部分、小数部分进行移位标记为reg_a,若加数阶码e1大于被加数e2,则reg_a为i1和m1拼接得到。若e1小于e2,则reg_a为i1和m1拼接后向右移位e1与e2的差值位得到。

67.对被加数的整数部分、小数部分进行移位标记为reg_b,若加数阶码e1小于被加数e2,则reg_b为i2和m2拼接得到。若e1大于e2,则reg_b为i2和m2拼接后向右移位e1与e2的差值位得到。计算reg_a和reg_b的补码结果分别为com_a和com_b,com_a和com_b根据reg_a和reg_b的符号位是否为1进行操作,若符号位为1,则reg_a和reg_b取反加1得到com_a和com_b。若符号位为0,则com_a和com_b为reg_a和reg_b本身。相加的临时结果结果为temp_add(temp_add= (s1==s2)reg_a reg_b : com_a com_b),若s1和s2同号,则临时结果结果为reg_a和reg_b的和;若s1和s2异号,则临时结果结果为com_a和com_b的和。接下来跳转到规格化状态。

68.第二个周期(3’d010)是规格化状态,进行符号位计算、规格化整数部分的移位操作、阶码累加的操作。

69.计算加法结果符号位s3,当加数和被加数均为正的时候s3=0,当加数和被加数均为负的时候s3=1,当加数和被加数一正一负的时候s3为加数符号位、被加数符号位、临时加法结果最高位的和。

70.根据临时加法结果temp_add的最高位是否为1判断临时加法结果是否需要移位。

71.加数和被加数同符号:当temp_add的最高位为1时,若阶码e3为最大值(111111)时,直接跳转到第三周期输出状态、输出使能信号拉高。若e3不是最大值,则进行补零操作,将临时加法结果temp_add向右移位4位,得到新的temp_add((temp_add[regwidth:0]= {4'b0,temp_add[mwidth:0]})),跳转到输出状态、输出使能信号拉高。

[0072]

加数和被加数一正一反:当temp_add的最高位为1时,将temp_add进行补零操作,将临时加法结果temp_add向右移位4位,得到新的temp_add(temp_add[regwidth:0]= {4'b0,temp_add[mwidth:0]})。temp_add的最高位不为1,判断temp_add从次高位开始的低4位是否为0。如果是0,则左移4位,反之跳转到输出状态,输出使能信号拉高。

[0073]

第三个周期(3’d100)是输出状态,进行规格化输出,由于数据类型中边界情况的讨论和对整数部分的定义,需要针对临时加法的结果再进行规格化的输出得到最终结果f。

[0074]

输出使能信号为高进行操作:若临时加法结果temp_add的低14位都为0,则输出f为0_000000_0000_0000000000,若临时加法结果temp_add的低14为不全为0,则通过符号位s3和临时加法结果temp_add最高位的情况来判断输出。当结果符号位s3和临时加法结果temp_add最高位为00时,则输出f为s3,e3和temp_add低14位拼接结果;当符号位s3和临时加法结果temp_add最高位为01时,则输出f为0_111111_0000_0000000000;当符号位s3和临时加法结果temp_add最高位为10时,若s1和s2同号则输出f为s3,e3和temp_add低14位的拼接结果,若s1和s2异号则输出f为s3、e3和temp_add低14位取反加1的拼接结果。当符号位s3和临时加法结果temp_add最高位为11时,则输出f为1_111111_0000_0000000000。

[0075]

实施例1:十进制计算( 240) ( 24)=( 264)。 240和 24根据mix21数据类型表示如表8所示。

[0076]

表8 240和 24的mix21数据类型表示

十进制mix21数据类型表示 2400_100001_1111_0000000000 240_100001_0001_1000000000第一个周期,对阶移位加法阶段, 240的阶码减去 24的阶码,差值为0,则e3=100001。reg_a=com_a=1111_0000000000,reg_b=com_b=0001_1000000000,两个补码相加的临时结果结果为temp_add=1_0000_1000000000。

[0077]

第二个周期,加数和被加数均为正,加法结果符号位s3=0。规格化移位得到temp_add= 000 0100 0010 0000。

[0078]

第三个周期,f= 1000 1000 0100 0010 0000。

[0079]

实施例2:十进制计算( 24) (-1.125)=( 22.875)。 24和-1.125根据mix21数据类型表示如表9所示。

[0080]

表9 24和-1.125的mix21数据类型表示十进制mix21数据类型表示 240_100001_0001_1000000000-1.1251_100000_0001_0010000000第一个周期,对阶移位加法阶段, 24的阶码减去-1.125的阶码,则e3=000001。 24的整数部分和小数部分不需要进行移位,则reg_a=com_a= 0001_1000000000。-1.125的整数部分和小数部分进行移位,结果为reg_b= 0000_0001001000,补码为com_b= 1111_1110111000。两个补码相加的临时结果结果为temp_add= 1_0001_0110111000。

[0081]

第二个周期,加数和被加数一正一负,加法结果符号位加数符号位、被加数符号位、临时加法结果最高位的和,s3=1 0 1=0。

[0082]

第三个周期,根据s3和temp_add决定输出。

[0083]

{s3,temp_add}=00,则:f={s3,e3,temp_add[regwidth-1:0]}= 0_100001_0001_0110111000。

[0084]

至此,得到计算结果f=0_100001_0001_0110111000,通过mix21的表达式计算即为 22.875。

[0085]

本发明中,对21bit数据类型进行设计、经过mobilenet网络进行推测、硬件电路的设计、硬件语言进行描述,最终对电路进行仿真和综合。可以发现,21bit加法器包括两部分优点。

[0086]

本发明定义一种新的数据类型,使得指数位更少,移位次数更少,速度更快。通过更简单的补码生成电路减少芯片面积,提高工作频率。本发明21比特浮点加法器适用于卷积神经网络,提高卷积神经网络的速度和能效,最终提高芯片性能。

[0087]

因此本发明新数据类型的21比特加法器具有更高的工作效率。

[0088]

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

[0089]

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。