基于多电场模型的时钟驱动fpga芯片全局布局方法

技术领域:

:1.本发明属于电子电气设计自动化(electronicdesignautomation,以下简称eda)

技术领域:

:,涉及芯片集成电路物理设计中针对现场可编程门阵列(fieldprogrammablegatearray,以下简称fpga)的全局布局技术,具体涉及一种基于多电场模型系统的时钟驱动fpga全局布局方法。

背景技术:

::2.fpga是一种在硅片上进行预先设计的具有可编程特性的半定制集成电路芯片。在fpga芯片制造过程中,制造厂商会预先在硅片上设计出可编程门逻辑器件;在客户使用过程时,设计人员可以通过硬件描述语言(verilog或者vhdl)描述定制化的逻辑电路,然后利用逻辑综合,布局和布线等eda软件,将定制化的逻辑电路快速刻录到fpga上进行测试。fpga能够按照设计人员的需求快速配置为指定的电路结构,让客户能够在芯片开发前期不必依赖流片周期长,一次性工程费用大的专用集成电路(applicationspecificintegratedcircuit,以下简称asic)芯片,因此fpga被广泛应用在原型验证,工业控制,通信,汽车电子,数据中心和航空航天等领域。3.fpga全局布局技术是指,给定电路网表和目标fpga芯片的布局限制,计算器件在芯片上的位置,使得通过接下来的合法化,详细布局和布线阶段后得到的布线的线长最短。由于fpga芯片的异构性质,相比于asic芯片,针对fpga芯片的全局布局算法难度更高。fpga的异构性质体现在,制造厂商在硅片上预先设计的多种可编程逻辑器件在fpga芯片上成列分布,且器件的数量、位置分布不均;并且由于局部可编辑逻辑器件的信号线共用问题,在局部区域部分逻辑器件的不能任意组合,这些都大大增加了针对fpga全局布局算法的难度。4.而随着现代fpga集成度的提高和性能的多元化,fpga芯片对布局的要求越来越复杂,其中包括在布局阶段对时钟信号路由的考虑。为了减少后期进行时序分析中的时钟偏移(clockskew),在现代高性能fpga芯片的制造过程中,往往为了时钟信号设计了专门的时钟路由通道(clockroutingtrack),以提高电路的运行频率。但是,时钟路由通道的分布也对布局阶段器件的分布提出了限制。以赛灵思(简称xilinx)设计的ultrascalevu095芯片为例,其把整个fpga芯片版图划分为5×8个时钟区域(clockregion),通过每个时钟区域的时钟信号个数最多为24。这个要求在同一个时钟区域内的所有器件的时钟信号种类个数不能超过24个,这对fpga全局布局算法提出了更高的要求。5.现有的传统fpga全局布局算法存在以下的不足之处:(一)现有的fpga布局工具在大规模fpga布局问题上效果不佳。现有的fpga布局工具主要使用基于二次规划的全局布局算法,然而随着芯片规模和芯片复杂度的不断增加,在大规模的fgpa布局问题上基于二次规划的fpga全局布局算法不能取得很好的布局质量。6.(二)现有的fpga全局布局算法较少在全局布局阶段考虑对时钟信号路由的限制。由于在布局阶段缺乏对时钟信号路由的限制,在后期的合法化阶段需要对部分违反时钟信号路由的器件的位置再进行调整,这会影响整个布局结果的质量。7.综上所述,现有的传统fpga全局布局算法在大规模fpga布局问题上难以取得很好的布局结果,并且由于在全局布局阶段较少考虑对时钟信号路由的限制,在布局后期的合法化阶段中对违反时钟路由信号的器件的调整会影响布局质量。技术实现要素:8.为了克服上述现有技术的不足,本发明提出了一种基于多电场模型的时钟驱动fpga芯片的全局布局算法。该算法针对fpga布局的异构性质,对多种不同的器件类型分别建立了电场模型,用于对器件的密度分布进行建模;并且通过时钟路由分配算法和二次罚函数的方法,在全局布局阶段以平滑化的方式引入了时钟路由的限制,使得该算法可以在全局布局阶段产生满足时钟路由限制的布局结果,提升fpga芯片全局布局的质量和效果。9.在本发明中,将fgpa布局问题通过增广拉格朗日方法转化成一个非凸优化问题,并使用内思特罗夫动量法(nesterovmomentummethod)进行求解。并且,本发明提出的算法采用适合gpu进行并行运算的算法结构,能够充分利用gpu进行加速计算,从而在全局布局阶段高效地获得较好的满足时钟路由限制的布局结果。10.本发明的技术方案是:一种基于多电场模型的时钟驱动fpga芯片的全局布局方法,分别对多种不同的器件类型建立了电场模型,来对多种器件的密度分布进行高效建模,并通过时钟路由分配算法和二次罚函数的方法在全局布局的优化问题中以平滑化的方式引入时钟路由的限制,使得可以在全局布局阶段生成有利于接下来合法化阶段的满足时钟路由限制的布局结果。11.在本发明中,输入包括逻辑综合后得到的电路网表和fpga芯片的布局限制,其中的布局限制包括时钟路由限制。本发明包括如下步骤:a.建立优化模型。12.利用可微的加权平均线长模型(weightedaveragewirelength,以下简称wawl)模型来作为布线线长的近似;针对多种不同的器件类型,分别建立了不同器件类型的电场模型,用于对不同器件类型的密度分布进行建模;同时,利用时钟路由分配算法,在优化目标中加入光滑化的二次时钟罚函数项,从而把时钟驱动的fpga布局问题建模成一个带约束非凸优化问题。13.b.利用增广拉格朗日方法(augmentedlagrangianmethod)将该带约束非凸优化问题转化为无约束非凸优化问题。对于原优化问题的三个约束,即时钟路由约束,器件可路由性约束和器件密度分布约束,通过利用一个嵌套优化框架来统一求解,该嵌套优化框架如下:b1.判断是否满足时钟路由约束,并更新时钟乘子。14.b2.判断是否存在路由拥塞问题、是否满足器件可路由性约束,并调整器件面积。15.b3.判断器件密度分布是否足够小、是否满足器件密度分布约束,并调整密度乘子。16.b4.在上述的b1,b2,b3步骤后,无约束优化问题中时钟乘子,器件面积和密度乘子被确定,使用内思特罗夫动量法对优化问题进行求解,直到优化问题完全收敛。17.通过上述步骤,即可以生成一个考虑到时钟路由限制的布局结果,并且该算法兼具较好的运行效率和结果质量,能在相对较短的时间内生成较好的考虑到时钟路由限制的布局结果。18.与现有技术相比,本发明的有益效果在于:本发明提供了一种高效的基于多电场系统的时钟驱动fpga全局布局算法,分别对多种不同的器件类型建立了电场模型来对器件的密度分布进行高效建模,并通过时钟路由分配算法和二次罚函数的方法在全局布局的优化问题中以平滑化的方式引入时钟路由的限制,将fpga布局问题转化成带约束非凸优化问题,并通过高效增广拉格朗日方法进行求解,从而获得质量较好的考虑到时钟路由限制的fpga布局结果。19.同时,该算法的计算模型多为向量化操作,具有可充分利用gpu进行并行加速的计算结构,因此具有良好的计算效率和布局结果质量。附图说明20.图1为本发明具体实施例中采用的fpga芯片的片上资源分布的简化示意图;其中,clb(configurablelogicblock)site为可编程逻辑单元,dsp(digitalsignalprocessing)site为数字信号处理单元,io(input/output)site为输入/输出单元,bram(blockram)site为块存储单元。21.图2为本发明具体实施采用的本发明提出了一种基于多电场模型的时钟驱动fpga全局布局算法的流程框图。具体实施方式22.下面结合附图,通过实施例进一步描述本发明,但不以任何方式限制本发明的范围。23.本发明提供的高效的基于多电场系统的时钟驱动fpga全局布局算法,输入包括电路网表和fpga芯片布局限制,输出考虑到时钟路由限制的fpga全局布局结果。24.以下先提供本发明输入的描述。在本发明中,电路网表用表示,其中表示器件集合,表示器件之间的超边集合。注意在fpga布局问题中,一个超边可以同时连接多个器件。各器件有自己的类型,在该实施例中,器件可能的类型为查找表(look-uptable,以下简称lut),触发器(flipflop,以下简称ff),数字信号处理器件dsp(digitalsignalprocessing,以下简称dsp),输入/输出器件(input/output,以下简称io)和块存储器件(blockram,以下简称bram)。如图1,lut和ff可以放置在芯片上的clbsite内,dsp,io和bram器件分别可以放置在对应的dspsite,iosite和bramsite内。一般io在fpga芯片上的位置已经给定,故只考虑剩下的器件类型。25.如图1所示,fpga芯片上不同的单元类型在芯片上成列分布。并且,在该实施例中,整个fpga版图被划分成了2×2个时钟区域。对于ff,dsp和bram器件而已,它们都有自己所连的时钟信号。在本实施例中,每个时钟区域内的时钟信号类型数不能超过24个。26.a.建立优化模型,包括wawl线长模型、基于多电场系统的密度模型和二次罚函数时钟惩罚项模型。其中,wawl线长模型用于在布局阶段对线长进行近似计算,基于多电场系统的密度模型和二次罚函数时钟惩罚项模型是本发明提出的模型方法。27.以下分别描述本优化模型中的wawl线长模型,基于多电场系统的密度模型和二次罚函数时钟惩罚项模型,并给出带约束优化问题的形式。28.a1.wawl线长模型。29.本发明具体使用wawl线长模型来作为全局布局阶段对最终布线线长的近似。不妨假设当前所有器件的横纵坐标向量分别为和,所有线网组成集合。对于其中一个线网,该线网wawl线长模型中,其在横坐标和纵坐标方向上的线长分别表示为:该线网wawl线长模型中,其在横坐标和纵坐标方向上的线长分别表示为:其中,为线网在横坐标方向上的线长;为线网在纵坐标方向上的线长;为线网连接的第i个器件的横坐标;为线网连接的第i个器件的纵坐标;为是控制wawl线长模型的平滑程度的参数。线网的wawl线长即为在横纵坐标方向上线长的和:在最终的优化问题中的线长项即为所有线网的wawl线长总和:a2.基于多电场的密度分布模型。对于每种器件类型,分别建立一个电场模型。以下描述如何对单个器件类型建立密度分布模型(电场模型)。30.记表示属于类型的器件集合;另外定义一个参数,表示在除了类型器件可放的单元以外位置的背景电荷密度,而类型器件可放的单元内的背景电荷密度为零。以类型为例,lut类型器件可以放置在clb单元中。在lut类型器件的电场系统中,clb单元所在的位置背景电荷密度为零,clb以外的位置背景电荷密度为。31.另外对于类型的器件,将其视为一个均匀带电二维带电体,其所带电荷均匀分布在其所覆盖的位置内。32.背景电荷密度和所有类型器件所带的电荷这两部分加起来可以得到二维电路版图上每一个点的电荷密度,其中是版图上任意一点的位置坐标。利用麦克斯韦方程组,可以得到器件类型所对应的电场系统中的电荷密度。33.a3.二次罚函数时钟惩罚项模型。34.首先介绍本发明提出的时钟路由分配算法,然后介绍在优化问题中引入二次罚函数时钟惩罚项。35.时钟路由分配算法的目标是根据当前的器件位置,生成器件到可用时钟区域的映射,使得生成的映射不仅要满足时钟路由限制,而且要对线长的扰动最小。时钟路由分配算法的具体步骤如下:1)在当前所有时钟区域中找到时钟信号数量最拥挤的时钟区域,如果该最拥挤的时钟区域满足时钟路由限制(在xilinx的ultrascalevu095芯片上限制每个时钟区域内时钟信号的个数不能超过24个),那么退出算法;2)否则,找出所有出现在该最拥挤的时钟区域的时钟信号,分别计算禁止单个时钟信号出现在该时钟区域的近似代价。对于某时钟信号,该近似代价的计算方式为,对于时钟区域内连接该时钟信号的器件,将其移出该时钟区域的最近欧式距离(也就是离该时钟区域边界的最近欧式距离)即为禁止该器件出现在时钟区域的代价;对时钟区域内连接该时钟信号的所有器件的代价求和即为禁止该时钟信号出现在时钟区域的近似代价。36.3)找到代价最少的禁止单个时钟信号出现在该时钟区域所采用的时钟路由分配映射方式,并把该区域内与该时钟信号相连的所有器件移出,然后回到步骤1)。37.给定时钟路由分配算法生成的器件到可用时钟区域的映射,根据此来生成二次罚函数时钟惩罚项。假设对于器件其可用的时钟区域集合为,并记的边界框的左部、右部、底部和顶部边界坐标分别为分别为:和。本发明将器件的时钟惩罚项定义为:,其中轴方向上的时钟惩罚的定义如下:其中为器件的横坐标,其中为器件的纵坐标。푦轴方向上的时钟惩罚定义类似。优化问题中二次罚函数时钟惩罚项即为所有器件的时钟惩罚项之和:据此,可以将fpga全局布局问题建模成一个带约束非凸优化模型:b.利用增广拉格朗日方法将该带约束非凸优化问题转化为无约束非凸优化问题。转化后的无约束非凸优化问题的模型表示如下:其中,为无约束非凸优化问题的目标函数;为器件类型对应的电场模型的电势能;为器件类型的增广拉格朗日项,包括的一阶项和二阶项,其中为一个引入的参数,用于平衡一阶项和二阶项的大小;为的密度乘子。本发明从拉格朗日松弛方法的角度统一看待问题的时钟路由限制,可路由限制和密度限制,从整个优化过程来看,这三个限制在嵌套的优化迭代中逐渐增强。当优化过程完全收敛时,时钟驱动的全局布局阶段结束。这里引入了时钟乘子和密度乘子,当分别增大这两个乘子时,可以分别增强时钟路由限制和密度限制。38.关于可路由限制,使用面积调整方法策略。该方法的主要思想是,当检测到器件附近存在布线拥塞的情况时,根据器件附近的拥塞情况适当放大实例的面积,布线拥塞越严重的实例,其放大倍数也越大。放大后的面积将体现在电势能的计算上,从而增加可路由性。39.本发明利用一个嵌套优化框架来统一求解,该嵌套优化框架如下:b1.判断是否满足时钟路由约束,如不满足时钟路由约束则更新时钟乘子。40.如果当前不满足时钟路由限制,则利用时钟路由分配算法更新二次时钟罚函数项,加强时钟路由约束限制,并更新无约束优化问题中的时钟乘子。41.b2.判断是否存在路由拥塞问题,如不满足器件可路由性约束则调整器件面积。42.本发明使用使用器件密度和rudy算法来估计路由拥塞程度。如果当前路由拥塞程度超过阈值,则通过调整器件面积,等效地在电场模型中调整器件所带的电荷量,在优化问题中加强对可路由性的限制,从而缓解路由拥塞问题。43.b3.判断器件密度分布是否小于给定的阈值,如果当前器件密度大于阈值,则在优化问题中通过加大密度乘子从而加强对密度分布约束的限制,从而引导器件分散开。44.b4.在上述的b1,b2,b3步骤后,无约束优化问题中时钟乘子,器件面积和密度乘子被确定,使用内思特罗夫动量法对优化问题进行求解,直到优化问题完全收敛,至此即获得了满足时钟路由限制的全局布局结果。45.通过上述步骤,即可以生成一个考虑到时钟路由限制的布局结果,并且该算法兼具较好的运行效率和结果质量,能在相对较短的时间内生成较好的考虑到时钟路由限制的布局结果。46.需要注意的是,公布实施例的目的在于进一步帮助理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附权利要求的范围内,各种替换和修改都是可能的,包括但不限于优化参数的调整,具体的每个时钟区域的时钟信号类型数等。因此,本发明不应局限于实施例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。当前第1页12当前第1页12

技术领域:

:1.本发明属于电子电气设计自动化(electronicdesignautomation,以下简称eda)

技术领域:

:,涉及芯片集成电路物理设计中针对现场可编程门阵列(fieldprogrammablegatearray,以下简称fpga)的全局布局技术,具体涉及一种基于多电场模型系统的时钟驱动fpga全局布局方法。

背景技术:

::2.fpga是一种在硅片上进行预先设计的具有可编程特性的半定制集成电路芯片。在fpga芯片制造过程中,制造厂商会预先在硅片上设计出可编程门逻辑器件;在客户使用过程时,设计人员可以通过硬件描述语言(verilog或者vhdl)描述定制化的逻辑电路,然后利用逻辑综合,布局和布线等eda软件,将定制化的逻辑电路快速刻录到fpga上进行测试。fpga能够按照设计人员的需求快速配置为指定的电路结构,让客户能够在芯片开发前期不必依赖流片周期长,一次性工程费用大的专用集成电路(applicationspecificintegratedcircuit,以下简称asic)芯片,因此fpga被广泛应用在原型验证,工业控制,通信,汽车电子,数据中心和航空航天等领域。3.fpga全局布局技术是指,给定电路网表和目标fpga芯片的布局限制,计算器件在芯片上的位置,使得通过接下来的合法化,详细布局和布线阶段后得到的布线的线长最短。由于fpga芯片的异构性质,相比于asic芯片,针对fpga芯片的全局布局算法难度更高。fpga的异构性质体现在,制造厂商在硅片上预先设计的多种可编程逻辑器件在fpga芯片上成列分布,且器件的数量、位置分布不均;并且由于局部可编辑逻辑器件的信号线共用问题,在局部区域部分逻辑器件的不能任意组合,这些都大大增加了针对fpga全局布局算法的难度。4.而随着现代fpga集成度的提高和性能的多元化,fpga芯片对布局的要求越来越复杂,其中包括在布局阶段对时钟信号路由的考虑。为了减少后期进行时序分析中的时钟偏移(clockskew),在现代高性能fpga芯片的制造过程中,往往为了时钟信号设计了专门的时钟路由通道(clockroutingtrack),以提高电路的运行频率。但是,时钟路由通道的分布也对布局阶段器件的分布提出了限制。以赛灵思(简称xilinx)设计的ultrascalevu095芯片为例,其把整个fpga芯片版图划分为5×8个时钟区域(clockregion),通过每个时钟区域的时钟信号个数最多为24。这个要求在同一个时钟区域内的所有器件的时钟信号种类个数不能超过24个,这对fpga全局布局算法提出了更高的要求。5.现有的传统fpga全局布局算法存在以下的不足之处:(一)现有的fpga布局工具在大规模fpga布局问题上效果不佳。现有的fpga布局工具主要使用基于二次规划的全局布局算法,然而随着芯片规模和芯片复杂度的不断增加,在大规模的fgpa布局问题上基于二次规划的fpga全局布局算法不能取得很好的布局质量。6.(二)现有的fpga全局布局算法较少在全局布局阶段考虑对时钟信号路由的限制。由于在布局阶段缺乏对时钟信号路由的限制,在后期的合法化阶段需要对部分违反时钟信号路由的器件的位置再进行调整,这会影响整个布局结果的质量。7.综上所述,现有的传统fpga全局布局算法在大规模fpga布局问题上难以取得很好的布局结果,并且由于在全局布局阶段较少考虑对时钟信号路由的限制,在布局后期的合法化阶段中对违反时钟路由信号的器件的调整会影响布局质量。技术实现要素:8.为了克服上述现有技术的不足,本发明提出了一种基于多电场模型的时钟驱动fpga芯片的全局布局算法。该算法针对fpga布局的异构性质,对多种不同的器件类型分别建立了电场模型,用于对器件的密度分布进行建模;并且通过时钟路由分配算法和二次罚函数的方法,在全局布局阶段以平滑化的方式引入了时钟路由的限制,使得该算法可以在全局布局阶段产生满足时钟路由限制的布局结果,提升fpga芯片全局布局的质量和效果。9.在本发明中,将fgpa布局问题通过增广拉格朗日方法转化成一个非凸优化问题,并使用内思特罗夫动量法(nesterovmomentummethod)进行求解。并且,本发明提出的算法采用适合gpu进行并行运算的算法结构,能够充分利用gpu进行加速计算,从而在全局布局阶段高效地获得较好的满足时钟路由限制的布局结果。10.本发明的技术方案是:一种基于多电场模型的时钟驱动fpga芯片的全局布局方法,分别对多种不同的器件类型建立了电场模型,来对多种器件的密度分布进行高效建模,并通过时钟路由分配算法和二次罚函数的方法在全局布局的优化问题中以平滑化的方式引入时钟路由的限制,使得可以在全局布局阶段生成有利于接下来合法化阶段的满足时钟路由限制的布局结果。11.在本发明中,输入包括逻辑综合后得到的电路网表和fpga芯片的布局限制,其中的布局限制包括时钟路由限制。本发明包括如下步骤:a.建立优化模型。12.利用可微的加权平均线长模型(weightedaveragewirelength,以下简称wawl)模型来作为布线线长的近似;针对多种不同的器件类型,分别建立了不同器件类型的电场模型,用于对不同器件类型的密度分布进行建模;同时,利用时钟路由分配算法,在优化目标中加入光滑化的二次时钟罚函数项,从而把时钟驱动的fpga布局问题建模成一个带约束非凸优化问题。13.b.利用增广拉格朗日方法(augmentedlagrangianmethod)将该带约束非凸优化问题转化为无约束非凸优化问题。对于原优化问题的三个约束,即时钟路由约束,器件可路由性约束和器件密度分布约束,通过利用一个嵌套优化框架来统一求解,该嵌套优化框架如下:b1.判断是否满足时钟路由约束,并更新时钟乘子。14.b2.判断是否存在路由拥塞问题、是否满足器件可路由性约束,并调整器件面积。15.b3.判断器件密度分布是否足够小、是否满足器件密度分布约束,并调整密度乘子。16.b4.在上述的b1,b2,b3步骤后,无约束优化问题中时钟乘子,器件面积和密度乘子被确定,使用内思特罗夫动量法对优化问题进行求解,直到优化问题完全收敛。17.通过上述步骤,即可以生成一个考虑到时钟路由限制的布局结果,并且该算法兼具较好的运行效率和结果质量,能在相对较短的时间内生成较好的考虑到时钟路由限制的布局结果。18.与现有技术相比,本发明的有益效果在于:本发明提供了一种高效的基于多电场系统的时钟驱动fpga全局布局算法,分别对多种不同的器件类型建立了电场模型来对器件的密度分布进行高效建模,并通过时钟路由分配算法和二次罚函数的方法在全局布局的优化问题中以平滑化的方式引入时钟路由的限制,将fpga布局问题转化成带约束非凸优化问题,并通过高效增广拉格朗日方法进行求解,从而获得质量较好的考虑到时钟路由限制的fpga布局结果。19.同时,该算法的计算模型多为向量化操作,具有可充分利用gpu进行并行加速的计算结构,因此具有良好的计算效率和布局结果质量。附图说明20.图1为本发明具体实施例中采用的fpga芯片的片上资源分布的简化示意图;其中,clb(configurablelogicblock)site为可编程逻辑单元,dsp(digitalsignalprocessing)site为数字信号处理单元,io(input/output)site为输入/输出单元,bram(blockram)site为块存储单元。21.图2为本发明具体实施采用的本发明提出了一种基于多电场模型的时钟驱动fpga全局布局算法的流程框图。具体实施方式22.下面结合附图,通过实施例进一步描述本发明,但不以任何方式限制本发明的范围。23.本发明提供的高效的基于多电场系统的时钟驱动fpga全局布局算法,输入包括电路网表和fpga芯片布局限制,输出考虑到时钟路由限制的fpga全局布局结果。24.以下先提供本发明输入的描述。在本发明中,电路网表用表示,其中表示器件集合,表示器件之间的超边集合。注意在fpga布局问题中,一个超边可以同时连接多个器件。各器件有自己的类型,在该实施例中,器件可能的类型为查找表(look-uptable,以下简称lut),触发器(flipflop,以下简称ff),数字信号处理器件dsp(digitalsignalprocessing,以下简称dsp),输入/输出器件(input/output,以下简称io)和块存储器件(blockram,以下简称bram)。如图1,lut和ff可以放置在芯片上的clbsite内,dsp,io和bram器件分别可以放置在对应的dspsite,iosite和bramsite内。一般io在fpga芯片上的位置已经给定,故只考虑剩下的器件类型。25.如图1所示,fpga芯片上不同的单元类型在芯片上成列分布。并且,在该实施例中,整个fpga版图被划分成了2×2个时钟区域。对于ff,dsp和bram器件而已,它们都有自己所连的时钟信号。在本实施例中,每个时钟区域内的时钟信号类型数不能超过24个。26.a.建立优化模型,包括wawl线长模型、基于多电场系统的密度模型和二次罚函数时钟惩罚项模型。其中,wawl线长模型用于在布局阶段对线长进行近似计算,基于多电场系统的密度模型和二次罚函数时钟惩罚项模型是本发明提出的模型方法。27.以下分别描述本优化模型中的wawl线长模型,基于多电场系统的密度模型和二次罚函数时钟惩罚项模型,并给出带约束优化问题的形式。28.a1.wawl线长模型。29.本发明具体使用wawl线长模型来作为全局布局阶段对最终布线线长的近似。不妨假设当前所有器件的横纵坐标向量分别为和,所有线网组成集合。对于其中一个线网,该线网wawl线长模型中,其在横坐标和纵坐标方向上的线长分别表示为:该线网wawl线长模型中,其在横坐标和纵坐标方向上的线长分别表示为:其中,为线网在横坐标方向上的线长;为线网在纵坐标方向上的线长;为线网连接的第i个器件的横坐标;为线网连接的第i个器件的纵坐标;为是控制wawl线长模型的平滑程度的参数。线网的wawl线长即为在横纵坐标方向上线长的和:在最终的优化问题中的线长项即为所有线网的wawl线长总和:a2.基于多电场的密度分布模型。对于每种器件类型,分别建立一个电场模型。以下描述如何对单个器件类型建立密度分布模型(电场模型)。30.记表示属于类型的器件集合;另外定义一个参数,表示在除了类型器件可放的单元以外位置的背景电荷密度,而类型器件可放的单元内的背景电荷密度为零。以类型为例,lut类型器件可以放置在clb单元中。在lut类型器件的电场系统中,clb单元所在的位置背景电荷密度为零,clb以外的位置背景电荷密度为。31.另外对于类型的器件,将其视为一个均匀带电二维带电体,其所带电荷均匀分布在其所覆盖的位置内。32.背景电荷密度和所有类型器件所带的电荷这两部分加起来可以得到二维电路版图上每一个点的电荷密度,其中是版图上任意一点的位置坐标。利用麦克斯韦方程组,可以得到器件类型所对应的电场系统中的电荷密度。33.a3.二次罚函数时钟惩罚项模型。34.首先介绍本发明提出的时钟路由分配算法,然后介绍在优化问题中引入二次罚函数时钟惩罚项。35.时钟路由分配算法的目标是根据当前的器件位置,生成器件到可用时钟区域的映射,使得生成的映射不仅要满足时钟路由限制,而且要对线长的扰动最小。时钟路由分配算法的具体步骤如下:1)在当前所有时钟区域中找到时钟信号数量最拥挤的时钟区域,如果该最拥挤的时钟区域满足时钟路由限制(在xilinx的ultrascalevu095芯片上限制每个时钟区域内时钟信号的个数不能超过24个),那么退出算法;2)否则,找出所有出现在该最拥挤的时钟区域的时钟信号,分别计算禁止单个时钟信号出现在该时钟区域的近似代价。对于某时钟信号,该近似代价的计算方式为,对于时钟区域内连接该时钟信号的器件,将其移出该时钟区域的最近欧式距离(也就是离该时钟区域边界的最近欧式距离)即为禁止该器件出现在时钟区域的代价;对时钟区域内连接该时钟信号的所有器件的代价求和即为禁止该时钟信号出现在时钟区域的近似代价。36.3)找到代价最少的禁止单个时钟信号出现在该时钟区域所采用的时钟路由分配映射方式,并把该区域内与该时钟信号相连的所有器件移出,然后回到步骤1)。37.给定时钟路由分配算法生成的器件到可用时钟区域的映射,根据此来生成二次罚函数时钟惩罚项。假设对于器件其可用的时钟区域集合为,并记的边界框的左部、右部、底部和顶部边界坐标分别为分别为:和。本发明将器件的时钟惩罚项定义为:,其中轴方向上的时钟惩罚的定义如下:其中为器件的横坐标,其中为器件的纵坐标。푦轴方向上的时钟惩罚定义类似。优化问题中二次罚函数时钟惩罚项即为所有器件的时钟惩罚项之和:据此,可以将fpga全局布局问题建模成一个带约束非凸优化模型:b.利用增广拉格朗日方法将该带约束非凸优化问题转化为无约束非凸优化问题。转化后的无约束非凸优化问题的模型表示如下:其中,为无约束非凸优化问题的目标函数;为器件类型对应的电场模型的电势能;为器件类型的增广拉格朗日项,包括的一阶项和二阶项,其中为一个引入的参数,用于平衡一阶项和二阶项的大小;为的密度乘子。本发明从拉格朗日松弛方法的角度统一看待问题的时钟路由限制,可路由限制和密度限制,从整个优化过程来看,这三个限制在嵌套的优化迭代中逐渐增强。当优化过程完全收敛时,时钟驱动的全局布局阶段结束。这里引入了时钟乘子和密度乘子,当分别增大这两个乘子时,可以分别增强时钟路由限制和密度限制。38.关于可路由限制,使用面积调整方法策略。该方法的主要思想是,当检测到器件附近存在布线拥塞的情况时,根据器件附近的拥塞情况适当放大实例的面积,布线拥塞越严重的实例,其放大倍数也越大。放大后的面积将体现在电势能的计算上,从而增加可路由性。39.本发明利用一个嵌套优化框架来统一求解,该嵌套优化框架如下:b1.判断是否满足时钟路由约束,如不满足时钟路由约束则更新时钟乘子。40.如果当前不满足时钟路由限制,则利用时钟路由分配算法更新二次时钟罚函数项,加强时钟路由约束限制,并更新无约束优化问题中的时钟乘子。41.b2.判断是否存在路由拥塞问题,如不满足器件可路由性约束则调整器件面积。42.本发明使用使用器件密度和rudy算法来估计路由拥塞程度。如果当前路由拥塞程度超过阈值,则通过调整器件面积,等效地在电场模型中调整器件所带的电荷量,在优化问题中加强对可路由性的限制,从而缓解路由拥塞问题。43.b3.判断器件密度分布是否小于给定的阈值,如果当前器件密度大于阈值,则在优化问题中通过加大密度乘子从而加强对密度分布约束的限制,从而引导器件分散开。44.b4.在上述的b1,b2,b3步骤后,无约束优化问题中时钟乘子,器件面积和密度乘子被确定,使用内思特罗夫动量法对优化问题进行求解,直到优化问题完全收敛,至此即获得了满足时钟路由限制的全局布局结果。45.通过上述步骤,即可以生成一个考虑到时钟路由限制的布局结果,并且该算法兼具较好的运行效率和结果质量,能在相对较短的时间内生成较好的考虑到时钟路由限制的布局结果。46.需要注意的是,公布实施例的目的在于进一步帮助理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附权利要求的范围内,各种替换和修改都是可能的,包括但不限于优化参数的调整,具体的每个时钟区域的时钟信号类型数等。因此,本发明不应局限于实施例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。当前第1页12当前第1页12

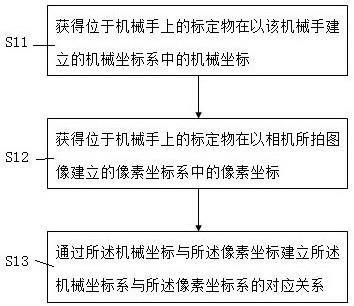

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。