一种数据存储方法、ssd控制器、ssd及电子设备

技术领域:

:1.本技术实施例涉及存储器

技术领域:

:,具体涉及一种数据存储方法、ssd控制器、ssd及电子设备。

背景技术:

::2.ssd(solidstatedisk,固态硬盘)是使用固态电子存储芯片阵列制成的硬盘,其可以采用闪存颗粒作为存储介质。相比于传统的机械硬盘,ssd具有读写速度快、功耗低、噪音低、轻便等优点,因此ssd在存储领域得到了广泛的应用。3.在multi-stream(多流)技术下,ssd可通过multi-stream协议,将主机端传输的数据流在闪存颗粒中进行分区存放,以实现ssd的盘内区域隔离。然而,出于ssd掉电时的数据存储安全性、以及闪存颗粒可能多次page(页)program(编程)的考虑,ssd可支持的多流数量会存在一定的限制,因此如何优化ssd的数据存储方案,以提升ssd支持的多流数量,从而提升ssd的数据存储性能,成为了本领域技术人员亟需解决的技术问题。技术实现要素:4.有鉴于此,本技术实施例提供一种数据存储方法、ssd控制器、ssd及电子设备,以提升ssd支持的多流数量,从而提升ssd的数据存储性能。5.为实现上述目的,本技术实施例提供如下技术方案。6.第一方面,本技术实施例提供一种数据存储方法,包括:获取主机传输的数据流;将所述数据流缓存到ssd的非易失性缓存;其中,所述非易失性缓存为ssd的闪存颗粒的前置缓存,并且所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间;若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到所述闪存颗粒。7.第二方面,本技术实施例提供一种数据存储方法,包括:检测ssd的闪存颗粒中数据的读取频率;若数据的读取频率高于预定频率,将所述数据搬移到所述闪存颗粒的前置缓存;所述前置缓存包括非易失性缓存,所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间。8.第三方面,本技术实施例提供一种ssd控制器,所述ssd控制器被配置为执行如上述第一方面所述的数据存储方法,或者,如上述第二方面所述的数据存储方法。9.第四方面,本技术实施例提供一种ssd,包括:如上述所述的ssd控制器、非易失性缓存、以及闪存颗粒;其中,所述非易失性缓存作为所述闪存颗粒的前置缓存,用于缓存主机传输至所述ssd的数据流;所述非易失性缓存的数据读写延时介于所述ssd的易失性缓存和闪存颗粒之间。10.第五方面,本技术实施例提供一种电子设备,包括主机以及如上述所述的ssd,所述主机与所述ssd之间通过多流协议传输数据。11.本技术实施例在ssd的闪存颗粒使用单位bit数较多的闪存单元,并且闪存颗粒需要进行多次pageprogram时,可在ssd中设置非易失性缓存作为闪存颗粒的前置缓存,并且该非易失性缓存的数据读写延时介于ssd中的易失性缓存和非易失性的闪存颗粒之间。从而,在ssd获取到主机端传输的数据流时,本技术实施例可将所述数据流缓存到ssd中的非易失性缓存中,并且非易失性缓存中的数据流达到预设的写入条件时,可写入到闪存颗粒中,以实现多流场景下,数据流在ssd中的分区隔离存储。由于本技术实施例使用非易失性缓存作为闪存颗粒的前置缓存,来缓存主机侧传输的数据流,因此即使ssd发生掉电情况,本技术实施例也可保障非易失性缓存中的数据不出现丢失,而不必在掉电时立刻将非易失性缓存中的数据写入到闪存颗粒中;从而,本技术实施例可规避ssd中的电容对于前置缓存所缓存的数据量限制,避免主机侧的数据流数量所受的限制,从而提升主机侧在多流场景下可传输给ssd的数据流数量,提升ssd的数据存储性能。附图说明12.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。13.图1a为ssd的结构示例图。14.图1b为闪存颗粒的类型示例图。15.图2为应用ssd的电子设备的示例图。16.图3为本技术实施例提供的ssd的另一示例图。17.图4a为本技术实施例提供的数据存储方法的流程图。18.图4b为本技术实施例提供的数据存储方法的另一流程图。19.图5a为本技术实施例提供的ssd的再一示例图。20.图5b为本技术实施例提供的数据存储方法的再一流程图。21.图5c为本技术实施例提供的数据存储方案的实现示例图。22.图6为本技术实施例提供的ssd的又一示例图。23.图7a为本技术实施例提供的数据存储方法的又一流程图。24.图7b为本技术实施例搬移数据到前置缓存的方法流程图。25.图8为本技术实施例提供的ssd的又另一示例图。具体实施方式26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。27.图1a示例性的示出了ssd的结构示例图,如图1a所示,ssd可以包括:ssd控制器110和闪存颗粒120。ssd控制器110为ssd中的主控芯片,主要实现ssd中的数据存储控制和管理,例如ssd控制器可管理用户(一般为主机侧)传输至ssd进行读写的数据流、管理逻辑地址和物理地址的映射、管理闪存颗粒的特性等。闪存颗粒120为ssd中存储数据的存储介质,在一些实施例中,闪存颗粒可以是非易失性的存储介质。例如,ssd中可以使用nand闪存颗粒,其中,nand闪存是一种非易失性存储技术,即断电后仍能保存数据。28.闪存颗粒(例如nand闪存颗粒)可以由多个以bit(比特)为单位的闪存单元构成,一个闪存单元存储数据的单位bit数可以是一位或者多位。基于闪存颗粒中的每个闪存单元存储数据的单位bit数,闪存颗粒可以分为多种不同的类型。也就是说,基于闪存颗粒中电子单元的密度大小,闪存颗粒可以具有不同的类型。图1b示例性的示出了闪存颗粒的类型示例图,可进行参照。如图1b所示,闪存颗粒可以分为slc(singlelevelcell,单层单元)、mlc(multilevelcell,多层单元)、tlc(triplelevelcell,三层单元)、qlc(quadlevelcell,四层单元)等多种类型;其中,基于slc的闪存颗粒以1bit为单位存储数据,基于mlc的闪存颗粒以2bit为单位存储数据,基于tlc的闪存颗粒以3bit为单位存储数据,基于qlc的闪存颗粒以4bit为单位存储数据。需要说明的是,闪存单元的单位bit数越多,则闪存颗粒每bit的数据存储成本越低,但是理论上的数据读写速度越慢;例如qlc和tlc相比于slc和mlc具有更低的数据存储成本,但是数据读写速度则较慢。因此qlc等单位bit数较多的闪存单元比较适用于数据存储量较大且需求成本较低的数据存储场景,例如数据仓库等企业级的数据存储场景。29.可以看出,随着闪存单元存储数据的单位bit数增多(例如闪存颗粒基于qlc等单位bit数较多的闪存单元存储数据),ssd能够降低数据的单bit存储成本,但是在实际应用过程中,闪存单元的单位bit数增多,将带来闪存颗粒的数据稳定性变差、读写page的时间变长,写入数据需要多次pageprogram(编程)等挑战,这导致ssd需要为闪存颗粒设置大容量的前置缓存,以满足闪存颗粒多次pageprogram的需求。在此情况下,如果该前置缓存选用大容量的易失性缓存(例如ddr缓存),则出于ssd掉电时的数据存储安全性考虑,ssd需要为该前置缓存设置大容量的电容,以在ssd掉电时,通过该大容量的电容将前置缓存中的数据写入到闪存颗粒。而在multi-stream场景下,为保障前置缓存中缓存的数据流,能够在掉电时写入到闪存颗粒中,前置缓存需要基于电容可支持的写入数据量来缓存数据,这导致ssd需要基于电容可支持的写入数据量来限制多流数量,致使ssd在应用multi-stream技术时,存在多流数量限制。30.为便于说明上述问题,以基于qlc的闪存颗粒为例,图2示例性的示出了应用ssd的电子设备的示例图,如图2所示,该电子设备可以包括:主机210、接口220、ssd230。其中,主机210可以例如与ssd230耦合的计算机,主机中可设置处理器等用于数据处理、计算的处理核心。接口220可以是主机210与ssd230耦合接口,并支持multi-stream协议。ssd230为主机210耦合的固态硬盘,其通过接口220与主机210交换数据,在本示例中,ssd可以包括ssd控制器110、基于qlc的闪存颗粒120、易失性缓存240和电容250。31.在主机与ssd传输数据的过程中,主机与ssd可通过multi-stream协议传输数据,并且ssd可通过multi-stream技术,将主机端传输的数据进行分区存放。具体来说,在multi-stream技术下,主机端可传输给ssd多个数据流,并且数据流会携带streamid(数据流标识);ssd可根据主机端提供的streamid,将具有相同streamid的数据(相同streamid的数据一般具有相同或相似的数据特性)写入到闪存颗粒的相似物理空间中,以实现ssd的盘内区域隔离。32.结合图2所示,在multi-stream场景下,易失性缓存240作为闪存颗粒120的前置缓存,易失性缓存240可以缓存主机210传输给ssd的多个数据流,并且该多个数据流可通过易失性缓存240写入到闪存颗粒120中,实现不同streamid的数据流在闪存颗粒中的分区存放。在一个示例中,易失性缓存240可以为ddr(doubledatarate,双倍数据速率)缓存,ddr缓存可以dram(dynamicrandomaccessmemory,动态随机存取存储器)为介质。33.然而,由于易失性缓存240的易失性特点(即掉电时,易失性缓存240中的数据将会丢失),为保障ssd的数据存储安全,易失性缓存240中的数据需要在掉电时写入到闪存颗粒中,此时,ssd控制器110需要驱动电容250来控制易失性缓存240在掉电时,将数据写入到闪存颗粒。在此情况下,由于基于qlc的闪存颗粒需要通过多次的program进行写数据,在多流并发下,为避免易失性缓存240中缓存的数据过多,难以在掉电情况下完全写入到闪存颗粒中而出现数据丢失,因此需要在闪存颗粒每次program的间隔内,限制易失性缓存240所缓存的数据量。例如,在闪存颗粒每次program的间隔内,需要限制易失性缓存240所缓存的数据量不超过电容250可支持的写入数据量,从而避免易失性缓存240中超出的数据在掉电时难以写入到闪存颗粒中,出现数据丢失的不安全情况。34.需要说明的是,闪存颗粒中的一个block通常包含多个page,因此在multi-stream技术下,闪存颗粒在块中读写数据时,涉及到对于page的读写操作。此时,如果闪存颗粒使用qlc等单位bit数较多的闪存单元,则闪存颗粒需要通过多次的program进行写数据,同时闪存颗粒需要较长的时间进行page读写、闪存颗粒的tprog和tr的时间均较长(tprog是指数据编程写入page的时间,tr是指数据从page读取的时间)。35.通过上述描述可以看出,在ssd使用易失性缓存作为闪存颗粒的前置缓存时,如果闪存颗粒使用qlc等单位bit数较多的闪存单元,则出于掉电时的数据存储安全性、以及闪存颗粒可能多次pageprogram的考虑,需要基于电容能支持的写入数据量,来限制易失性缓存所缓存的数据量,这导致主机侧并发传输的数据流数量需要进行限制,以避免较多的数据流同时缓存在易失性缓存;而这进一步导致主机侧难以并发传输数量较多的数据流,从而对于multi-stream技术的应用造成限制,降低了ssd的数据存储性能。36.解决上述问题的一个思路是,由于主机侧可传输的数据流数量与缓存所能保存的数据量呈正相关,因此可在ssd中设置更大容量的电容,以提升电容所能支持的易失性缓存的写入数据量,然而ssd的电路板空间有限,更大容量的电容设置将挤占ssd的板上空间,并且提升了ssd的设计难度。37.基于此,本技术实施例提供改进型的技术思路,在ssd中设置大容量和单bit数据存储成本较低的非易失性缓存,通过非易失性缓存来缓存multi-stream场景下的数据流,并且基于非易失性缓存的非易失特性,规避ssd在掉电时数据可能出现丢失的不安全问题。38.基于上述思路,本技术实施例考虑在ssd中引入非易失性缓存,该非易失性缓存的数据读写延时介于易失性缓存和闪存颗粒之间(闪存颗粒可以为非易失性的存储介质);并且将该非易失性缓存作为闪存颗粒的前置缓存,通过改进多流技术下的数据存储方案,使得闪存颗粒在使用qlc等单位bit数较多的闪存单元时,本技术实施例能够通过该非易失性缓存的非易失特性,将闪存颗粒的tprog和tr的时间较长、较长的page读写时间的缺点所带来的约束进行规避,从而在ssd掉电时,仍能通过该非易失性缓存保存数据,而不必将数据立刻写入到闪存颗粒中,进而本技术实施例可规避电容所能支持的写入数据量对于ssd缓存数据的限制,提升multi-stream的多流数量,提升ssd的数据存储性能。39.作为可选实现,图3示例性的示出了本技术实施例提供的ssd的另一示例图。参照图3所示,在本技术实施例中,ssd可以包括:ssd控制器110、闪存颗粒120、非易失性缓存310;闪存颗粒120可以使用单位bit数较多的闪存单元,比如闪存颗粒120使用的闪存单元存储数据的单位bit数为4(例如基于qlc的闪存颗粒),或者大于4;在闪存颗粒使用单位bit数较多的闪存单元时,闪存颗粒需要通过多次的pageprogram进行写数据。40.非易失性缓存310为ssd中设置的非易失性的内存缓存,并且非易失性缓存310的数据读写延时介于易失性缓存和闪存颗粒120之间。41.在一个示例中,非易失性缓存310可以为scm(storageclassmemory,储存级存储器),例如pcm(phase-changememory,相变存储器)、3d-xpoint等;scm具有容量大和单bit成本比dram等易失性缓存低3到5倍的特点。42.在本技术实施例中,非易失性缓存可作为闪存颗粒的前置缓存,用于对主机侧传输的数据流进行缓存,并且非易失性缓存中的数据流可写入到闪存颗粒中。在一些实施例中,主机端在传输多个数据流时,数据流可通过非易失性缓存作为桥梁,写入ssd的闪存颗粒(简称为写数据过程);并且闪存颗粒中的数据,可通过非易失性缓存作为桥梁进行读取(简称为读数据过程)。下面将分别从写数据和读数据的角度,对本技术实施例提供的数据存储方法进行介绍。43.作为可选实现,图4a示例性的示出了本技术实施例提供的数据存储方法的可选流程图。该方法流程可由ssd执行实现,例如由ssd中的ssd控制器执行实现。需要说明的是,ssd控制器内部可设置硬件加速模块和片内处理器,本技术实施例可结合ssd控制器内部的硬件逻辑以及片内处理器的程序逻辑,执行实现该方法流程。参照图4a,该方法流程可以包括如下步骤。44.在步骤s410中,获取主机传输的数据流。45.在步骤s411中,将所述数据流缓存到ssd的非易失性缓存。46.在步骤s412中,若所述非易失性缓存中的缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。47.在一些实施例中,数据流从非易失性缓存写入到闪存颗粒的写入条件例如:任一数据流在非易失性缓存中缓存的数据量达到闪存颗粒的最小编程单元的数据量要求,则可将该数据流写入到闪存颗粒中;或者,在发生掉电时,如果非易失性缓存中缓存的数据流的数据量未达到最小编程单元的数据量要求,则补足数据流的数据量,从而将补足数据量的数据流写入到闪存颗粒中。48.在一个示例中,假设闪存颗粒的最小编程单元要求的数据量为96kb(最小编程单元的具体数据量要求可根据闪存颗粒的具体情况设置,本技术实施例并不设限),主机侧以4kb为单位持续性的传输数据流,则在非易失性缓存缓存主机侧传输的数据流后,如果任一个数据流的数据量达到96kb,则该数据流可从非易失性缓存写入到闪存颗粒中。在进一步的示例中,如果任一个数据流在非易失性缓存中所缓存的数据量未达到96kb时,发生掉电情况,则非易失性缓存可将该数据流的数据量补足到96kb(例如通过空白值或者其他设定数值进行数据量的补充),并将补足到96kb的数据流从非易失性缓存写入到闪存颗粒中。49.在一些实施例中,本技术实施例在将数据流从非易失性缓存写入到闪存颗粒时,可根据数据流携带的数据流标识,将不同数据流标识的数据流写入到闪存颗粒的不同区域,以实现不同数据流标识的数据在ssd中的分区隔离存储。50.本技术实施例在ssd的闪存颗粒使用单位bit数较多的闪存单元,并且闪存颗粒需要进行多次pageprogram时,可在ssd中设置非易失性缓存作为闪存颗粒的前置缓存,并且该非易失性缓存的数据读写延时介于ssd中的易失性缓存和非易失性的闪存颗粒之间。从而,在ssd获取到主机端传输的数据流时,本技术实施例可将所述数据流缓存到ssd中的非易失性缓存中,并且非易失性缓存中的数据流达到预设的写入条件时,可写入到闪存颗粒中,以实现多流场景下,数据流在ssd中的分区隔离存储。由于本技术实施例使用非易失性缓存作为闪存颗粒的前置缓存,来缓存主机侧传输的数据流,因此即使ssd发生掉电情况,本技术实施例也可保障非易失性缓存中的数据不出现丢失,而不必在掉电时立刻将非易失性缓存中的数据写入到闪存颗粒中;从而,本技术实施例可规避ssd中的电容对于前置缓存所缓存的数据量限制,进而避免主机侧的数据流数量受到限制,提升主机侧在多流场景下可传输给ssd的数据流数量,提升ssd的数据存储性能。51.在本技术实施例的一些实施例中,ssd设置的非易失性缓存可缓存主机侧传输的所有数据流,也可仅设置非易失性缓存对主机侧传输的特定特性的数据流进行缓存。作为可选实现,本技术实施例可设置非易失性缓作为闪存颗粒的前置缓存,并且缓存多流技术下第一特性的数据流(例如读写性能要求低的数据流、冷数据、数据块较小的数据流等)。也就是说,主机端在传输多个数据流时,第一特性的数据流可通过非易失性缓存作为桥梁,写入ssd的闪存颗粒;并且闪存颗粒中第一特性的数据,可通过非易失性缓存作为桥梁进行读取。52.作为可实现,图4b示例性的示出了本技术实施例提供的数据存储方法的另一可选流程图。该方法流程可由ssd控制器执行实现,参照图4b,该方法流程可以包括如下步骤。53.在步骤s420中,获取主机传输的数据流。54.在步骤s421中,确定所述数据流的数据特性。55.在本技术实施例中,主机可通过与ssd的接口协议(例如multi-stream协议),将数据流传输到ssd,从而ssd中的ssd控制器可获取主机传输的多个数据流,并确定每个数据流的数据特性。56.在一些实施例中,在multi-stream技术下,基于ssd在多流的接口协议特性,主机可根据数据流的读写特征(例如,数据流的冷热特征、读写性能要求、数据块大小等),为传输给ssd的数据流标记streamid,从而主机可将携带streamid的数据流传输给ssd。此时,ssd控制器可获取到主机端传输的携带streamid的多个数据流,并基于每个数据流携带的streamid,确定每个数据流的数据特性。57.作为可选实现,本技术实施例可将数据流分为第一特性的数据流和第二特性的数据流,例如,第一特性的数据流包括读写性能要求低的数据流、冷数据、数据块较小的数据流,第二特性的数据流包括读写性能要求高的数据流、热数据、数据块较大的数据流等。也就是说,在可能的示例中,第一特性的数据流的读写性能要求低于第二特性的数据流、或者第一特性的数据流的数据块小于第二特性的数据流、或者第一特性的数据流为冷数据并且第二特性的数据流为热数据。冷数据可以理解为是访问频率较低的数据,比如企业备份数据、操作日志数据等,热数据可以理解为是频繁访问的数据,比如metadata(元数据)等。58.在本技术实施例中,主机端传输的第一特性的数据流可由ssd中设置的非易失性缓存(例如scm)进行前置缓存。作为可选实现,针对第一特性的数据流,本技术实施例可设置第一特性的数据对应的streamid范围,从而ssd控制器可通过主机端传输的数据流携带的streamid,确定主机端传输的数据流的特性是否为第一特性,比如,主机端传输的数据流携带的streamid在第一特性的数据流对应的streamid范围内,则可确定主机端传输的数据流为第一特性的数据流,可由ssd中的非易失性缓存进行前置缓存。59.在步骤s422中,若所述数据特性为第一特性,将所述数据流缓存到ssd中的非易失性缓存。60.ssd控制器在确定主机传输的数据流的数据特性为第一特性时(例如数据流携带的streamid在第一特性的数据流对应的streamid范围内),则ssd控制器可确定由非易失性缓存进行数据流的缓存,从而ssd控制器可将数据流缓存到非易失性缓存中。在一个示例中,主机端传输的读写性能要求较低的数据流、冷数据、数据块较小的数据流可缓存到非易失性缓存中,例如,ssd控制器在基于数据流携带的streamid,确定数据流为读写性能要求较低的数据流、冷数据、数据块较小的数据流中的任一项时,可基于数据流携带的streamid,将数据流缓存到非易失性缓存。61.在步骤s423中,若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。62.在进一步的一些实施例中,基于非易失性缓存作为闪存颗粒的前置缓存,因此非易失性缓存所缓存的数据达到一定条件时,需要写入到前置缓存中。作为可选实现,本技术实施例可设置数据流从缓存(包括非易失性缓存和易失性缓存)写入到闪存颗粒的写入条件,当非易失性缓存中缓存的数据流达到该写入条件时,本技术实施例可将数据流从非易失性缓存写入到闪存颗粒。具体的写入条件内容可参照前文相应部分的描述。63.针对第一特性的数据流,本技术实施例可将非易失性缓存作为闪存颗粒和主机之间的中间数据缓存,从而利用非易失性缓存的数据读写延时高于易失性缓存、低于闪存颗粒,并且非易失性缓存的大容量、单bit数据存储成本较低以及非易失性的特性,避免ssd在掉电时需要通过电容将前置缓存中的数据立刻写入到闪存颗粒的情况,进而将闪存颗粒多次的pageprogram所带来的约束进行规避,提升了多流场景下主机侧可传输的数据流数量,减少了主机侧的数据传输约束,为提升ssd更大的存储性能提供了可能。进一步的,通过非易失性缓存对第一特性的数据进行缓存和管理,可使得ssd能够在多流技术下满足主机端读写数据的多流特性要求。64.在进一步的一些实施例中,本技术实施例也可在ssd中设置易失性缓存,该易失性缓存可用于在非多流场景下,作为闪存颗粒的前置缓存来缓存数据;该易失性缓存也可在多流场景下,作为闪存颗粒的前置缓存,用于对主机侧传输的第二特性的数据流进行缓存(例如缓存读写性能要求高的数据流、热数据、数据块较大的数据流等)。作为可选实现,图5a示例性的示出了本技术实施例提供的ssd的再一示例图。结合图3和图5a所示,ssd还可以包括:易失性缓存240。在一个示例中,易失性缓存240可以为ddr(doubledatarate,双倍数据速率)缓存,此处所指的ddr缓存可以例如ddr4、ddr5等ssd内部的数据缓存,ddr缓存具有低延时的数据读写特性。ddr缓存为易失性的缓存,在多流场景下,本技术实施例由非易失性缓存缓存第一特性的数据流,由易失性缓存缓存第二特性的数据流,因此在设备掉电时,本技术实施例需要进一步确保易失性缓存240中的数据写入到闪存颗粒内。65.作为可选实现,图5b示例性的示出了本技术实施例提供的数据存储方法的再一可选流程图,该方法流程可由ssd控制器执行实现,参照图5b,该方法流程可以包括如下步骤。66.在步骤s501中,获取主机传输的数据流。67.在步骤s502中,确定所述数据流的数据特性。68.在步骤s503中,若所述数据特性为第一特性,将所述数据流缓存到ssd中的非易失性缓存。69.在步骤s504中,若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。70.步骤s501至步骤s504的介绍可参照前文相应部分的描述。71.在步骤s505中,若所述数据特性为第二特性,将所述数据流缓存到ssd中的易失性缓存。72.在一些实施例中,针对第二特性的数据流,本技术实施例可设置第二特性的数据流对应的streamid范围,从而ssd控制器可通过主机端传输的数据流携带的streamid,确定主机端传输的数据流的特性是否为第二特性,比如,主机端传输的数据流携带的streamid在第二特性的数据流对应的streamid范围内,则可确定主机端传输的数据流为第二特性的数据流,可由ssd中的易失性缓存进行前置缓存。73.在步骤s506中,若所述易失性缓存中缓存的数据流达到写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。74.易失性缓存中缓存的数据流写入到闪存颗粒的条件可同理参照前文相应部分的描述。75.结合图4b和图5b所示流程,可以看出,本技术实施例在设置非易失性缓存对第一特性的数据流进行前置缓存的情况下,还可设置易失性缓存对第二特性的数据流进行前置缓存。基于易失性缓存具有低延时的数据读写特性(例如易失性缓存的数据读写延时低于非易失性缓存和闪存颗粒),因此易失性缓存可被配置为对主机端传输的读写性能要求较高的数据流、热数据、数据块较大的数据流等第二特性的数据流进行缓存,从而使得ssd能够在多流技术下进一步满足主机端读写数据的多流特性要求。76.作为可选实现,本技术实施例可设置非易失性缓存的数据读写延时介于易失性缓存和闪存颗粒之间;例如,非易失性缓存的数据读写延时高于易失性缓存,低于闪存颗粒。在一个示例中,非易失性缓存为scm,易失性缓存为ddr缓存,闪存颗粒基于qlc。77.需要进一步说明的是,在设置易失性缓存缓存第二特性的数据流的情况下,为保障易失性缓存中的数据在掉电时能够写入到闪存颗粒,本技术实施例需对易失性缓存所缓存的数据量进行限制,例如易失性缓存所缓存的数据量不超过ssd中的电容支持的写入数据量。可以理解的是,尽管对易失性缓存的缓存数据量进行了限制,但是由于本技术实施例结合采用非易失性缓存来缓存第一特性的数据流,因此仍可降低主机侧传输数据流的约束,提升ssd的数据存储性能。78.为便于理解本技术实施例将主机端传输的数据写入ssd的闪存颗粒的过程,图5c示例性的示出了本技术实施例提供的数据存储方案的实现示例图,如图5c所示,主机可通过与ssd耦合的接口以及ssd的接口协议特性,向ssd传输多个数据流511至51n,n表示ssd支持的数据流数量,具体可根据实际情况而定,本技术实施例并不设限。需要说明的是,多流属于非易失存储中的重要特性,可在ssd的接口端支持不同数据特性的数据流的隔离,例如支持数据读写性能,数据冷热,数据块大小等不同特性的数据流的隔离。本技术实施例在定义n个数据流的情况下,可以根据数据读写性能,数据冷热,数据块大小等不同需求,分stream的对数据流进行隔离管理。79.在本技术实施例中,数据流511至51n的n个数据流可以分别携带数据流标识,ssd控制器可通过各个数据流携带的数据流标识,确定各个数据流的数据特性。为便于说明,假设数据流511至51k携带的数据流标识与读写性能要求低的数据流、冷数据、数据块较小的数据流中任一项的数据流标识相对应,则可确定数据流511至51k为第一特性的数据流,ssd控制器可将数据流511至51k缓存到非易失性缓存310中;假设数据流51k 1至51n携带的数据流标识与读写性能要求高的数据流、热数据、数据块较大的数据流中任一项的数据流标识相对应,则可确定数据流51k 1至51n为第二特性的数据流,ssd控制器可将数据流51k 1至51n缓存到易失性缓存240中。作为可选实现,易失性缓存240所缓存的数据量不大于电容支持的写入数据量。80.非易失性缓存310在缓存数据的情况下,针对非易失性缓存310中达到写入条件的数据流,非易失性缓存310可将该数据流写入到闪存颗粒120中。易失性缓存240在缓存数据的情况下,针对易失性缓存240中达到写入条件的数据流,易失性缓存240可将该数据写入到闪存颗粒120中。81.进一步的,在发生掉电的情况下,本技术实施例可通过ssd中的电容,将易失性缓存240中缓存的数据写入到闪存颗粒120中。82.在进一步的一些实施例中,由于非易失性缓存的数据读写延时高于易失性的缓存(例如scm的数据读写延时比dram高2至3倍),因此非易失性缓存的数据读写延时将对ssd的ftl(flashtranslationlayer,闪存转换层)的读取与更新带来一定的影响。基于此,本技术实施例可在ssd中进一步设置dma(directmemoryaccess,直接存储器访问)引擎,通过dma引擎实现ssd中存储器件之间的直接数据传输,从而隐藏非易失性缓存的数据读写延时对于ftl的影响。需要说明的是,ftl可以用于用户逻辑地址和闪存物理地址之间的映射,例如通过ftltable(表)作为用户逻辑地址和闪存物理地址的映射表。83.作为可选实现,图6示例性的示出了本技术实施例提供的ssd的又一示例图。结合图5a和图6所示,ssd中可以进一步包括:dma引擎610,该dma引擎可用于非易失性缓存与闪存颗粒之间的直接数据传输。进一步的,该dma引擎还可用于易失性缓存和闪存颗粒之间的直接数据传输、和/或非易失性缓存和易失性缓存之间的直接数据传输。84.本技术实施例在从主机端向ssd写数据时,针对主机端传输的多个数据流,ssd控制器可将第一特性的数据流缓存到非易失性缓存,将第二特性的数据流缓存到易失性缓存,并且非易失性缓存和易失性缓存中缓存的数据达到写入条件时,可写入到ssd的闪存颗粒中。基于非易失性缓存的非易失性特点、数据读写延时介于易失性缓存和闪存颗粒、同时,非易失性缓存的大容量和单bit数据存储成本较低、以及非易失性的特性,本技术实施例可在ssd发生掉电时,不必立刻将非易失性缓存中的数据写入到闪存颗粒中,从而降低前置缓存为掉电情况限制的数据量对于数据流数量的约束,提升主机侧可传输的数据流数量,提升ssd的数据存储性能。85.下面从ssd的闪存颗粒读取数据的角度,对本技术实施例提供的数据存储方案进行介绍。作为可选实现,图7a示例性的示出了本技术实施例提供的数据存储方法的又一可选流程图,该方法流程可由ssd控制器执行实现,参照图7a,该方法流程可以包括如下步骤。86.在步骤s710中,检测ssd的闪存颗粒中数据的读取频率。87.本技术实施例可对闪存颗粒中存储的数据进行读取频率的检测,从而确定出闪存颗粒中读写频率较为频繁的数据。在一些实施例中,本技术实施例可以sector(扇区)为单位,检测闪存颗粒中数据的读取频率,例如通过检测闪存颗粒中各个sector的数据读取频率,以实现检测闪存颗粒中数据的读取频率。88.在步骤s711中,若数据的读取频率高于预定频率,将所述数据搬移到所述闪存颗粒的前置缓存;其中,所述前置缓存包括非易失性缓存,所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间。89.在检测闪存颗粒中数据的读取频率的过程中,如果检测到数据的读取频率高于预定频率,为避免频繁读取的数据需要再通过闪存颗粒进行读取,本技术实施例可将频繁读取的数据搬移到闪存颗粒的前置缓存中,以提升该频繁读取的数据的读写效率。在一些实施例中,本技术实施例设置的闪存颗粒的前置缓存可以包括非易失性缓存,本技术实施例可将频繁读取的数据,从闪存颗粒搬移到所述非易失性缓存。90.在一些实施例中,在将数据从闪存颗粒搬移到前置缓存时,本技术实施例可以sector的最小物理单元为数据搬移的单位。例如,本技术实施例在检测到闪存颗粒中某个sector的数据读取频率达到预定频率时,可将该sector的最小物理单元中的数据搬移到非易失性缓存。91.在一些实施例中,闪存颗粒的前置缓存可以包括非易失性缓存(例如scm)和易失性缓存(例如ddr缓存),并且非易失性缓存缓存第一特性的数据,易失性缓存缓存第二特性的数据,因此本技术实施例需针对闪存颗粒中频繁读取的数据确定数据特性;并基于频繁读取的数据的数据特性,确定数据是搬移到易失性缓存还是非易失性缓存。作为可选实现,图7b示例性的示出了本技术实施例搬移数据到前置缓存的可选方法流程图。如图7b所示,该方法流程可以包括如下步骤。92.在步骤s720中,确定读取频率高于预定频率的数据的数据特性。93.在一些实施例中,如果闪存颗粒中频繁读取的数据为读写性能较低的数据、冷数据、数据块较小的数据中的任一项,则该频繁读取的数据为第一特性的数据;如果该频繁读取的数据为读写性能较高的数据、热数据、数据块较大的数据中的任一项,则该频繁读取的数据为第二特性的数据。94.在步骤s721中,若所述数据特性为第一特性,将所述数据从闪存颗粒搬移到非易失性缓存。95.非易失性缓存的具体介绍可参照前文相应部分的描述,本技术实施例此处不再赘述。在一些实施例中,针对数据读取频率达到预定频率的sector,如果sector中数据的数据特性为第一特性,则本技术实施例可将sector的最小物理单元中的数据搬移到非易失性缓存。96.在步骤s722中,若所述数据特性为第二特性,将所述数据从闪存颗粒搬移到易失性缓存。97.易失性缓存的具体介绍可参照前文相应部分的描述,本技术实施例此处不再赘述。在一些实施例中,针对数据读取频率达到预定频率的sector,如果sector中数据的数据特性为第二特性,则本技术实施例可将sector的最小物理单元中的数据搬移到易失性缓存。98.作为可选实现,闪存颗粒在存储数据时可同步存储数据的数据流标识,本技术实施例可通过闪存颗粒中频繁读取的数据的数据流标识,确定该频繁读取的数据为第一特性的数据还是第二特性的数据。从而,针对闪存颗粒中不同数据流标识的频繁读取的数据,本技术实施例可通过不同的数据流标识的特征,实现不同特性的数据的精细化搬移控制。99.本技术实施例在前文提供相应的写数据方案的情况下,适应性的提供闪存颗粒的数据读取方案,能够在多流技术场景下,满足不同数据特性的数据的读取需求,提升从ssd中读取数据的效率。100.作为一种实现示例,在基于qlc的ssd中,本技术实施例可将scm作为闪存颗粒的前置缓存,从而基于scm的特性,将qlc需要2次pageprogram所带来的约束进行规避。101.需要说明的是,在传统技术中,闪存颗粒主要使用tlc作为闪存单元,在tlc单次pageprogram的情况下,ssd可以使用dram等易失性缓存作为前置缓存,然后通过合理的使用电容来保证掉电情况下的数据写入;但是随着虚拟化的演进,主机侧的多流特性要求越来越高,已无法通过有限的若干个数据流来满足主机侧的数据传输需求,同时,在闪存单元的技术演进过程中,伴随着qlc的大批量使用,qlc的多次pageprogram的特性,已使得传统dram的前置缓存,在面对越来越高的主机侧的多流特性时,产生局限。因此,伴随着scm作为一种全新介质的提出,本技术实施例创造性的将scm应用于ssd的数据存储方案中,从而基于scm的特性,将qlc需要2次pageprogram所带来的约束进行规避,以提升主机侧可传输的数据流数量,提升ssd的数据存储性能。102.作为一种实现示例,图8示例性的示出了本技术实施例提供的ssd的又另一示例图。参照图8所示,在多流810的数据传输场景下,ssd可以包括ssd控制器110、scm820(scm可以视为是非易失性缓存的一种示例)、ddr缓存830(ddr缓存可以视为是易失性缓存的一种示例)、基于qlc的nand闪存颗粒840(闪存颗粒的一种示例)、scm820与nand闪存颗粒840的数据通路850、ddr缓存830与nand闪存颗粒840的数据通路860。下面针对ssd的上述结构,分别进行介绍。103.多流810属于非易失存储的重要特性,主要是在ssd的接口端支持数据读写性能,数据冷热,数据块大小等不同特性的数据隔离。ssd可以支持的流数量,每个流的具体定义可由用户在主机侧进行定义。104.ssd控制器110内部可以设置fec(frontendcontroller,前端控制器)111、mec(middleendcontroller,中间端控制器)112、bec(backendcontroller,后端控制器)113等硬件加速模块,以及fep(frontendprocessor,前端处理器)114、mep(middleendprocessor,中间端处理器)115、bep(backendprocessor,后端处理器)116等片内处理器;ssd控制器通过这些硬件加速模块和片内处理器,可控制管理读写数据流,逻辑地址和物理地址的映射,nand闪存颗粒840的特性管理等操作。105.当用户从主机侧发起数据读写操作时,本技术实施例的ssd控制器可根据主机侧下发的streamid,对不同特性的数据流进行分区的读写。例如,根据主机侧下发的第一特性的数据流对应的streamid,ssd控制器可在scm820中进行第一特性的数据流的读写,根据主机侧下发的第二特性的数据流对应的streamid,ssd控制器可在ddr缓存830中进行第二特性的数据流的读写。通过不同特性的数据流的读写位置区分,ssd可确保nand闪存颗粒840在使用qlc时,不同streamid下的数据读写路径存在不同,满足多流技术下的数据多流特性要求,并且实现在异常掉电时,易失性的ddr缓存830中的数据能够写入到nand闪存颗粒840,实现数据在内存和nand闪存颗粒进出时的性能平衡。106.scm820在ssd中作为nand闪存颗粒840的前置缓存,是具有非易失特性的内存缓存。scm820的数据读写延时介于ddr等易失内存缓存和nand闪存颗粒等非易失存储介质之间,并且scm具有容量大和单bit成本比内存(例如dram)低3到5倍的特点。107.在本技术实施例中,ssd在读写数据的过程中,可根据streamid将读写性能要求低、冷数据、数据块较小的数据流(第一特性的数据流的一种示例),缓存到scm中。在这种情况下,scm的特性可以有效的将nand闪存颗粒(基于qlc)多次program所带来的约束进行规避。例如,在ssd发生掉电时,scm中缓存的数据不会出现丢失情况,从而不必立刻将scm中的数据写入到nand闪存颗粒中,规避了前置缓存的数据缓存量限制对于数据流数量的限制,能够提升主机侧传输的数据流数量,提升ssd在多流场景下的数据存储性能。108.ddr缓存830为ssd内部的易失性内存缓存,具有低延时的数据读写特性,其作为nand闪存颗粒的前置缓存,在ssd读写数据的过程中,可根据streamid,缓存读写性能要求高、热数据、数据块较大的数据流(第二特性的数据流的一种示例)。为保障ddr缓存830中的数据能够在掉电时写入到nand闪存颗粒,ddr缓存830缓存的数据量需基于ssd中的电容支持的写入数据量而定。109.nand闪存颗粒840是基于qlc的非易失性介质,在qcl以4bit为单位存储数据的情况下,nand闪存颗粒的一个wl(wordline,字线)可以具有4个page,分别为upperpage(上页)、lowerpage(下页)、middlepage(中页)、extrapage(额外页)。基于qlc的nand闪存颗粒,在pageprogram和读取时需要较长时间,因此具有较大的数据块和2次pageprogram的特性。为满足nand闪存颗粒的上述特性,在数据写入nand闪存颗粒的过程中,一般需要大量的前置缓存来保证program的成功,如果该前置缓存设置为易失性缓存,则为保障ssd掉电时的数据存储安全性,ssd需要通过设置大容量的电容来保障前置缓存中的数据能够写入到nand闪存颗粒中,这导致前置缓存中缓存的数据量会基于电容支持的写入数据量进行限制,从而导致主机侧可传输的数据流数量受限,比如主机侧仅可支持2路数据流的传输;基于此,本技术实施例通过改进ssd的数据存储方案,在ssd中引入scm和ddr缓存作为nand闪存颗粒的前置缓存,来分别缓存第一特性的数据和第二特性的数据,从而基于scm的非易失性特性,能够在ssd发生掉电时,保障数据的存储安全性,从而降低主机侧传输的数据流数量限制,提升主机侧可传输的数据流数量(例如最多支持200路数据流的传输),实现多流技术在ssd中应用的优化,提升ssd的数据存储性能。110.数据通路850用于scm820与nand闪存颗粒840的数据互通,可在scm缓存的数据达到写入条件时,将数据从scm经过数据通路850写入到nand闪存颗粒;同时,在nand闪存颗粒的某个sector被频繁读取,且该sector中的数据为第一特性的数据时,将该sector的最小物理单元中的数据,从nand闪存颗粒经过数据通路850搬移到scm。111.数据通路860用于ddr缓存830与nand闪存颗粒840的数据互通,可在ddr缓存缓存的数据达到写入条件时,将数据从ddr缓存经过数据通路860写入到nand闪存颗粒;同时,在nand闪存颗粒的某个sector被频繁读取,且该sector中的数据为第二特性的数据时,将该sector的最小物理单元中的数据,从nand闪存颗粒经过数据通路860搬移到ddr缓存。112.进一步的,在掉电时,ddr缓存中的数据可通过数据通路860写入到nand闪存颗粒840。113.进一步的,dma引擎610可用于scm820与nand闪存颗粒840之间的直接数据传输,和/或,ddr缓存与nand闪存颗粒840之间的直接数据传输。114.需要说明的是,如果nand闪存颗粒基于slc、mlc、tlc等闪存单元,则基于slc、mlc、tlc单次pageprogram的特性,ssd可以使用dram缓存等易失性缓存,作为nand闪存颗粒的前置缓存。115.本技术实施例能够通过非易失性缓存的特性,在闪存颗粒使用单位bit数较多的闪存单元时,将闪存颗粒多次的pageprogram所带来的数据流数量限制进行规避,并且解决了ssd在异常掉电时需要大容量电容将前置缓存中的数据写入到闪存颗粒的约束,能够提升主机侧传输的数据流数量,实现多流技术在sdd应用时的优化,提升ssd的数据存储性能。进一步的,在数据多流特性下,基于不同的数据特性,实现了数据在非易失性缓存和闪存颗粒、易失性缓存和闪存颗粒、易失性缓存和非易失性缓存与闪存颗粒之间的分区管理及控制。进一步的,通过引入dma引擎,有效的使能非易失性缓存的大容量、低成本的特性,并通过dma的硬件加速,实现了非易失性缓存在读写延时上的优化。116.上文描述了本技术实施例提供的多个实施例方案,各实施例方案介绍的各可选方式可在不冲突的情况下相互结合、交叉引用,从而延伸出多种可能的实施例方案,这些均可认为是本技术实施例披露、公开的实施例方案。117.虽然本技术实施例披露如上,但本技术并非限定于此。任何本领域技术人员,在不脱离本技术的精神和范围内,均可作各种更动与修改,因此本技术的保护范围应当以权利要求所限定的范围为准。当前第1页12当前第1页12

技术领域:

:1.本技术实施例涉及存储器

技术领域:

:,具体涉及一种数据存储方法、ssd控制器、ssd及电子设备。

背景技术:

::2.ssd(solidstatedisk,固态硬盘)是使用固态电子存储芯片阵列制成的硬盘,其可以采用闪存颗粒作为存储介质。相比于传统的机械硬盘,ssd具有读写速度快、功耗低、噪音低、轻便等优点,因此ssd在存储领域得到了广泛的应用。3.在multi-stream(多流)技术下,ssd可通过multi-stream协议,将主机端传输的数据流在闪存颗粒中进行分区存放,以实现ssd的盘内区域隔离。然而,出于ssd掉电时的数据存储安全性、以及闪存颗粒可能多次page(页)program(编程)的考虑,ssd可支持的多流数量会存在一定的限制,因此如何优化ssd的数据存储方案,以提升ssd支持的多流数量,从而提升ssd的数据存储性能,成为了本领域技术人员亟需解决的技术问题。技术实现要素:4.有鉴于此,本技术实施例提供一种数据存储方法、ssd控制器、ssd及电子设备,以提升ssd支持的多流数量,从而提升ssd的数据存储性能。5.为实现上述目的,本技术实施例提供如下技术方案。6.第一方面,本技术实施例提供一种数据存储方法,包括:获取主机传输的数据流;将所述数据流缓存到ssd的非易失性缓存;其中,所述非易失性缓存为ssd的闪存颗粒的前置缓存,并且所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间;若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到所述闪存颗粒。7.第二方面,本技术实施例提供一种数据存储方法,包括:检测ssd的闪存颗粒中数据的读取频率;若数据的读取频率高于预定频率,将所述数据搬移到所述闪存颗粒的前置缓存;所述前置缓存包括非易失性缓存,所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间。8.第三方面,本技术实施例提供一种ssd控制器,所述ssd控制器被配置为执行如上述第一方面所述的数据存储方法,或者,如上述第二方面所述的数据存储方法。9.第四方面,本技术实施例提供一种ssd,包括:如上述所述的ssd控制器、非易失性缓存、以及闪存颗粒;其中,所述非易失性缓存作为所述闪存颗粒的前置缓存,用于缓存主机传输至所述ssd的数据流;所述非易失性缓存的数据读写延时介于所述ssd的易失性缓存和闪存颗粒之间。10.第五方面,本技术实施例提供一种电子设备,包括主机以及如上述所述的ssd,所述主机与所述ssd之间通过多流协议传输数据。11.本技术实施例在ssd的闪存颗粒使用单位bit数较多的闪存单元,并且闪存颗粒需要进行多次pageprogram时,可在ssd中设置非易失性缓存作为闪存颗粒的前置缓存,并且该非易失性缓存的数据读写延时介于ssd中的易失性缓存和非易失性的闪存颗粒之间。从而,在ssd获取到主机端传输的数据流时,本技术实施例可将所述数据流缓存到ssd中的非易失性缓存中,并且非易失性缓存中的数据流达到预设的写入条件时,可写入到闪存颗粒中,以实现多流场景下,数据流在ssd中的分区隔离存储。由于本技术实施例使用非易失性缓存作为闪存颗粒的前置缓存,来缓存主机侧传输的数据流,因此即使ssd发生掉电情况,本技术实施例也可保障非易失性缓存中的数据不出现丢失,而不必在掉电时立刻将非易失性缓存中的数据写入到闪存颗粒中;从而,本技术实施例可规避ssd中的电容对于前置缓存所缓存的数据量限制,避免主机侧的数据流数量所受的限制,从而提升主机侧在多流场景下可传输给ssd的数据流数量,提升ssd的数据存储性能。附图说明12.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。13.图1a为ssd的结构示例图。14.图1b为闪存颗粒的类型示例图。15.图2为应用ssd的电子设备的示例图。16.图3为本技术实施例提供的ssd的另一示例图。17.图4a为本技术实施例提供的数据存储方法的流程图。18.图4b为本技术实施例提供的数据存储方法的另一流程图。19.图5a为本技术实施例提供的ssd的再一示例图。20.图5b为本技术实施例提供的数据存储方法的再一流程图。21.图5c为本技术实施例提供的数据存储方案的实现示例图。22.图6为本技术实施例提供的ssd的又一示例图。23.图7a为本技术实施例提供的数据存储方法的又一流程图。24.图7b为本技术实施例搬移数据到前置缓存的方法流程图。25.图8为本技术实施例提供的ssd的又另一示例图。具体实施方式26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。27.图1a示例性的示出了ssd的结构示例图,如图1a所示,ssd可以包括:ssd控制器110和闪存颗粒120。ssd控制器110为ssd中的主控芯片,主要实现ssd中的数据存储控制和管理,例如ssd控制器可管理用户(一般为主机侧)传输至ssd进行读写的数据流、管理逻辑地址和物理地址的映射、管理闪存颗粒的特性等。闪存颗粒120为ssd中存储数据的存储介质,在一些实施例中,闪存颗粒可以是非易失性的存储介质。例如,ssd中可以使用nand闪存颗粒,其中,nand闪存是一种非易失性存储技术,即断电后仍能保存数据。28.闪存颗粒(例如nand闪存颗粒)可以由多个以bit(比特)为单位的闪存单元构成,一个闪存单元存储数据的单位bit数可以是一位或者多位。基于闪存颗粒中的每个闪存单元存储数据的单位bit数,闪存颗粒可以分为多种不同的类型。也就是说,基于闪存颗粒中电子单元的密度大小,闪存颗粒可以具有不同的类型。图1b示例性的示出了闪存颗粒的类型示例图,可进行参照。如图1b所示,闪存颗粒可以分为slc(singlelevelcell,单层单元)、mlc(multilevelcell,多层单元)、tlc(triplelevelcell,三层单元)、qlc(quadlevelcell,四层单元)等多种类型;其中,基于slc的闪存颗粒以1bit为单位存储数据,基于mlc的闪存颗粒以2bit为单位存储数据,基于tlc的闪存颗粒以3bit为单位存储数据,基于qlc的闪存颗粒以4bit为单位存储数据。需要说明的是,闪存单元的单位bit数越多,则闪存颗粒每bit的数据存储成本越低,但是理论上的数据读写速度越慢;例如qlc和tlc相比于slc和mlc具有更低的数据存储成本,但是数据读写速度则较慢。因此qlc等单位bit数较多的闪存单元比较适用于数据存储量较大且需求成本较低的数据存储场景,例如数据仓库等企业级的数据存储场景。29.可以看出,随着闪存单元存储数据的单位bit数增多(例如闪存颗粒基于qlc等单位bit数较多的闪存单元存储数据),ssd能够降低数据的单bit存储成本,但是在实际应用过程中,闪存单元的单位bit数增多,将带来闪存颗粒的数据稳定性变差、读写page的时间变长,写入数据需要多次pageprogram(编程)等挑战,这导致ssd需要为闪存颗粒设置大容量的前置缓存,以满足闪存颗粒多次pageprogram的需求。在此情况下,如果该前置缓存选用大容量的易失性缓存(例如ddr缓存),则出于ssd掉电时的数据存储安全性考虑,ssd需要为该前置缓存设置大容量的电容,以在ssd掉电时,通过该大容量的电容将前置缓存中的数据写入到闪存颗粒。而在multi-stream场景下,为保障前置缓存中缓存的数据流,能够在掉电时写入到闪存颗粒中,前置缓存需要基于电容可支持的写入数据量来缓存数据,这导致ssd需要基于电容可支持的写入数据量来限制多流数量,致使ssd在应用multi-stream技术时,存在多流数量限制。30.为便于说明上述问题,以基于qlc的闪存颗粒为例,图2示例性的示出了应用ssd的电子设备的示例图,如图2所示,该电子设备可以包括:主机210、接口220、ssd230。其中,主机210可以例如与ssd230耦合的计算机,主机中可设置处理器等用于数据处理、计算的处理核心。接口220可以是主机210与ssd230耦合接口,并支持multi-stream协议。ssd230为主机210耦合的固态硬盘,其通过接口220与主机210交换数据,在本示例中,ssd可以包括ssd控制器110、基于qlc的闪存颗粒120、易失性缓存240和电容250。31.在主机与ssd传输数据的过程中,主机与ssd可通过multi-stream协议传输数据,并且ssd可通过multi-stream技术,将主机端传输的数据进行分区存放。具体来说,在multi-stream技术下,主机端可传输给ssd多个数据流,并且数据流会携带streamid(数据流标识);ssd可根据主机端提供的streamid,将具有相同streamid的数据(相同streamid的数据一般具有相同或相似的数据特性)写入到闪存颗粒的相似物理空间中,以实现ssd的盘内区域隔离。32.结合图2所示,在multi-stream场景下,易失性缓存240作为闪存颗粒120的前置缓存,易失性缓存240可以缓存主机210传输给ssd的多个数据流,并且该多个数据流可通过易失性缓存240写入到闪存颗粒120中,实现不同streamid的数据流在闪存颗粒中的分区存放。在一个示例中,易失性缓存240可以为ddr(doubledatarate,双倍数据速率)缓存,ddr缓存可以dram(dynamicrandomaccessmemory,动态随机存取存储器)为介质。33.然而,由于易失性缓存240的易失性特点(即掉电时,易失性缓存240中的数据将会丢失),为保障ssd的数据存储安全,易失性缓存240中的数据需要在掉电时写入到闪存颗粒中,此时,ssd控制器110需要驱动电容250来控制易失性缓存240在掉电时,将数据写入到闪存颗粒。在此情况下,由于基于qlc的闪存颗粒需要通过多次的program进行写数据,在多流并发下,为避免易失性缓存240中缓存的数据过多,难以在掉电情况下完全写入到闪存颗粒中而出现数据丢失,因此需要在闪存颗粒每次program的间隔内,限制易失性缓存240所缓存的数据量。例如,在闪存颗粒每次program的间隔内,需要限制易失性缓存240所缓存的数据量不超过电容250可支持的写入数据量,从而避免易失性缓存240中超出的数据在掉电时难以写入到闪存颗粒中,出现数据丢失的不安全情况。34.需要说明的是,闪存颗粒中的一个block通常包含多个page,因此在multi-stream技术下,闪存颗粒在块中读写数据时,涉及到对于page的读写操作。此时,如果闪存颗粒使用qlc等单位bit数较多的闪存单元,则闪存颗粒需要通过多次的program进行写数据,同时闪存颗粒需要较长的时间进行page读写、闪存颗粒的tprog和tr的时间均较长(tprog是指数据编程写入page的时间,tr是指数据从page读取的时间)。35.通过上述描述可以看出,在ssd使用易失性缓存作为闪存颗粒的前置缓存时,如果闪存颗粒使用qlc等单位bit数较多的闪存单元,则出于掉电时的数据存储安全性、以及闪存颗粒可能多次pageprogram的考虑,需要基于电容能支持的写入数据量,来限制易失性缓存所缓存的数据量,这导致主机侧并发传输的数据流数量需要进行限制,以避免较多的数据流同时缓存在易失性缓存;而这进一步导致主机侧难以并发传输数量较多的数据流,从而对于multi-stream技术的应用造成限制,降低了ssd的数据存储性能。36.解决上述问题的一个思路是,由于主机侧可传输的数据流数量与缓存所能保存的数据量呈正相关,因此可在ssd中设置更大容量的电容,以提升电容所能支持的易失性缓存的写入数据量,然而ssd的电路板空间有限,更大容量的电容设置将挤占ssd的板上空间,并且提升了ssd的设计难度。37.基于此,本技术实施例提供改进型的技术思路,在ssd中设置大容量和单bit数据存储成本较低的非易失性缓存,通过非易失性缓存来缓存multi-stream场景下的数据流,并且基于非易失性缓存的非易失特性,规避ssd在掉电时数据可能出现丢失的不安全问题。38.基于上述思路,本技术实施例考虑在ssd中引入非易失性缓存,该非易失性缓存的数据读写延时介于易失性缓存和闪存颗粒之间(闪存颗粒可以为非易失性的存储介质);并且将该非易失性缓存作为闪存颗粒的前置缓存,通过改进多流技术下的数据存储方案,使得闪存颗粒在使用qlc等单位bit数较多的闪存单元时,本技术实施例能够通过该非易失性缓存的非易失特性,将闪存颗粒的tprog和tr的时间较长、较长的page读写时间的缺点所带来的约束进行规避,从而在ssd掉电时,仍能通过该非易失性缓存保存数据,而不必将数据立刻写入到闪存颗粒中,进而本技术实施例可规避电容所能支持的写入数据量对于ssd缓存数据的限制,提升multi-stream的多流数量,提升ssd的数据存储性能。39.作为可选实现,图3示例性的示出了本技术实施例提供的ssd的另一示例图。参照图3所示,在本技术实施例中,ssd可以包括:ssd控制器110、闪存颗粒120、非易失性缓存310;闪存颗粒120可以使用单位bit数较多的闪存单元,比如闪存颗粒120使用的闪存单元存储数据的单位bit数为4(例如基于qlc的闪存颗粒),或者大于4;在闪存颗粒使用单位bit数较多的闪存单元时,闪存颗粒需要通过多次的pageprogram进行写数据。40.非易失性缓存310为ssd中设置的非易失性的内存缓存,并且非易失性缓存310的数据读写延时介于易失性缓存和闪存颗粒120之间。41.在一个示例中,非易失性缓存310可以为scm(storageclassmemory,储存级存储器),例如pcm(phase-changememory,相变存储器)、3d-xpoint等;scm具有容量大和单bit成本比dram等易失性缓存低3到5倍的特点。42.在本技术实施例中,非易失性缓存可作为闪存颗粒的前置缓存,用于对主机侧传输的数据流进行缓存,并且非易失性缓存中的数据流可写入到闪存颗粒中。在一些实施例中,主机端在传输多个数据流时,数据流可通过非易失性缓存作为桥梁,写入ssd的闪存颗粒(简称为写数据过程);并且闪存颗粒中的数据,可通过非易失性缓存作为桥梁进行读取(简称为读数据过程)。下面将分别从写数据和读数据的角度,对本技术实施例提供的数据存储方法进行介绍。43.作为可选实现,图4a示例性的示出了本技术实施例提供的数据存储方法的可选流程图。该方法流程可由ssd执行实现,例如由ssd中的ssd控制器执行实现。需要说明的是,ssd控制器内部可设置硬件加速模块和片内处理器,本技术实施例可结合ssd控制器内部的硬件逻辑以及片内处理器的程序逻辑,执行实现该方法流程。参照图4a,该方法流程可以包括如下步骤。44.在步骤s410中,获取主机传输的数据流。45.在步骤s411中,将所述数据流缓存到ssd的非易失性缓存。46.在步骤s412中,若所述非易失性缓存中的缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。47.在一些实施例中,数据流从非易失性缓存写入到闪存颗粒的写入条件例如:任一数据流在非易失性缓存中缓存的数据量达到闪存颗粒的最小编程单元的数据量要求,则可将该数据流写入到闪存颗粒中;或者,在发生掉电时,如果非易失性缓存中缓存的数据流的数据量未达到最小编程单元的数据量要求,则补足数据流的数据量,从而将补足数据量的数据流写入到闪存颗粒中。48.在一个示例中,假设闪存颗粒的最小编程单元要求的数据量为96kb(最小编程单元的具体数据量要求可根据闪存颗粒的具体情况设置,本技术实施例并不设限),主机侧以4kb为单位持续性的传输数据流,则在非易失性缓存缓存主机侧传输的数据流后,如果任一个数据流的数据量达到96kb,则该数据流可从非易失性缓存写入到闪存颗粒中。在进一步的示例中,如果任一个数据流在非易失性缓存中所缓存的数据量未达到96kb时,发生掉电情况,则非易失性缓存可将该数据流的数据量补足到96kb(例如通过空白值或者其他设定数值进行数据量的补充),并将补足到96kb的数据流从非易失性缓存写入到闪存颗粒中。49.在一些实施例中,本技术实施例在将数据流从非易失性缓存写入到闪存颗粒时,可根据数据流携带的数据流标识,将不同数据流标识的数据流写入到闪存颗粒的不同区域,以实现不同数据流标识的数据在ssd中的分区隔离存储。50.本技术实施例在ssd的闪存颗粒使用单位bit数较多的闪存单元,并且闪存颗粒需要进行多次pageprogram时,可在ssd中设置非易失性缓存作为闪存颗粒的前置缓存,并且该非易失性缓存的数据读写延时介于ssd中的易失性缓存和非易失性的闪存颗粒之间。从而,在ssd获取到主机端传输的数据流时,本技术实施例可将所述数据流缓存到ssd中的非易失性缓存中,并且非易失性缓存中的数据流达到预设的写入条件时,可写入到闪存颗粒中,以实现多流场景下,数据流在ssd中的分区隔离存储。由于本技术实施例使用非易失性缓存作为闪存颗粒的前置缓存,来缓存主机侧传输的数据流,因此即使ssd发生掉电情况,本技术实施例也可保障非易失性缓存中的数据不出现丢失,而不必在掉电时立刻将非易失性缓存中的数据写入到闪存颗粒中;从而,本技术实施例可规避ssd中的电容对于前置缓存所缓存的数据量限制,进而避免主机侧的数据流数量受到限制,提升主机侧在多流场景下可传输给ssd的数据流数量,提升ssd的数据存储性能。51.在本技术实施例的一些实施例中,ssd设置的非易失性缓存可缓存主机侧传输的所有数据流,也可仅设置非易失性缓存对主机侧传输的特定特性的数据流进行缓存。作为可选实现,本技术实施例可设置非易失性缓作为闪存颗粒的前置缓存,并且缓存多流技术下第一特性的数据流(例如读写性能要求低的数据流、冷数据、数据块较小的数据流等)。也就是说,主机端在传输多个数据流时,第一特性的数据流可通过非易失性缓存作为桥梁,写入ssd的闪存颗粒;并且闪存颗粒中第一特性的数据,可通过非易失性缓存作为桥梁进行读取。52.作为可实现,图4b示例性的示出了本技术实施例提供的数据存储方法的另一可选流程图。该方法流程可由ssd控制器执行实现,参照图4b,该方法流程可以包括如下步骤。53.在步骤s420中,获取主机传输的数据流。54.在步骤s421中,确定所述数据流的数据特性。55.在本技术实施例中,主机可通过与ssd的接口协议(例如multi-stream协议),将数据流传输到ssd,从而ssd中的ssd控制器可获取主机传输的多个数据流,并确定每个数据流的数据特性。56.在一些实施例中,在multi-stream技术下,基于ssd在多流的接口协议特性,主机可根据数据流的读写特征(例如,数据流的冷热特征、读写性能要求、数据块大小等),为传输给ssd的数据流标记streamid,从而主机可将携带streamid的数据流传输给ssd。此时,ssd控制器可获取到主机端传输的携带streamid的多个数据流,并基于每个数据流携带的streamid,确定每个数据流的数据特性。57.作为可选实现,本技术实施例可将数据流分为第一特性的数据流和第二特性的数据流,例如,第一特性的数据流包括读写性能要求低的数据流、冷数据、数据块较小的数据流,第二特性的数据流包括读写性能要求高的数据流、热数据、数据块较大的数据流等。也就是说,在可能的示例中,第一特性的数据流的读写性能要求低于第二特性的数据流、或者第一特性的数据流的数据块小于第二特性的数据流、或者第一特性的数据流为冷数据并且第二特性的数据流为热数据。冷数据可以理解为是访问频率较低的数据,比如企业备份数据、操作日志数据等,热数据可以理解为是频繁访问的数据,比如metadata(元数据)等。58.在本技术实施例中,主机端传输的第一特性的数据流可由ssd中设置的非易失性缓存(例如scm)进行前置缓存。作为可选实现,针对第一特性的数据流,本技术实施例可设置第一特性的数据对应的streamid范围,从而ssd控制器可通过主机端传输的数据流携带的streamid,确定主机端传输的数据流的特性是否为第一特性,比如,主机端传输的数据流携带的streamid在第一特性的数据流对应的streamid范围内,则可确定主机端传输的数据流为第一特性的数据流,可由ssd中的非易失性缓存进行前置缓存。59.在步骤s422中,若所述数据特性为第一特性,将所述数据流缓存到ssd中的非易失性缓存。60.ssd控制器在确定主机传输的数据流的数据特性为第一特性时(例如数据流携带的streamid在第一特性的数据流对应的streamid范围内),则ssd控制器可确定由非易失性缓存进行数据流的缓存,从而ssd控制器可将数据流缓存到非易失性缓存中。在一个示例中,主机端传输的读写性能要求较低的数据流、冷数据、数据块较小的数据流可缓存到非易失性缓存中,例如,ssd控制器在基于数据流携带的streamid,确定数据流为读写性能要求较低的数据流、冷数据、数据块较小的数据流中的任一项时,可基于数据流携带的streamid,将数据流缓存到非易失性缓存。61.在步骤s423中,若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。62.在进一步的一些实施例中,基于非易失性缓存作为闪存颗粒的前置缓存,因此非易失性缓存所缓存的数据达到一定条件时,需要写入到前置缓存中。作为可选实现,本技术实施例可设置数据流从缓存(包括非易失性缓存和易失性缓存)写入到闪存颗粒的写入条件,当非易失性缓存中缓存的数据流达到该写入条件时,本技术实施例可将数据流从非易失性缓存写入到闪存颗粒。具体的写入条件内容可参照前文相应部分的描述。63.针对第一特性的数据流,本技术实施例可将非易失性缓存作为闪存颗粒和主机之间的中间数据缓存,从而利用非易失性缓存的数据读写延时高于易失性缓存、低于闪存颗粒,并且非易失性缓存的大容量、单bit数据存储成本较低以及非易失性的特性,避免ssd在掉电时需要通过电容将前置缓存中的数据立刻写入到闪存颗粒的情况,进而将闪存颗粒多次的pageprogram所带来的约束进行规避,提升了多流场景下主机侧可传输的数据流数量,减少了主机侧的数据传输约束,为提升ssd更大的存储性能提供了可能。进一步的,通过非易失性缓存对第一特性的数据进行缓存和管理,可使得ssd能够在多流技术下满足主机端读写数据的多流特性要求。64.在进一步的一些实施例中,本技术实施例也可在ssd中设置易失性缓存,该易失性缓存可用于在非多流场景下,作为闪存颗粒的前置缓存来缓存数据;该易失性缓存也可在多流场景下,作为闪存颗粒的前置缓存,用于对主机侧传输的第二特性的数据流进行缓存(例如缓存读写性能要求高的数据流、热数据、数据块较大的数据流等)。作为可选实现,图5a示例性的示出了本技术实施例提供的ssd的再一示例图。结合图3和图5a所示,ssd还可以包括:易失性缓存240。在一个示例中,易失性缓存240可以为ddr(doubledatarate,双倍数据速率)缓存,此处所指的ddr缓存可以例如ddr4、ddr5等ssd内部的数据缓存,ddr缓存具有低延时的数据读写特性。ddr缓存为易失性的缓存,在多流场景下,本技术实施例由非易失性缓存缓存第一特性的数据流,由易失性缓存缓存第二特性的数据流,因此在设备掉电时,本技术实施例需要进一步确保易失性缓存240中的数据写入到闪存颗粒内。65.作为可选实现,图5b示例性的示出了本技术实施例提供的数据存储方法的再一可选流程图,该方法流程可由ssd控制器执行实现,参照图5b,该方法流程可以包括如下步骤。66.在步骤s501中,获取主机传输的数据流。67.在步骤s502中,确定所述数据流的数据特性。68.在步骤s503中,若所述数据特性为第一特性,将所述数据流缓存到ssd中的非易失性缓存。69.在步骤s504中,若所述非易失性缓存中缓存的数据流达到预设的写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。70.步骤s501至步骤s504的介绍可参照前文相应部分的描述。71.在步骤s505中,若所述数据特性为第二特性,将所述数据流缓存到ssd中的易失性缓存。72.在一些实施例中,针对第二特性的数据流,本技术实施例可设置第二特性的数据流对应的streamid范围,从而ssd控制器可通过主机端传输的数据流携带的streamid,确定主机端传输的数据流的特性是否为第二特性,比如,主机端传输的数据流携带的streamid在第二特性的数据流对应的streamid范围内,则可确定主机端传输的数据流为第二特性的数据流,可由ssd中的易失性缓存进行前置缓存。73.在步骤s506中,若所述易失性缓存中缓存的数据流达到写入条件,将达到所述写入条件的数据流,写入到闪存颗粒。74.易失性缓存中缓存的数据流写入到闪存颗粒的条件可同理参照前文相应部分的描述。75.结合图4b和图5b所示流程,可以看出,本技术实施例在设置非易失性缓存对第一特性的数据流进行前置缓存的情况下,还可设置易失性缓存对第二特性的数据流进行前置缓存。基于易失性缓存具有低延时的数据读写特性(例如易失性缓存的数据读写延时低于非易失性缓存和闪存颗粒),因此易失性缓存可被配置为对主机端传输的读写性能要求较高的数据流、热数据、数据块较大的数据流等第二特性的数据流进行缓存,从而使得ssd能够在多流技术下进一步满足主机端读写数据的多流特性要求。76.作为可选实现,本技术实施例可设置非易失性缓存的数据读写延时介于易失性缓存和闪存颗粒之间;例如,非易失性缓存的数据读写延时高于易失性缓存,低于闪存颗粒。在一个示例中,非易失性缓存为scm,易失性缓存为ddr缓存,闪存颗粒基于qlc。77.需要进一步说明的是,在设置易失性缓存缓存第二特性的数据流的情况下,为保障易失性缓存中的数据在掉电时能够写入到闪存颗粒,本技术实施例需对易失性缓存所缓存的数据量进行限制,例如易失性缓存所缓存的数据量不超过ssd中的电容支持的写入数据量。可以理解的是,尽管对易失性缓存的缓存数据量进行了限制,但是由于本技术实施例结合采用非易失性缓存来缓存第一特性的数据流,因此仍可降低主机侧传输数据流的约束,提升ssd的数据存储性能。78.为便于理解本技术实施例将主机端传输的数据写入ssd的闪存颗粒的过程,图5c示例性的示出了本技术实施例提供的数据存储方案的实现示例图,如图5c所示,主机可通过与ssd耦合的接口以及ssd的接口协议特性,向ssd传输多个数据流511至51n,n表示ssd支持的数据流数量,具体可根据实际情况而定,本技术实施例并不设限。需要说明的是,多流属于非易失存储中的重要特性,可在ssd的接口端支持不同数据特性的数据流的隔离,例如支持数据读写性能,数据冷热,数据块大小等不同特性的数据流的隔离。本技术实施例在定义n个数据流的情况下,可以根据数据读写性能,数据冷热,数据块大小等不同需求,分stream的对数据流进行隔离管理。79.在本技术实施例中,数据流511至51n的n个数据流可以分别携带数据流标识,ssd控制器可通过各个数据流携带的数据流标识,确定各个数据流的数据特性。为便于说明,假设数据流511至51k携带的数据流标识与读写性能要求低的数据流、冷数据、数据块较小的数据流中任一项的数据流标识相对应,则可确定数据流511至51k为第一特性的数据流,ssd控制器可将数据流511至51k缓存到非易失性缓存310中;假设数据流51k 1至51n携带的数据流标识与读写性能要求高的数据流、热数据、数据块较大的数据流中任一项的数据流标识相对应,则可确定数据流51k 1至51n为第二特性的数据流,ssd控制器可将数据流51k 1至51n缓存到易失性缓存240中。作为可选实现,易失性缓存240所缓存的数据量不大于电容支持的写入数据量。80.非易失性缓存310在缓存数据的情况下,针对非易失性缓存310中达到写入条件的数据流,非易失性缓存310可将该数据流写入到闪存颗粒120中。易失性缓存240在缓存数据的情况下,针对易失性缓存240中达到写入条件的数据流,易失性缓存240可将该数据写入到闪存颗粒120中。81.进一步的,在发生掉电的情况下,本技术实施例可通过ssd中的电容,将易失性缓存240中缓存的数据写入到闪存颗粒120中。82.在进一步的一些实施例中,由于非易失性缓存的数据读写延时高于易失性的缓存(例如scm的数据读写延时比dram高2至3倍),因此非易失性缓存的数据读写延时将对ssd的ftl(flashtranslationlayer,闪存转换层)的读取与更新带来一定的影响。基于此,本技术实施例可在ssd中进一步设置dma(directmemoryaccess,直接存储器访问)引擎,通过dma引擎实现ssd中存储器件之间的直接数据传输,从而隐藏非易失性缓存的数据读写延时对于ftl的影响。需要说明的是,ftl可以用于用户逻辑地址和闪存物理地址之间的映射,例如通过ftltable(表)作为用户逻辑地址和闪存物理地址的映射表。83.作为可选实现,图6示例性的示出了本技术实施例提供的ssd的又一示例图。结合图5a和图6所示,ssd中可以进一步包括:dma引擎610,该dma引擎可用于非易失性缓存与闪存颗粒之间的直接数据传输。进一步的,该dma引擎还可用于易失性缓存和闪存颗粒之间的直接数据传输、和/或非易失性缓存和易失性缓存之间的直接数据传输。84.本技术实施例在从主机端向ssd写数据时,针对主机端传输的多个数据流,ssd控制器可将第一特性的数据流缓存到非易失性缓存,将第二特性的数据流缓存到易失性缓存,并且非易失性缓存和易失性缓存中缓存的数据达到写入条件时,可写入到ssd的闪存颗粒中。基于非易失性缓存的非易失性特点、数据读写延时介于易失性缓存和闪存颗粒、同时,非易失性缓存的大容量和单bit数据存储成本较低、以及非易失性的特性,本技术实施例可在ssd发生掉电时,不必立刻将非易失性缓存中的数据写入到闪存颗粒中,从而降低前置缓存为掉电情况限制的数据量对于数据流数量的约束,提升主机侧可传输的数据流数量,提升ssd的数据存储性能。85.下面从ssd的闪存颗粒读取数据的角度,对本技术实施例提供的数据存储方案进行介绍。作为可选实现,图7a示例性的示出了本技术实施例提供的数据存储方法的又一可选流程图,该方法流程可由ssd控制器执行实现,参照图7a,该方法流程可以包括如下步骤。86.在步骤s710中,检测ssd的闪存颗粒中数据的读取频率。87.本技术实施例可对闪存颗粒中存储的数据进行读取频率的检测,从而确定出闪存颗粒中读写频率较为频繁的数据。在一些实施例中,本技术实施例可以sector(扇区)为单位,检测闪存颗粒中数据的读取频率,例如通过检测闪存颗粒中各个sector的数据读取频率,以实现检测闪存颗粒中数据的读取频率。88.在步骤s711中,若数据的读取频率高于预定频率,将所述数据搬移到所述闪存颗粒的前置缓存;其中,所述前置缓存包括非易失性缓存,所述非易失性缓存的数据读写延时介于ssd中的易失性缓存和闪存颗粒之间。89.在检测闪存颗粒中数据的读取频率的过程中,如果检测到数据的读取频率高于预定频率,为避免频繁读取的数据需要再通过闪存颗粒进行读取,本技术实施例可将频繁读取的数据搬移到闪存颗粒的前置缓存中,以提升该频繁读取的数据的读写效率。在一些实施例中,本技术实施例设置的闪存颗粒的前置缓存可以包括非易失性缓存,本技术实施例可将频繁读取的数据,从闪存颗粒搬移到所述非易失性缓存。90.在一些实施例中,在将数据从闪存颗粒搬移到前置缓存时,本技术实施例可以sector的最小物理单元为数据搬移的单位。例如,本技术实施例在检测到闪存颗粒中某个sector的数据读取频率达到预定频率时,可将该sector的最小物理单元中的数据搬移到非易失性缓存。91.在一些实施例中,闪存颗粒的前置缓存可以包括非易失性缓存(例如scm)和易失性缓存(例如ddr缓存),并且非易失性缓存缓存第一特性的数据,易失性缓存缓存第二特性的数据,因此本技术实施例需针对闪存颗粒中频繁读取的数据确定数据特性;并基于频繁读取的数据的数据特性,确定数据是搬移到易失性缓存还是非易失性缓存。作为可选实现,图7b示例性的示出了本技术实施例搬移数据到前置缓存的可选方法流程图。如图7b所示,该方法流程可以包括如下步骤。92.在步骤s720中,确定读取频率高于预定频率的数据的数据特性。93.在一些实施例中,如果闪存颗粒中频繁读取的数据为读写性能较低的数据、冷数据、数据块较小的数据中的任一项,则该频繁读取的数据为第一特性的数据;如果该频繁读取的数据为读写性能较高的数据、热数据、数据块较大的数据中的任一项,则该频繁读取的数据为第二特性的数据。94.在步骤s721中,若所述数据特性为第一特性,将所述数据从闪存颗粒搬移到非易失性缓存。95.非易失性缓存的具体介绍可参照前文相应部分的描述,本技术实施例此处不再赘述。在一些实施例中,针对数据读取频率达到预定频率的sector,如果sector中数据的数据特性为第一特性,则本技术实施例可将sector的最小物理单元中的数据搬移到非易失性缓存。96.在步骤s722中,若所述数据特性为第二特性,将所述数据从闪存颗粒搬移到易失性缓存。97.易失性缓存的具体介绍可参照前文相应部分的描述,本技术实施例此处不再赘述。在一些实施例中,针对数据读取频率达到预定频率的sector,如果sector中数据的数据特性为第二特性,则本技术实施例可将sector的最小物理单元中的数据搬移到易失性缓存。98.作为可选实现,闪存颗粒在存储数据时可同步存储数据的数据流标识,本技术实施例可通过闪存颗粒中频繁读取的数据的数据流标识,确定该频繁读取的数据为第一特性的数据还是第二特性的数据。从而,针对闪存颗粒中不同数据流标识的频繁读取的数据,本技术实施例可通过不同的数据流标识的特征,实现不同特性的数据的精细化搬移控制。99.本技术实施例在前文提供相应的写数据方案的情况下,适应性的提供闪存颗粒的数据读取方案,能够在多流技术场景下,满足不同数据特性的数据的读取需求,提升从ssd中读取数据的效率。100.作为一种实现示例,在基于qlc的ssd中,本技术实施例可将scm作为闪存颗粒的前置缓存,从而基于scm的特性,将qlc需要2次pageprogram所带来的约束进行规避。101.需要说明的是,在传统技术中,闪存颗粒主要使用tlc作为闪存单元,在tlc单次pageprogram的情况下,ssd可以使用dram等易失性缓存作为前置缓存,然后通过合理的使用电容来保证掉电情况下的数据写入;但是随着虚拟化的演进,主机侧的多流特性要求越来越高,已无法通过有限的若干个数据流来满足主机侧的数据传输需求,同时,在闪存单元的技术演进过程中,伴随着qlc的大批量使用,qlc的多次pageprogram的特性,已使得传统dram的前置缓存,在面对越来越高的主机侧的多流特性时,产生局限。因此,伴随着scm作为一种全新介质的提出,本技术实施例创造性的将scm应用于ssd的数据存储方案中,从而基于scm的特性,将qlc需要2次pageprogram所带来的约束进行规避,以提升主机侧可传输的数据流数量,提升ssd的数据存储性能。102.作为一种实现示例,图8示例性的示出了本技术实施例提供的ssd的又另一示例图。参照图8所示,在多流810的数据传输场景下,ssd可以包括ssd控制器110、scm820(scm可以视为是非易失性缓存的一种示例)、ddr缓存830(ddr缓存可以视为是易失性缓存的一种示例)、基于qlc的nand闪存颗粒840(闪存颗粒的一种示例)、scm820与nand闪存颗粒840的数据通路850、ddr缓存830与nand闪存颗粒840的数据通路860。下面针对ssd的上述结构,分别进行介绍。103.多流810属于非易失存储的重要特性,主要是在ssd的接口端支持数据读写性能,数据冷热,数据块大小等不同特性的数据隔离。ssd可以支持的流数量,每个流的具体定义可由用户在主机侧进行定义。104.ssd控制器110内部可以设置fec(frontendcontroller,前端控制器)111、mec(middleendcontroller,中间端控制器)112、bec(backendcontroller,后端控制器)113等硬件加速模块,以及fep(frontendprocessor,前端处理器)114、mep(middleendprocessor,中间端处理器)115、bep(backendprocessor,后端处理器)116等片内处理器;ssd控制器通过这些硬件加速模块和片内处理器,可控制管理读写数据流,逻辑地址和物理地址的映射,nand闪存颗粒840的特性管理等操作。105.当用户从主机侧发起数据读写操作时,本技术实施例的ssd控制器可根据主机侧下发的streamid,对不同特性的数据流进行分区的读写。例如,根据主机侧下发的第一特性的数据流对应的streamid,ssd控制器可在scm820中进行第一特性的数据流的读写,根据主机侧下发的第二特性的数据流对应的streamid,ssd控制器可在ddr缓存830中进行第二特性的数据流的读写。通过不同特性的数据流的读写位置区分,ssd可确保nand闪存颗粒840在使用qlc时,不同streamid下的数据读写路径存在不同,满足多流技术下的数据多流特性要求,并且实现在异常掉电时,易失性的ddr缓存830中的数据能够写入到nand闪存颗粒840,实现数据在内存和nand闪存颗粒进出时的性能平衡。106.scm820在ssd中作为nand闪存颗粒840的前置缓存,是具有非易失特性的内存缓存。scm820的数据读写延时介于ddr等易失内存缓存和nand闪存颗粒等非易失存储介质之间,并且scm具有容量大和单bit成本比内存(例如dram)低3到5倍的特点。107.在本技术实施例中,ssd在读写数据的过程中,可根据streamid将读写性能要求低、冷数据、数据块较小的数据流(第一特性的数据流的一种示例),缓存到scm中。在这种情况下,scm的特性可以有效的将nand闪存颗粒(基于qlc)多次program所带来的约束进行规避。例如,在ssd发生掉电时,scm中缓存的数据不会出现丢失情况,从而不必立刻将scm中的数据写入到nand闪存颗粒中,规避了前置缓存的数据缓存量限制对于数据流数量的限制,能够提升主机侧传输的数据流数量,提升ssd在多流场景下的数据存储性能。108.ddr缓存830为ssd内部的易失性内存缓存,具有低延时的数据读写特性,其作为nand闪存颗粒的前置缓存,在ssd读写数据的过程中,可根据streamid,缓存读写性能要求高、热数据、数据块较大的数据流(第二特性的数据流的一种示例)。为保障ddr缓存830中的数据能够在掉电时写入到nand闪存颗粒,ddr缓存830缓存的数据量需基于ssd中的电容支持的写入数据量而定。109.nand闪存颗粒840是基于qlc的非易失性介质,在qcl以4bit为单位存储数据的情况下,nand闪存颗粒的一个wl(wordline,字线)可以具有4个page,分别为upperpage(上页)、lowerpage(下页)、middlepage(中页)、extrapage(额外页)。基于qlc的nand闪存颗粒,在pageprogram和读取时需要较长时间,因此具有较大的数据块和2次pageprogram的特性。为满足nand闪存颗粒的上述特性,在数据写入nand闪存颗粒的过程中,一般需要大量的前置缓存来保证program的成功,如果该前置缓存设置为易失性缓存,则为保障ssd掉电时的数据存储安全性,ssd需要通过设置大容量的电容来保障前置缓存中的数据能够写入到nand闪存颗粒中,这导致前置缓存中缓存的数据量会基于电容支持的写入数据量进行限制,从而导致主机侧可传输的数据流数量受限,比如主机侧仅可支持2路数据流的传输;基于此,本技术实施例通过改进ssd的数据存储方案,在ssd中引入scm和ddr缓存作为nand闪存颗粒的前置缓存,来分别缓存第一特性的数据和第二特性的数据,从而基于scm的非易失性特性,能够在ssd发生掉电时,保障数据的存储安全性,从而降低主机侧传输的数据流数量限制,提升主机侧可传输的数据流数量(例如最多支持200路数据流的传输),实现多流技术在ssd中应用的优化,提升ssd的数据存储性能。110.数据通路850用于scm820与nand闪存颗粒840的数据互通,可在scm缓存的数据达到写入条件时,将数据从scm经过数据通路850写入到nand闪存颗粒;同时,在nand闪存颗粒的某个sector被频繁读取,且该sector中的数据为第一特性的数据时,将该sector的最小物理单元中的数据,从nand闪存颗粒经过数据通路850搬移到scm。111.数据通路860用于ddr缓存830与nand闪存颗粒840的数据互通,可在ddr缓存缓存的数据达到写入条件时,将数据从ddr缓存经过数据通路860写入到nand闪存颗粒;同时,在nand闪存颗粒的某个sector被频繁读取,且该sector中的数据为第二特性的数据时,将该sector的最小物理单元中的数据,从nand闪存颗粒经过数据通路860搬移到ddr缓存。112.进一步的,在掉电时,ddr缓存中的数据可通过数据通路860写入到nand闪存颗粒840。113.进一步的,dma引擎610可用于scm820与nand闪存颗粒840之间的直接数据传输,和/或,ddr缓存与nand闪存颗粒840之间的直接数据传输。114.需要说明的是,如果nand闪存颗粒基于slc、mlc、tlc等闪存单元,则基于slc、mlc、tlc单次pageprogram的特性,ssd可以使用dram缓存等易失性缓存,作为nand闪存颗粒的前置缓存。115.本技术实施例能够通过非易失性缓存的特性,在闪存颗粒使用单位bit数较多的闪存单元时,将闪存颗粒多次的pageprogram所带来的数据流数量限制进行规避,并且解决了ssd在异常掉电时需要大容量电容将前置缓存中的数据写入到闪存颗粒的约束,能够提升主机侧传输的数据流数量,实现多流技术在sdd应用时的优化,提升ssd的数据存储性能。进一步的,在数据多流特性下,基于不同的数据特性,实现了数据在非易失性缓存和闪存颗粒、易失性缓存和闪存颗粒、易失性缓存和非易失性缓存与闪存颗粒之间的分区管理及控制。进一步的,通过引入dma引擎,有效的使能非易失性缓存的大容量、低成本的特性,并通过dma的硬件加速,实现了非易失性缓存在读写延时上的优化。116.上文描述了本技术实施例提供的多个实施例方案,各实施例方案介绍的各可选方式可在不冲突的情况下相互结合、交叉引用,从而延伸出多种可能的实施例方案,这些均可认为是本技术实施例披露、公开的实施例方案。117.虽然本技术实施例披露如上,但本技术并非限定于此。任何本领域技术人员,在不脱离本技术的精神和范围内,均可作各种更动与修改,因此本技术的保护范围应当以权利要求所限定的范围为准。当前第1页12当前第1页12

再多了解一些

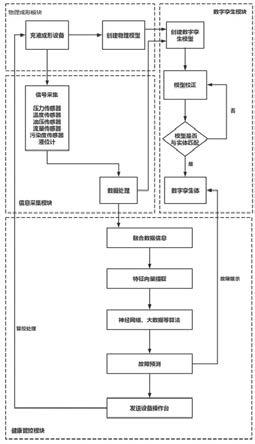

本文用于企业家、创业者技术爱好者查询,结果仅供参考。