1.本说明书涉及用于执行数学计算的硬件电路。

背景技术:

2.计算电路能够包括具有硬件乘法器的乘法电路,这些硬件乘法器用于将诸如整数和浮点数的数字输入相乘。获取乘法电路并将其集成到现有的计算电路中能够是昂贵的,并且一些电路的尺寸不适用于某些应用。例如,一些乘法电路能够包括带符号乘法器和无符号乘法器两者,它们消耗电路管芯的相当大的面积,但是尽管它们的尺寸很大,在计算吞吐量方面却没有优势。对于某些计算应用来说,过大的乘法器电路会导致功耗和利用率的低效。

3.硬件电路能够用来实现神经网络。特别地,具有多层的神经网络能够在包括若干硬件乘法器的计算电路上实现。硬件电路的计算电路也能够表示用于执行给定层的神经网络计算的计算单元。例如,给定输入,电路能够通过使用硬件电路的计算单元中的一个或多个乘法器执行点积运算,来使用神经网络计算输入的推断。

技术实现要素:

4.本文档描述了一种用于将输入相乘的专用硬件电路。硬件电路包括接收输入的处理电路,每个输入具有相应位宽。处理电路能够基于具有超过硬件电路的固定位宽的位宽的第一输入,将至少一个输入表示为带符号多字输入。硬件电路被配置为带符号多字乘法器,并且包括每个被配置为将带符号输入相乘的带符号乘法器。每个带符号乘法器包括乘法电路,所述乘法电路被配置为:接收带符号多字输入;接收带符号第二输入;以及响应于带符号多字输入与带符号第二输入相乘而生成带符号输出。

5.本说明书中描述的主题的一个方面能够体现在用于将输入集相乘的硬件电路中。所述硬件电路包括:处理电路,接收第一输入和第二输入,第一输入和第二输入中的每一个具有相应位宽,其中,所述处理电路被配置为基于具有超过硬件电路的固定位宽的位宽的第一输入,将至少第一输入表示为带符号多字输入;以及多个带符号乘法器,多个带符号乘法器中的每个带符号乘法器被配置为将两个或更多个带符号输入相乘,每个带符号乘法器包括乘法电路,所述乘法电路被配置为:接收表示第一输入的带符号多字输入;接收与第二输入相对应的带符号第二输入;并且响应于带符号多字输入与带符号第二输入相乘而生成带符号输出。

6.这些和其他实现能够各自可选地包括一个或多个以下特征。例如,在一些实现中,带符号多字输入是包括n个字的移位的带符号数,每个n个字包括b个位;并且n是大于1的整数,b是大于1的整数。在一些实现中,移位的带符号数的数值是基于a0 a1*2b a2*2

(2b)

…

a{n-1}*2

{(n-1)b}

定义的,其中,a表示带符号多字输入的相应带符号字。在一些实现中,移位的带符号数的可表示的数值范围是基于[-2

(n*b-1)-s,2

(n*b-1)-1-s]定义的。在一些实现中,s是基于2

(b-1)

*(1 2b

…

2

{(n-2)b}

)定义的。在一些实现中,处理电路被配置为将第一输入表示为

带符号多字输入,所述带符号多字输入包括:带符号高字部分;以及带符号低字部分。

[0007]

在一些实现中,将第一输入表示为带符号多字输入包括:基于硬件电路的固定位宽,使用量化方案来修改第一输入的数据格式。在一些实现中,量化方案被配置为通过生成相应字部分来修改第一输入的数据格式,以将第一输入表示为带符号多字输入;并且包括每个相应字部分的总位宽等于硬件电路的固定位宽。在一些实现中,带符号多字输入包括多个相应字;并且乘法电路被配置为通过将带符号多字输入的每个字与带符号第二输入的每个字相乘来生成带符号输出。在一些实现中,带符号第二输入包括多个相应带符号字;并且乘法电路被配置为将带符号输出生成为通过将带符号多字输入的每个字与带符号第二输入的每个带符号字相乘而计算出的各个乘积之和。

[0008]

本说明书中描述的主题的一个方面能够体现在一种使用硬件电路来将输入集相乘的方法中。所述方法包括:由硬件电路的处理电路接收第一输入和第二输入,第一输入和第二输入中的每一个具有相应位宽,其中,至少第一输入具有超过在硬件电路中包括的乘法硬件的固定位宽的位宽,乘法硬件用于将第一输入和第二输入相乘;从至少第一输入生成包括多个带符号字的带符号多字输入,每个带符号字具有多个位,其中,带符号多字输入的位宽小于乘法硬件的固定位宽;向乘法硬件提供带符号多字输入和带符号第二输入用于相乘,其中,带符号第二输入与第二输入相对应并且具有在乘法硬件的固定位宽内的位宽;以及至少使用第一输入和第二输入从乘法硬件生成带符号输出。

[0009]

这些和其他实现能够各自可选地包括一个或多个以下特征。例如,在一些实现中,带符号多字输入是包括n个字的移位的带符号数,每个n个字包括b个位;并且n是大于1的整数,b是大于1的整数。在一些实现中,移位的带符号数的数值是基于a0 a1*2b a2*2

(2b)

…

a{n-1}*2

{(n-1)b}

定义的,其中,a表示带符号多字输入的相应带符号字。在一些实现中,移位的带符号数的可表示的数值范围是基于[-2

(n*b-1)-s,2

(n*b-1)-1-s]定义的。在一些实现中,s是基于2

(b-1)

*(1 2b

…

2

{(n-2)b}

定义的。在一些实现中,生成带符号多字输入包括将第一输入表示为带符号多字输入,所述带符号多字输入包括:带符号高字部分;和带符号低字部分。

[0010]

在一些实现中,将第一输入表示为带符号多字输入包括:基于硬件电路的固定位宽,使用量化方案来修改第一输入的数据格式。在一些实现中,所述方法还包括:基于量化方案,通过生成相应字部分来修改第一输入的数据格式,以将第一输入表示为带符号多字输入,其中,包括每个相应字部分的总位宽等于硬件电路的固定位宽。在一些实现中,带符号第二输入包括多个相应字;并且所述方法还包括:使用乘法硬件的带符号乘法器,将带符号输出生成为带符号多字输入的每个字与带符号第二输入的每个字相乘的相应乘积之和。

[0011]

该方面和其他方面的其他实现包括对应的系统、装置和计算机程序,被配置为执行在计算机存储设备(例如,非暂时性机器可读存储介质)上编码的方法的动作。一个或多个计算机或硬件电路的计算系统能够通过安装在系统上的软件、固件、硬件或它们的组合来配置,这些软件、固件、硬件或它们的组合在操作中使系统执行动作。一个或多个计算机程序能够通过具有以下指令来配置,当由数据处理设备执行时,所述指令使得所述设备执行动作。

[0012]

本说明书中描述的主题能够在特定实施例中实现,以达成一个或多个以下优点。所描述的技术能够用于实现专用硬件电路,用于将两个或更多个输入相乘,同时比用于将输入相乘的传统电路需要更少的功率。本文档中描述的硬件电路的组件形成具有带符号乘

法器的带符号多字乘法器电路,所述带符号乘法器被配置为将带符号输入相乘以生成带符号输出。多字乘法器能够是低功率硬件乘法电路,其基于用于表示带符号数的唯一数字格式来有效地将几个输入(例如,浮点输入)相乘。

[0013]

乘法电路能够被配置为具有乘法硬件,所述乘法硬件仅包括用于执行输入相乘的带符号硬件乘法器。所述电路包括处理电路,用于响应于具有诸如二进制补码格式的传统编号格式的处理输入,生成移位的带符号多字数。带符号多字数通过带符号硬件乘法器相乘,以生成带符号输出。与传统的将输入相乘的电路相比,乘法电路的这些特性降低了电路的功耗。这是因为乘法只使用带符号乘法器来完成,而不是使用带符号乘法器和无符号乘法器两者。此外,包括用于支持多种模式(例如,带符号和无符号模式)的硬件乘法器的电路也增加了电路消耗的芯片面积,从而增加了电路的制造成本。因此,所提出的技术不仅降低了功耗,还降低了制造成本。

[0014]

当电路的乘法硬件被配置为仅包括带符号硬件乘法器时,整个硬件电路比必须包括额外乘法硬件以支持带符号和无符号计算模式的传统电路消耗更少的功率。因此,这种低功耗硬件乘法器电路能够被优化,以基于影响仅带符号模式来生成将两个或更多个带符号多字输入相乘的乘积的至少带符号乘法器配置,将数字输入相乘,同时降低功耗要求。

[0015]

本说明书中描述的主题的一个或多个实现的细节在附图和以下描述中阐述。根据描述、附图和权利要求,本主题的其他潜在特征、方面和优点将变得显而易见。

附图说明

[0016]

图1示出用于将输入相乘的示例专用硬件电路的图。

[0017]

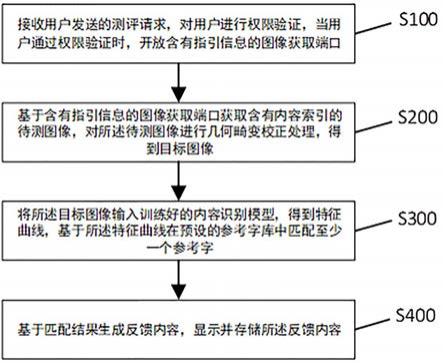

图2示出用于生成带符号多字输入的流程图,带符号多字输入被提供给带符号硬件乘法器以生成带符号输出。

[0018]

图3示出用于在描述的硬件乘法器电路中将输入相乘的示例过程的流程图。

[0019]

不同附图中相同的附图标记和名称表示相同的元件。

具体实施方式

[0020]

传统的计算机体系架构以固定的位宽b提供乘法硬件。当这些体系架构需要将位数超过位宽的输入相乘时,这些体系架构将输入数分成多个片段(“字”),其中,每个字具都有长度或位宽b。为了产生计算输出,这些体系架构将第一个输入的每个字与第二个输入的每个字相乘。然而,为了产生带符号(例如,正、负或零)输出,体系架构必须在带符号模式和无符号模式(例如,其中,输入仅为正或零)二者中可配置。必须在带符号模式和无符号模式二者中可配置的传统电路需要额外的硬件组件,这会导致功耗增加。

[0021]

在示例实现中,硬件电路能够用于实现多层神经网络,并通过处理通过神经网络的每一层的输入来执行计算(例如,神经网络计算)。具体而言,神经网络的各个层能够各自具有相应参数集。每层接收输入,并根据该层的参数集处理输入,以基于使用示例计算单元的乘法电路执行的计算来生成输出。例如,当执行输入阵列和参数阵列的矩阵乘法或者作为计算输入阵列和参数核阵列之间的卷积的一部分时,神经网络层计算多个乘积。

[0022]

一般来说,通过神经网络的层处理输入是使用用于执行数学运算——例如乘法和加法——的电路来完成的。示例硬件电路能够包括用于将两个或更多输入相乘的硬件乘法

器。乘法器电路能够与硬件加法器一起分组,以形成硬件电路的计算单元,例如矩阵或矢量处理单元。计算单元用于将诸如整数和浮点数的数字输入相加和相乘。例如,当硬件电路用于执行神经网络计算时,发生加法和乘法,诸如用于处理通过神经网络的层的输入的矩阵-向量乘法。

[0023]

考虑到以上情境,本文档描述了用于实现专用硬件电路的技术,该专用硬件电路用于将表示为带符号多字输入的两个或更多个输入相乘。这些技术能够用于将带符号或无符号输入表示为“移位的带符号多字数(multiword number)”。这些移位的带符号多字数使用唯一的数字格式将接收到的输入表示为带符号数。接收到的输入能够是多字数的单个字,也能够包括单字输入和多字输入。通过将输入表示为带符号数,专用硬件电路不需要支持无符号模式。因此,所描述的硬件电路使用更精简的体系架构,该体系架构包括用于带符号模式操作而不是用于带符号和无符号模式二者的操作的乘法电路。因为所描述的硬件电路被配置为仅用于带符号模式操作,所以该电路需要更少的组件,当与传统架构相比时,这转化为提高的功率效率。

[0024]

图1示出了用于将输入102相乘的示例专用硬件电路100的图。在示例实现中,输入102a(“输入a”)和102b(“输入b”)是相应的浮点数或二进制补码数,它们能够使用二进制数据结构在软件中表示。二进制数据结构能够具有特定的位数,例如16位、24位或32位数据结构。例如,输入a或b中的每一个可以是相应的带符号浮点数,并且每个输入的符号位(或多个)可以指示该输入的符号(例如,正或负)。

[0025]

每个数字输入的数据结构能够与特定的数据格式相关联。数据格式可以指示能够使用数据格式表示的有限范围的数值。在一些实现中,输入a的16位数据结构能够包括表示输入a的二进制补码数据格式的二进制输入(例如,0010)。关于数字范围,普通的二进制补码数能够具有以下的有限可表示范围的数值:[-32,768,32,767]。此外,每个数字输入在其数据结构中具有一个或多个位,指示该数是带符号数还是无符号数。

[0026]

如本文档所述,表示带符号数字输入(例如,整数)的数据结构可以保存正数值(例如,整数值)和负数值,而表示无符号数字输入的数据结构可以保存更大范围的正数值而没有负数值。一般来说,处理器电路,诸如gpu或神经网络处理器,通常包括用于执行涉及不同类型输入的计算的算术逻辑单元(alu)或计算单元,例如整数或浮点输入。

[0027]

涉及带符号输入的计算与带符号模式操作相对应,而涉及无符号输入的计算与无符号模式操作相对应。用于执行涉及带符号和无符号数字输入的计算的alu和计算单元需要不同的硬件组件集来支持各自的带符号模式和无符号模式操作。例如,如上所述,一些计算机体系架构提供固定位宽b的乘法硬件。当这些体系架构需要将具有超过位宽的位数的输入相乘时,该体系架构将输入数分成多个片段(“字”),其中,每个字具有长度或位宽b。为了产生计算输出,该体系架构将第一输入的每个字与第二输入的每个字相乘。

[0028]

但是,如前所述,为了产生带符号(例如,正、负或零)输出,体系架构必须在带符号模式和无符号模式(例如,其中输入仅是正的)下都是可配置的。必须针对带符号和无符号操作二者可配置的体系结构需要额外的硬件组件,这会导致功耗增加。在此情境下,描述了用于实现专用硬件电路100的技术,该专用硬件电路100被配置为对具有唯一数据格式的带符号输入进行乘法运算,同时相对于传统硬件电路消耗更少的功率。专用电路100包括仅支持带符号模式操作的乘法电路。当输入仅表示为带符号数时,该电路实现一定的功耗节省。

例如,通过仅将带符号输入相乘来生成计算输出,电路100能够包括更少的硬件组件和更小的指令集,该指令集具有减少数量的软件指令来将输入相乘。

[0029]

电路100包括输入处理器104,其被配置成生成带符号多字输入。硬件电路100的一部分能够包括具有乘法电路的计算单元103,乘法电路提供用于将输入102相乘的硬件乘法器。输入处理器104能够被配置为基于电路100的计算单元103中的乘法电路的固定位宽来生成带符号多字输入。更具体地,输入处理器104被配置为从输入102生成移位的带符号多字数。例如,输入处理器104能够生成移位的带符号多字数106和108。移位的带符号多字数106能够包括相应的带符号字输入c和d,它们各自从输入a生成,而移位的带符号多字数108能够包括相应的带符号字输入e和f,它们各自从输入b生成。

[0030]

硬件电路100包括带符号硬件乘法器110和112。在一些实现中,电路100被配置为包括低功率带符号整数或浮点乘法电路。在一些示例中,乘法器110、112能够经由可选连接113连接,以形成硬件电路100的单个、大规模带符号乘法电路。在一些其他示例中,乘法器110和112能够表示较大乘法电路114的不同硬件乘法器,并且电路100能够包括一个或多个乘法电路114。虽然在图1的示例中示出了两个乘法器,但是电路100(或电路114)能够被配置为包括更多或更少的乘法器。例如,电路100能够包括单个乘法器,该乘法器被配置为随着时间的推移用于多个目的,以实现与多个单独的乘法器相同(或相似)的计算效果。以这种方式,电路100能够被优化,用于通过例如仅包括带符号乘法器或仅支持带符号模式操作所需的其他硬件组件来将某些数字输入相乘,并具有降低的功率需求。在一些情况下,专用硬件电路100使用乘法电路来执行通过神经网络层处理输入的计算。计算能够包括输入和参数的相乘,以生成累加值,该累加值被进一步处理以生成神经网络层的层输出。

[0031]

在示例操作中,给定输入集,该输入集包括相应的带符号字输入c和d(各自从输入a生成)和相应的带符号字输入e和f(各自从输入b生成),电路100被配置为将输入c和e相乘(c*e),将输入c和f相乘(c*f),将输入d和e相乘(d*e),以及将输入d和f相乘(d*f)。计算单元103包括加法器电路120(“加法器120”),其被配置为在乘法电路114的一个或多个乘法器110、112生成的乘积之间执行适当的加法运算。计算单元103被配置为在将一个或多个乘积值移位必要的位宽之后执行加法运算。例如,计算单元103能够在执行以下加法运算(c*e《《(2*b)) ((c*f d*e)《《b) d*f之前,使用加法器120来执行移位操作(例如,《《2*b、《《b等)。

[0032]

加法器120接收带符号乘积116和118作为输入,并将带符号乘积116和118相加,以生成计算单元103的带符号输出122。在一些实现中,负的带符号乘积118的二进制补码版本用于执行加法运算,该加法运算包括将带符号乘积116与带符号乘积118的二进制补码版本相加,以生成带符号输出122。在一些情况下,将输入相加能够包括在生成带符号输出122之前使用四舍五入逻辑对初步总和执行四舍五入操作。例如,四舍五入逻辑能够用于在生成带符号输出122之前将初步总和四舍五入到最接近的十进制或整数值。在一些实现中,带符号输出122表示用于响应于通过神经网络层处理数值输入102而生成神经网络层的层输出的累积值。

[0033]

图2示出用于生成带符号多字输入的过程图200,带符号多字输入被提供给电路100的带符号硬件乘法器以生成带符号输出122。如下文更详细描述的,过程图200包括多个逻辑块,每个逻辑块表示输入处理器104的相应逻辑功能。一般来说,一个或多个相应的逻辑功能可以用于生成移位的带符号多字数。

[0034]

参考过程图200,硬件电路100被配置为带符号模式电路,并且包括用于生成带符号多字数字106的输入处理电路104。输入处理器104至少基于确定输入具有超过在硬件电路中包括的硬件乘法器的固定位宽的位宽,从输入102生成移位的带符号多字数(204)。例如,输入处理器104能够分析输入102的二进制数据结构,以确定每个相应的输入是否超过在计算单元103中包括的乘法电路114的固定位宽。

[0035]

生成带符号多字数106包括基于输入处理器104确定输入102在用于表示移位的带符号多字数106的数据格式的预定数值范围内来生成数106(206)。例如,输入处理器104响应于确定输入102的数值,例如二进制补码数,适合于表示移位的带符号多字数106的数据格式的可用数值范围,生成带符号多字数106。对于给定的输入102,如果输入处理器104确定输入102的数值不适合数据格式的可用数值范围,则输入处理器104结束过程200(208)。

[0036]

如果输入处理器104确定输入102在数据格式的预定数值范围内,则输入处理器204至少基于具有超过硬件电路100的固定位宽的位宽的第一输入,使得一个或多个输入被表示为相应的带符号多字输入。例如,为了将输入表示为带符号多字输入,输入处理器104生成相应的带符号n个字,每个字具有b个位(210)。输入处理器104然后使用每个都具有b个位的每个带符号n个字来生成移位的带符号数(212)。在一些实现中,n是大于1的整数,并且b是大于1的整数。带符号多字输入被提供给乘法电路114的带符号硬件乘法器,以最终产生带符号输出。

[0037]

在一些情况下,输入处理器104确定输入102的位宽不超过在硬件电路中包括的硬件乘法器110的固定位宽(205)。在这种情景下,输入处理器104将输入214提供给乘法电路114的带符号乘法器。例如,输入处理器104能够基于输入的符号与特定硬件乘法器的符号相匹配,向特定硬件乘法器提供输入214。在该实现中,因为输入214的位宽不大于乘法电路114的固定位宽,所以输入214不是用于生成带符号多字输入的合适输入。

[0038]

对于示例乘法运算,确定是否从输入102生成移位的带符号多字数,以及随后生成带符号多字输入,能够在计算周期中相对较早地发生。例如,能够使用与电路100通信的外部主机控制器进行片外确定,以获得用于通过神经网络层来处理的输入。在一些实现中,当从示例神经网络处理器的存储器获得输入时,确定和随后的生成发生,所述示例神经网络处理器诸如存储由在包括硬件电路100的神经网络处理器上实现的神经网络层生成的激活的激活存储器。

[0039]

在其他实现中,确定是否生成带符号多字输入以及随后生成带符号多字输入能够发生在先前的流水线阶段,例如在计算单元103的前一乘法器、alu或旁路电路处。在一些情况下,每个带符号硬件乘法器110、112的接口能够被修改或扩充以包括相应的输入处理器104。在这种情况下,在每个乘法器110、112的输入处接收的输入102能够被处理,以生成适当数量的移位多字输入,用于在相应的硬件乘法器110、112处相乘。

[0040]

图3示出了使用所描述的硬件乘法器电路100来将输入相乘的示例过程300的流程图。如上所述,输入能够是数字输入,诸如被表示为位的数据结构的浮点数,例如16位或32位。能够结合本文中描述的其他电路、组件和系统、使用至少电路100来执行过程300。

[0041]

现在参考过程300,电路100接收第一输入和第二输入,第一输入和第二输入中的每个具有相应位宽(302)。处理电路被配置为基于第一输入具有超过硬件电路的固定位宽的位宽,将至少第一输入表示为带符号多字输入。例如,硬件电路的固定位宽能够是16位,

而第一输入的示例数据结构的位宽是32位。

[0042]

电路100至少从第一输入生成带符号多字输入,其包括多个带符号字,每个带符号字具有多个位(304)。带符号多字输入/数是包括n个字的移位的带符号数,每个n个字包括b个位。一般来说,n能够是大于1的整数,并且b能够是大于1的整数。例如,响应于分析第一输入的数据结构,输入处理器104能够确定第一输入由32位组成。输入处理器104能够确定或计算第一输入中的位数和硬件电路的固定位宽的位数之间的差。

[0043]

输入处理器104能够基于计算的差来生成带符号多字数。在一些实现中,使用形成第一输入102的32位数据结构的一部分位来生成带符号多字数的每个字。例如,带符号多字数可以由四个8位数或两个16位数组成。这些数能够与上述带符号多字数106和108相对应。在一些情况下,带符号多字数的每个字是带符号字,其包括来自第一输入的一部分位和表示形成带符号多字数的带符号字的符号的相应符号位。

[0044]

在一些实现中,当移位的带符号多字数由四个8位数形成时,该移位的带符号数包括n=4个字,其中n个字中的每个包括b=8个位。这个“移位的带符号n字b位数”由n个普通的带符号数表示,每个带符号数的位宽为b。举例来说,令a0,a1,...,a{n-1}是那些普通的带符号数,并且令a是每个数共同表示的移位的带符号数。移位的带符号数的数值u被定义为:a=a0 a1*2b a2*2

(2b)

…

a{n-1}*2

{(n-1)b}

,其中,a表示带符号多字输入的相应带符号字。单个字a0,a1,...,a{n-1}每个是带符号数。在一些其他实现中,原始输入数被零扩展(例如,在最高有效端添加“0”位)或符号扩展(例如,原始输入数的最高有效位被复制到多余位),直到位宽是b的倍数为止。

[0045]

如上所述,数据格式可以具有有限范围的数值,这些数值能够使用该数据格式来表示。在一些实现中,移位的带符号多字数具有可表示的数值范围,该数值范围是基于用于表示普通二进制补码数的数值范围的示例已知表达式来定义的,但是该数值范围包括附加参数s。移位的带符号多字数的数值范围使用[-2

(n*b-1)-s,2

(n*b-1)-1-s]来获得。参数s向已知表达式引入一个移位函数,用于表示二进制补码数的数值范围。例如,当b=8并且n=2时,普通二进制补码数的可表示范围为:[-32,768,32,767]。普通二进制补码数的这个范围是用已知的表达式[-2

(n*b-1)

,2

(n*b-1)-1]得到的。关于本文档中描述的唯一数据格式,参数s用于将已知表达式相对于普通n字*b位的二进制补码可表示范围向左(例如,朝向负无穷大)移动距离s。在一些实现中,s和相应的移位是基于2

(b-1)

*(1 2b ... 2

{(n-2)b}

)定义的。

[0046]

在一些实现中,硬件电路100和输入处理器104使用量化方案来基于硬件电路的固定位宽修改第一输入的数据格式。量化方案被配置为通过生成相应的字部分来修改第一输入的数据格式,以将第一输入表示为带符号多字输入。例如,可以基于特定的量化方案来修改用于从神经网络层的参数或核权重值生成带符号多字数的数据格式,从而能够适当地使用这些参数来计算层的输出。对于生成的带符号多字输入,包括每个相应字部分的总位宽能够等于硬件电路的固定位宽。在一些实现中,输入处理器104被配置为调整某些软件方案,以重新量化或改变在电路100处获得和处理参数和权重的方式。

[0047]

电路100向乘法硬件提供带符号多字输入和带符号第二输入用于相乘(306)。带符号第二输入与接收的第二输入相对应。在一些实现中,第二输入能够与不超过硬件电路的位宽的带符号输入或另一个移位的带符号多字数相对应。在一些其他实现中,第二输入与超过硬件电路的位宽的带符号输入相对应,使得电路100从第二输入生成带符号多字数。

[0048]

电路100至少使用第一输入和第二输入从乘法硬件生成带符号乘积(308)。例如,电路100响应于将第一输入的移位带符号多字数与第二输入的移位带符号多字数相乘,生成带符号乘积116或118。这些移位的带符号多字输入包括多个相应的字,并且乘法电路114被配置为通过将带符号多字第一输入的每个字与带符号多字第二输入的每个字相乘来生成带符号乘积。移位带符号多字数的一个优点是,它们能够相乘,而不需要无符号硬件乘法器。例如,为了计算两个这样的数字a和b的带符号乘积116:

[0049]

a=a0 a1*2b a2*2

(2b)

... a{n-1}*2

{(n-1)b}

[0050]

b=b0 b1*2b b2*2

(2b)

…

b{n-1}*2

{(n-1)b}

[0051]

硬件电路100计算ai*bj的乘积,这些乘积都能够使用电路100的带符号硬件乘法器来计算。

[0052]

已经描述了许多实施例。然而,应当理解,在不脱离本发明的范围的情况下,可以进行各种修改。例如,可以使用上面所示的各种形式的流程,其中步骤被重新排序、添加或移除。因此,其他实施例在以下权利要求的范围内。虽然本说明书包含许多具体的实施细节,但是这些不应被解释为对所要求保护的范围的限制,而是对特定实施例特有的特征的描述。本说明书中在单独实施例的上下文中描述的某些特征也能够在单个实施例中组合实现。

[0053]

相反,在单个实施例的上下文中描述的各种特征也能够在多个实施例中单独实现或者在任何合适的子组合中实现。此外,尽管特征可以在上面被描述为在某些组合中起作用,并且甚至最初被这样要求保护,但是在一些情况下,来自所要求保护的组合的一个或多个特征能够从该组合中删除,并且所要求保护的组合可以指向子组合或子组合的变体。

[0054]

类似地,虽然在附图中以特定顺序描述了操作,但是这不应该被理解为要求以所示的特定顺序或顺序执行这些操作,或者要求执行所有示出的操作,以获得期望的结果。在某些情况下,多任务和并行处理可能是有利的。此外,上述实施例中的各种系统模块和组件的分离不应该被理解为在所有实施例中都需要这种分离,并且应该理解,所描述的程序组件和系统通常能够集成在单个软件产品中或者封装到多个软件产品中。

[0055]

已经描述了主题的特定实施例。其他实施例在以下权利要求的范围内。例如,权利要求中列举的动作能够以不同的顺序执行,并且仍然获得期望的结果。作为一个示例,附图中描述的过程不一定需要所示的特定顺序或顺序来实现期望的结果。在某些情况下,多任务和并行处理可能是有利的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。