1.本公开大体上涉及半导体存储器和方法,且更确切地说,涉及分级存储器设备。

背景技术:

2.通常将存储器装置提供为计算机或其它电子系统中的内部半导体集成电路。存在许多不同类型的存储器,包括易失性及非易失性存储器。易失性存储器可能需要电力以维持其数据(例如,主机数据、错误数据等),且包括随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)和同步动态随机存取存储器(sdram)等等。非易失性存储器可通过在未供电时保留所存储的数据来提供持久数据,且可包括nand快闪存储器、nor快闪存储器和电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)和磁阻随机存取存储器(mram),例如自旋力矩转移随机存取存储器(stt ram)等等。

3.存储器装置可耦合到主机(例如主机计算装置)以存储数据、命令和/或指令以在操作计算机或电子系统时供主机使用。举例来说,数据、命令和/或指令可在计算或其它电子系统的操作期间在主机与一或多个存储器装置之间传递。

附图说明

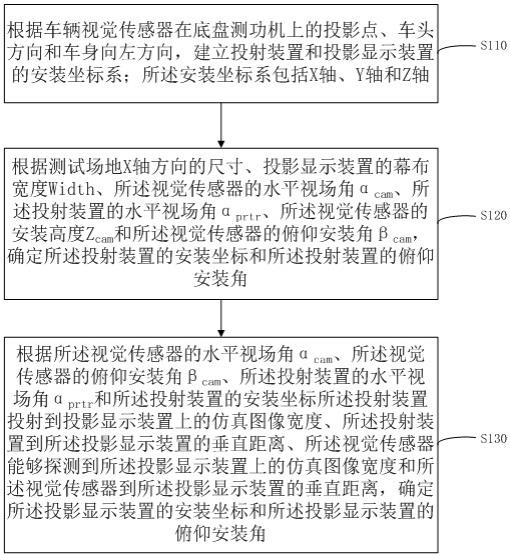

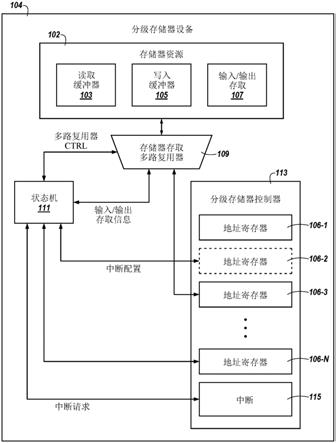

4.图1为根据本公开的数个实施例的分级存储器设备的功能框图。

5.图2为根据本公开的数个实施例的分级存储器设备的功能框图。

6.图3为根据本公开的数个实施例的呈包括分级存储器设备的计算系统形式的功能框图。

7.图4为根据本公开的数个实施例的呈包括分级存储器设备的计算系统形式的另一功能框图。

8.图5为表示根据本公开的数个实施例的分级存储器设备的实例方法的流程图。

9.图6为表示根据本公开的数个实施例的分级存储器设备的实例方法的另一流程图。

具体实施方式

10.本文中描述一种分级存储器设备。实例设备可包括状态机,其与分级存储器设备通信且配置成将存取数据和控制消息传递到多路复用器和/或从多路复用器接收存取数据。另外,状态机可包括逻辑电路系统,其配置成将中断请求消息传递到分级存储器控制器和从分级存储器控制器接收中断请求消息。分级存储器设备可为分级存储器系统的部分,所述分级存储器系统可利用持久存储器以存储通常存储在非持久存储器中的数据。逻辑电路系统可配置成确定存取持久存储器装置的请求对应于将数据从非持久存储器装置分流到持久存储器装置的操作,产生中断信号以及致使中断信号将在可耦合到逻辑电路系统的主机上断言,作为将数据从非持久存储器装置分流到持久存储器装置操作的部分。

11.计算系统在操作期间利用各种类型的存储器资源。举例来说,计算机系统可在操作期间利用易失性(例如随机存取存储器)存储器资源和非易失性(例如存储)存储器资源的组合。大体而言,易失存储器资源可在比非易失性存储器资源快得多的速度下操作,且可具有比非易失性存储器资源更长的生命期;然而,易失存储器资源通常比非易失性存储器资源更昂贵。如本文中所使用,易失性存储器资源可在替代方案中称为“非持久存储器装置”,而非易失性存储器资源可在替代方案中称为“持久存储器装置”。

12.然而,持久存储器装置可更广泛地指代以持久方式存取数据的能力。作为实例,在持久存储器情境中,存储器装置可将多个逻辑到物理映射或翻译数据和/或查找表存储在存储器阵列中以便跟踪存储器装置中的数据位置,而与存储器是否为非易失性的无关。此外,持久存储器装置可指代存储器的非易失性,还有通过包括服务于用于连续过程的命令(例如,通过使用逻辑到物理映射、查找表等)的能力来使用所述非易失性。

13.这些特性可需要计算系统中的权衡,以便提供具有充分资源以根据消耗者和计算资源提供者的不断增大需求起作用的计算机系统。举例来说,在多用户计算网络(例如基于云的计算机系统部署、软件定义的数据中心等)中,可提供相对大量的易失存储器以提供在多用户网络中运行的虚拟机。然而,通过依赖于易失存储器以将存储器资源提供到多用户网络,如在一些方法中为常见的,与为网络提供存储器资源相关联的成本可增加,尤其是当网络的用户需要越来越大的计算资源池可供使用时。

14.此外,在依赖于易失存储器以提供存储器资源以在多用户网络中提供虚拟机的方法中,一旦易失存储器资源耗尽(例如,一旦易失存储器资源分配给多用户网络的用户),那么可不将额外用户添加到多用户网络,直到额外易失存储器资源可供使用或添加为止。这可导致潜在用户离开,此可产生如果额外存储器资源可用于多用户网络,那么可产生的收入的损耗。

15.易失存储器资源(例如动态随机存取存储器(dram)倾向于以确定性方式操作),而非易失性存储器资源(例如存储类别存储器(例如nand快闪存储器装置、固态驱动器、电阻可变存储器装置等))倾向于以非确定性方式操作。举例来说,由于对从存储类别存储器装置检索的数据执行的错误校正操作、加密操作、raid操作,从存储类别存储器装置请求数据与可用的数据之间的时间量可在读取到读取之间变化,由此使得从存储类别存储器装置的数据检索具有非确定性。相反,从dram装置请求数据与可用的数据之间的时间量可在读取到读取之间保持固定,由此使得从dram装置的数据检索具有确定性。

16.另外,由于易失存储器资源的确定性的行为与非易失性存储器资源的非确定性行为之间的区别,传递进出存储器资源的数据通常穿越与所使用的存储器的类型相关联的特定接口(例如总线)。举例来说,传递到dram装置和从dram装置传递的数据通常经由双数据速率(ddr)总线传送,而传递到nand装置和从nand装置传递的数据通常经由外围组件互连高速(pci-e)总线传送。如将了解,然而,数据可经由其传递进出易失存储器资源和非易失性存储器资源的接口的实例不限于这些列举实例。

17.由于非易失性存储器装置和易失性存储器装置的不同行为,一些方法选择将某些类型的数据存储在易失性或非易失性存储器中。相较于非易失性存储器装置的非确定性行为,这可减轻可能由于例如易失性存储器装置的确定性行为而产生的问题。举例来说,计算系统在一些方法中存储在计算机系统在易失性存储器装置中的操作期间有规律地存取的

少量数据,而更大或更不频繁地存取的数据存储在非易失性存储器装置中。然而,在多用户网络部署中,绝大部分数据可存储在易失性存储器装置中。相反,本文中的实施例可允许从部署在多用户网络中的非易失性存储器装置进行数据存储和检索。

18.如本文中所描述,本公开的一些实施例针对计算系统,其中来自非易失性且因此非确定性存储器资源的数据经由局限于在其它方法中由易失性和确定性存储器资源使用的接口传送。举例来说,在一些实施例中,可经由例如ddr接口的接口将数据传递进出非易失性非确定性存储器资源,所述非易失性非确定性存储器资源例如nand快闪装置、电阻可变存储器装置,例如相变存储器装置和/或电阻式存储器装置(例如三维交叉点(3d xp)存储器装置)、固态驱动器(ssd)、自选存储器(ssm)装置等,所述ddr接口在一些方法中保留以用于将数据传递进出易失性确定性存储器资源。因此,与使用易失性确定性存储器装置以将主存储器提供到计算机系统的方法相比,本文中的实施例可允许非易失性非确定性存储器装置用作用于计算机系统的主存储器的至少一部分。

19.在一些实施例中,数据可在中间从非易失性存储器资源传递到高速缓存(例如较小静态随机存取存储器(sram)高速缓存)或缓冲器且随后使得可用于请求数据的应用程序。通过将一般以确定性方式提供的数据存储在非确定性存储器资源中,且允许存取如在此所描述的数据,与使用易失性存储器资源操作的方法相比,可通过例如允许以大体上减小的成本使得较大量的存储器资源可用于多用户网络来改良计算机系统效能。

20.为了促进本公开的实施例,可使对非易失性存储器资源的可见度对于其中部署分级存储器设备的计算系统的各种装置是模糊的。举例来说,部署在计算系统或多用户网络中的主机、网络接口卡、虚拟机等可能不能够区分数据由计算系统的易失性存储器资源还是非易失性存储器资源存储。举例来说,硬件电路系统可部署在计算系统中,其可寄存对应于数据的地址,这一方式使得主机、网络接口卡、虚拟机等不能够区分数据由易失性还是非易失性存储器资源存储。

21.如本文中更详细描述,分级存储器设备可包括状态机的硬件电路系统(例如逻辑电路系统),其可接收重导向数据请求,在与所请求数据相关联的逻辑电路系统中寄存地址(即使电路系统未由其自身的存储器资源备份以存储数据),且使用逻辑电路系统将寄存在逻辑电路系统中的地址映射到对应于非易失性存储器装置中的数据的物理地址。状态机可耦合到有助于状态机执行上述操作的多路复用器。

22.在本公开的以下详细描述中,参考形成本公开的部分的附图,且其中通过说明的方式展示可如何实践本公开的一或多个实施例。足够详细地描述了这些实施例以使本领域的一般技术人员能够实践本公开的实施例,且应当理解,可以利用其它实施例,且可以在不脱离本公开的范围的情况下进行过程、电和结构性改变。

23.如本文中所使用,例如“n”、“m”等特定地相对于图式中的参考标号的指定符指示可包括数个如此指定的特定特征。还应理解,本文中所使用的术语仅仅是出于描述特定实施例的目的且并不意图为限制性的。如本文所使用,除非上下文另外明确规定,否则单数形式“一(a/an)”以及“所述”可包括单数和复数指示物两者。另外,“数个”、“至少一个”和“一或多个”可指这种事物中的一或多个(例如,数个存储器组可指一或多个存储器组),然而“多个”意图指这种事物中的多于一个。

24.此外,贯穿本技术案在容许意义上(例如,可能、能够)而非在强制性意义上(例如,

必须)使用词语“可(can和may)”。术语“包括”和其派生词指“包括但不限于”。视上下文而定,术语“耦合(coupled/coupling)”意味着物理上直接或间接连接或存取和移动(发射)命令和/或数据。视上下文而定,术语“数据”和“数据值”在本文中可互换地使用且可具有相同含义。

25.本文中的图遵循编号惯例,其中第一数字或多个数字对应于图号,且其余的数字标识图中的元件或组件。可通过使用类似数字来标识不同图之间的类似元件或组件。举例来说,104可在图1中可参考元件“04”,且类似元件可在图2中指代为204。通常在本文中可用单个元件符号指代一组或多个类似元件或组件。举例来说,多个参考元件106-1、106-2、

…

、106-n(例如,106-1到106-n)可通常指代为106。如将了解,可添加、交换和/或去除本文中的各种实施例中所展示的元件,以便提供本公开的数个额外实施例。另外,图式中提供的元件的比例和/或相对尺度意图说明本公开的某些实施例,且不应在限制性意义上看待。

26.图1为根据本公开的数个实施例的分级存储器设备104的功能框图。分级存储器设备104可为计算机系统的部分,如将在本文中进一步描述。如本文中所使用,“设备”可指但不限于各种结构或结构的组合中的任何一种,例如电路或电路系统、一或多个管芯、一或多个模块、一或多个装置或一或多个系统。在一些实施例中,分级存储器设备104可提供为现场可编程门阵列(fpga)、专用集成电路(asic)、数个离散电路组件等,且可在本文中在替代方案中称为“逻辑电路系统”。

27.如图1中所说明,分级存储器设备104可包括存储器资源102,其可包括读取缓冲器103、写入缓冲器105和/或输入/输出(i/o)装置存取组件107。在一些实施例中,存储器资源102可为随机存取存储器资源,例如块ram,其可允许在分级存储器设备104为fpga的实施例中将数据存储在分级存储器设备104内。然而,实施例不限于此,且存储器资源102可包含各种寄存器、高速缓存、存储器阵列、锁存器和sram、dram、eprom,或可存储包括对应于其中数据存储在分级存储器设备104外部的物理位置的所寄存地址的数据(例如,位串)的其它合适的存储器技术。存储器资源102在分级存储器设备104内部且通常小于分级存储器设备104外部的存储器,例如可在分级存储器设备104外部的持久和/或非持久存储器资源。

28.读取缓冲器103可包括存储器资源102的一部分,其被保留以用于存储已由分级存储器设备104接收但尚未由分级存储器设备104处理的数据。举例来说,读取缓冲器可存储已由与对分级存储器设备104外部的存储器(例如持久存储器)执行的感测(例如读取)操作相关联(例如,在所述操作期间和/或作为所述操作的部分)的分级存储器设备104接收的数据。在一些实施例中,读取缓冲器103的大小可为约4千字节(kb),但实施例不限于此特定大小。读取缓冲器103可缓冲将寄存在地址寄存器106-1到106-n中的一个中的数据。

29.写入缓冲器105可包括存储器资源102的一部分,其被保留以用于存储正等待发射到分级存储器设备104外部的位置的数据。举例来说,写入缓冲器可存储将发射到与对外部存储器执行的编程(例如写入)操作相关联的分级存储器设备104外部的存储器(例如持久存储器)的数据。在一些实施例中,写入缓冲器105的大小可为约4千字节(kb),但实施例不限于此特定大小。写入缓冲器103可缓冲将寄存在地址寄存器106-1到106-n中的一个中的数据。

30.i/o存取组件107可包括存储器资源102的一部分,其被保留以用于存储对应于对分级存储器设备104外部的组件(例如,本文中图3和4中所说明的i/o装置310/410)的存取

的数据。i/o存取组件107可存储对应于i/o装置的地址的数据,其可用于从i/o装置读取数据和/或将数据写入到i/o装置。此外,在一些实施例中,i/o存取组件107可接收、存储和/或发射对应于超管理器(例如,图4中所说明的超管理器412)的状态的数据,如本文中结合图4更详细描述。

31.分级存储器设备104可进一步包括存储器存取多路复用器(mux)109、状态机111和/或分级存储器控制器113(或为简单起见“控制器”)。如图1中所展示,分级存储器控制器113可包括多个地址寄存器106-1到106-n和/或中断组件115。存储器存取mux109可包括电路系统,所述电路系统可包含一或多个逻辑门且可配置成控制针对分级存储器设备104的数据和/或地址总线。举例来说,存储器存取mux 109可传递消息进出存储器资源102,以及与分级存储器控制器113和/或状态机111通信,如下文更详细地描述。

32.在一些实施例中,mux 109可将接收到的来自主机(例如主机计算装置、虚拟机等)的传入消息和/或命令重导向到分级存储器设备104。举例来说,mux 109可将对应于来自输入/输出(i/o)装置(例如,本文中图3和4中所说明的i/o装置310/410)的存取(例如读取)或编程(例如写入)请求的传入消息重导向到地址寄存器中的一个(例如,地址寄存器106-n,其可为分级存储器控制器113的bar4区,如下文所描述)到读取缓冲器103和/或写入缓冲器105。

33.此外,mux 109可重导向由分级存储器设备104接收到的请求(例如,读取请求、写入请求)。在一些实施例中,请求可由分级存储器设备104从超管理器(例如,本文中图4中所说明的超管理器412)、裸金属服务器或以通信方式耦合到分级存储器设备104的主机计算装置接收。这些请求可由mux 109从读取缓冲器103、写入缓冲器105和/或i/o存取组件107重导向到地址寄存器(例如,地址寄存器106-2,其可为分级存储器控制器113的bar2区,如下文所描述)。

34.mux 109可将这些请求重导向为操作的部分以确定将存取的地址寄存器106中的地址。在一些实施例中,mux 109可响应于超管理器中断的断言(例如,由中断组件115产生的针对耦合到分级存储器设备104的超管理器断言的中断)将这些请求重导向为操作一部分以确定将存取的地址寄存器中的地址。

35.响应于确定请求对应于与写入到分级存储器设备104(例如,到持久存储器装置,例如本文中图3和4中所说明的持久存储器装置316/416)外部的位置的地址相关联的数据,mux 109可促进数据的检索、数据到写入缓冲器105的传递和/或数据到分级存储器设备104外部的位置的传递。响应于确定请求对应于从分级存储器设备104(例如从持久存储器装置)外部的位置读取的数据,mux 109可促进数据的检索,数据到读取缓冲器103的传递和/或数据或与数据相关联的地址信息到分级存储器设备104内部的位置的传递,例如地址寄存器106。

36.作为非限制性实例,如果分级存储器设备104从i/o装置接收读取请求,那么mux 109可通过选择从分级存储器设备104发送的适当的消息经由超管理器促进数据从持久存储器装置的检索。举例来说,mux 109可促进使用中断组件115产生中断,致使在超管理器上断言中断,将从持久存储器装置接收到的数据缓冲到读取缓冲器103中,和/或以已满足读取请求的指示响应于i/o装置。在分级存储器设备104从i/o装置接收写入请求的非限制性实例中,mux 109可通过选择从分级存储器设备104发送的适当的消息经由超管理器促进数

据到持久存储器装置的传递。举例来说,mux 109可促进使用中断组件115产生中断,致使在超管理器上断言中断,将待传递到持久存储器装置的数据缓冲到写入缓冲器105中,和/或以已满足写入请求的指示响应于i/o装置。本文中将进一步描述分别响应于读取和写入请求的接收的这类检索和数据传递的实例。

37.状态机111可包括配置成对输入执行操作且产生输出的一或多个处理装置、电路组件和/或逻辑。在一些实施例中,状态机111可为有限状态机(fsm)或硬件状态机,其可配置成接收改变的输入且基于接收到的输入产生所得输出。举例来说,状态机111可传递存取信息(例如,“i/o access info”)进出存储器存取多路复用器109,以及中断配置信息(例如,“interrupt config”)和/或中断请求消息(例如,“interrupt request”)进出分级存储器控制器113。在一些实施例中,状态机111可进一步传递控制消息(例如,“mux ctrl”)进出存储器存取多路复用器109。

38.access info消息可包括对应于从分级存储器设备104外部的i/o装置接收到的数据存取请求的信息。在一些实施例中,access info可包括对应于将存储在持久存储器装置中的数据的逻辑寻址信息,或对应于将从持久存储器装置检索的数据的寻址信息。

39.interrupt config消息可由状态机111在分级存储器控制器113上断言以配置适当中断消息以在分级存储器设备104外部断言。举例来说,当分级存储器设备104在耦合到分级存储器设备104的超管理器上断言中断作为满足重导向读取或写入请求的部分时,interrupt config消息可由状态机111产生以基于所述操作是从持久存储器装置检索数据的操作还是将数据写入到持久存储器装置的操作而产生适当的中断消息。

40.interrupt request消息可由状态机111产生且在中断组件115上断言以致使在超管理器(或裸金属服务器或其它计算装置)上断言中断消息。如本文中更详细描述,中断115可在超管理器上断言以致使超管理器对数据检索或数据写入到持久存储器装置区分优先级,作为分级存储器系统的操作的部分。

41.mux ctrl消息可由状态机111产生且在mux 109上断言以控制mux 109的操作。在一些实施例中,mux ctrl消息可由状态机111在mux 109上断言(反之亦然),作为上文所描述的mux 109操作的执行的部分。

42.分级存储器控制器113可包括核心,例如集成电路、芯片、芯片上系统或其组合。在一些实施例中,分级存储器控制器113可为外围组件互连高速(pcie)核心。如本文中所使用,“核心”指代接收指令且基于接收到的指令执行任务或动作的逻辑、处理器和/或协同处理器的可重复使用单元。

43.分级存储器控制器113可包括地址寄存器106-1到106-n和/或中断组件115。地址寄存器106-1到106-n可为基地址寄存器(bar),其可存储由分级存储器设备104或计算系统(例如,本文中图3和4中所说明的计算系统301/401)使用的存储器地址。地址寄存器中的至少一个(例如,地址寄存器106-1)可存储提供从例如图4中所说明的超管理器412的外部位置对分级存储器设备104的内部寄存器的存取的存储器地址。

44.不同地址寄存器(例如,地址寄存器106-2)可用以存储对应于中断控制的地址,如本文中更详细描述。在一些实施例中,地址寄存器106-2可映射直接存储器存取(dma)读取和dma写入控制和/或状态寄存器。举例来说,地址寄存器106-2可包括对应于用于dma命令链的描述符和/或控制位的地址,其可包括产生可向超管理器断言的一或多个中断消息,作

为分级存储器系统的操作的部分,如本文中结合图4所描述。

45.地址寄存器中的又一个(例如,地址寄存器106-3)可存储对应于进出超管理器(例如,本文中图4中所说明的超管理器412)的存取的地址。在一些实施例中,可经由与分级存储器设备104相关联的先进可扩展接口(axi)dma提供进和/或出超管理器的存取。在一些实施例中,地址寄存器可将对应于经由分级存储器设备104的dma(例如axi dma)传递的数据的地址映射到分级存储器设备104外部的位置。

46.在一些实施例中,至少一个地址寄存器(例如地址寄存器106-n)可存储对应于i/o装置(例如图3/4中所说明的i/o装置310/410)存取信息(例如对分级存储器设备104的存取)的地址。地址寄存器106-n可存储由与分级存储器设备104相关联的dma组件绕过的地址。可提供地址寄存器106-n使得映射到其上的地址不由分级存储器设备104的物理存储器位置“备份”。也就是说,在一些实施例中,分级存储器设备104可配置有存储对应于持久存储器装置的地址(例如逻辑地址)和/或存储在持久存储器装置(例如图3/4中所说明的持久存储器装置316/416)中的数据且不由分级存储器设备104存储的数据的地址空间。每一相应地址可对应于持久存储器装置中的不同位置和/或存储在持久存储器装置中的数据的不同部分的位置。举例来说,地址寄存器106-n可配置成可存储对应于物理存储器位置(例如在存储器装置中)的逻辑地址的虚拟地址空间,数据可编程到所述物理存储器位置或将数据存储在所述物理存储器位置中。

47.在一些实施例中,地址寄存器106-n可包括对应于存储器装置(例如,本文中图3和4中所说明的持久存储器装置316/416)的大小的一定数量的地址空间。举例来说,如果存储器装置含有一万亿字节的存储容量,那么地址寄存器106-n可配置成具有可包括一万亿字节的地址空间的地址空间。然而,如上文所描述,地址寄存器106-n实际上不包括一万亿字节的存储容量,而是配置成呈现为具有一万亿字节的存储空间。

48.作为实例,分级存储器设备104(例如mux 109和/或状态机111)可接收存取(例如读取)存储在持久存储器装置中的数据的部分的第一请求。在一些实施例中,持久存储器装置可在分级存储器设备104的外部。举例来说,持久存储器装置可为图3/4中所说明的持久存储器装置316/416。然而,在一些实施例中,持久存储器装置可包括在分级存储器设备104中(例如在分级存储器设备104内部)。

49.分级存储器设备104可经由接口例如从存储器管理电路系统(例如,经由本文中图3和4中所说明的接口308/408从存储器管理电路系统314/414)接收第一请求。第一请求可为例如来自i/o装置(例如,本文中图3和4中所说明的i/o装置310/410)的重导向请求。

50.响应于接收第一请求,分级存储器设备104可使用地址寄存器106-n确定对应于数据的部分(例如,持久存储器装置中的数据的位置)的持久存储器装置中的地址。举例来说,mux 109和/或状态机111可存取寄存器106-n以从寄存器106-n检索(例如撷取)地址。分级存储器设备104(例如mux 109和/或状态机111)还可响应于接收第一请求而检测对i/o装置的存取,且接收(例如撷取)对应于来自i/o装置的第一请求的i/o装置存取信息,包括例如虚拟i/o装置存取信息。i/o装置存取信息可存储在寄存器106-n和/或i/o存取组件107(例如,虚拟i/o装置存取信息可存储在i/o存取组件107中)中。此外,在一些实施例中,分级存储器设备104可使指示数据的部分不可由非持久存储器装置(例如,本文中图3和4中所说明的非持久存储器装置330/430)存取的信息与数据的部分相关联。

51.分级存储器设备104(例如mux 109和/或状态机111)可随后产生存取(例如读取)数据的部分的第二请求。第二请求可包括确定为对应于数据(例如,指示持久存储器装置中的数据的位置的地址)的持久存储器装置中的地址。连同第二请求,分级存储器设备104还可使用地址寄存器106-2产生中断信号(例如消息)。举例来说,mux 109和/或状态机111可通过存取地址寄存器102和使用中断组件115产生中断信号。

52.分级存储器设备104(例如mux 109和/或状态机111)可随后将中断信号和存取数据的部分的第二请求发送到持久存储器装置。举例来说,中断信号可作为第二请求的部分发送。在持久存储器装置在分级存储器设备104外部的实施例中,中断信号和第二请求可经由接口发送,经由所述接口接收第一请求(例如,经由本文中图3和4中所说明的接口308/408)。作为额外实例,在持久存储器装置包括在分级存储器设备104中的实施例中,中断信号可经由接口发送,而第二请求可直接发送到持久存储器装置。此外,分级存储器设备104还可经由接口从寄存器106-n发送i/o装置存取信息和/或从i/o存取组件107发送虚拟i/o装置存取信息作为第二请求的部分。

53.在发送中断信号和第二请求之后,分级存储器设备104可从(例如读取)持久存储器装置接收数据的部分。举例来说,在持久存储器装置在分级存储器设备104外部的实施例中,数据可经由接口从持久存储器装置接收,且在持久存储器装置包括在分级存储器设备104中的实施例中,数据可直接从持久存储器装置接收。在接收数据的部分之后,分级存储器设备104可将数据发送到i/o装置(例如,本文中图3和4中所说明的i/o装置310/410)。此外,分级存储器设备104可将数据存储在读取缓冲器103中(例如,在将数据发送到i/o装置之前)。

54.作为额外实例,分级存储器设备104(例如mux 109和/或状态机111)可接收将数据编程(例如写入)到持久存储器装置的第一请求。请求可例如经由接口从存储器管理电路系统(例如,经由本文中图3和4中所说明的接口308/408从存储器管理电路系统314/414)接收,且可以类似于先前本文所描述的第一存取请求的方式为来自i/o装置(例如,本文中图3和4中所说明的i/o装置310/410)的重导向请求。将编程到持久存储器装置的数据可存储在写入缓冲器105中(例如在发送到将编程的持久存储器装置之前)。

55.响应于接收第一请求,分级存储器设备104可使用地址寄存器106-n确定对应于数据(例如,数据将编程到其的持久存储器装置中的位置)的持久存储器装置中的地址。举例来说,mux 109和/或状态机111可存取寄存器106-n以从寄存器106-n检索(例如撷取)地址。分级存储器设备104(例如mux 109和/或状态机111)还可响应于接收第一请求而检测对i/o装置的存取,且接收(例如撷取)对应于来自i/o装置的第一请求的i/o装置存取信息,包括例如虚拟i/o装置存取信息。i/o装置存取信息可存储在寄存器106-n和/或i/o存取组件107(例如,虚拟i/o装置存取信息可存储在i/o存取组件107中)中。此外,在一些实施例中,分级存储器设备104可响应于接收第一请求而使指示数据不可由非持久存储器装置(例如,本文中图3和4中所说明的非持久存储器装置330/430)存取的信息与数据相关联。

56.分级存储器设备104(例如mux 109和/或状态机111)可随后产生将数据编程(例如写入)到持久存储器装置的第二请求。第二请求可包括将编程到持久存储器装置的数据,和确定对应于数据的持久存储器装置中的地址(例如数据将编程到的地址)。连同第二请求,分级存储器设备104还可以类似于先前针对第二存取请求所描述的方式使用地址寄存器

106-2产生中断信号(例如消息)。

57.分级存储器设备104(例如mux 109和/或状态机111)可随后发送中断信号和将数据编程到持久存储器装置的第二请求。举例来说,中断信号可作为第二请求的部分发送。在持久存储器装置在分级存储器设备104外部的实施例中,中断信号和第二请求可经由接口发送,经由所述接口接收第一请求(例如,经由本文中图3和4中所说明的接口308/408)。作为额外实例,在持久存储器装置包括在分级存储器设备104中的实施例中,中断信号可经由接口发送,而第二请求可直接发送到持久存储器装置。此外,分级存储器设备104还可经由接口从寄存器106-n发送i/o装置存取信息和/或从i/o存取组件107发送虚拟i/o装置存取信息,作为第二请求的部分。

58.尽管图1中未明确展示,但分级存储器设备104可耦合到主机计算系统。主机计算系统可包括系统母板和/或底板,且可包括数个处理资源(例如,一或多个处理器、微处理器或某一其它类型的控制电路系统)。举例来说,主机和分级存储器设备104可为服务器系统和/或高性能计算(hpc)系统和/或其一部分。在一些实施例中,计算系统可具有冯诺伊曼体系结构(von neumann architecture),然而,本公开的实施例可实施于可不包括常常与冯诺伊曼体系结构相关联的一或多个组件(例如,cpu、alu等)的非冯诺伊曼体系结构中。

59.图2为根据本公开的数个实施例的分级存储器设备204的功能框图。分级存储器设备204可为计算机系统的部分,和/或可以类似于先前结合图1所描述的分级存储器设备104的方式提供为fpga、asic、数个离散电路组件等。

60.如图2中所说明,分级存储器设备204可包括存储器资源202,其可包括数据缓冲器218和/或输入/输出(i/o)装置存取组件207。存储器资源202可类似于先前结合图1所描述的存储器资源102,除了数据缓冲器218可替代读取缓冲器103和写入缓冲器105。举例来说,先前结合读取缓冲器103和写入缓冲器105所描述的功能性可组合到数据缓冲器218的功能性中。在一些实施例中,数据缓冲器218的大小可为约4kb,但实施例不限于此特定大小。

61.分级存储器设备104可进一步包括存储器存取多路复用器(mux)109、状态机111,和/或分级存储器控制器113(或为简单起见“控制器”)。如图1中所展示,分级存储器控制器113可包括多个地址寄存器106-1到106-n和/或中断组件115。存储器存取mux 109可包括电路系统,所述电路系统可包含一或多个逻辑门且可配置成控制针对分级存储器设备104的数据和/或地址总线。举例来说,存储器存取mux 109可传递消息进出存储器资源102,以及与分级存储器控制器113和/或状态机111通信,如下文更详细地描述。

62.分级存储器设备204可进一步包括存储器存取多路复用器(mux)209、状态机211,和/或分级存储器控制器213(或为简单起见“控制器”)。如图1中所展示,分级存储器控制器113可包括多个地址寄存器206-1到206-n和/或中断组件115。

63.存储器存取mux 209可包括类似于先前结合图1所描述的mux 109的电路系统的电路系统,且可以类似于先前针对mux 109所描述的方式重导向由分级存储器设备204(例如,从主机、i/o装置或超管理器)接收到的传入消息、命令和/或请求(例如读取和/或写入请求)。举例来说,mux 209可重导向这些请求作为确定地址寄存器106中的将存取的地址的操作的部分,如先前结合图1所描述。举例来说,响应于确定请求对应于与写入到分级存储器设备204外部的位置的地址相关联的数据,mux 209可促进数据的检索、数据到数据缓冲器218的传递和/或数据到分级存储器设备204外部的位置的传递,如先前结合图1所描述。此

外,响应于确定请求对应于从分级存储器设备204外部的位置读取的数据,mux 209可促进数据的检索,数据到数据缓冲器218的传递和/或数据或与数据相关联的地址信息到分级存储器设备204内部的位置的传递,例如地址寄存器206,如先前结合图1所描述。

64.状态机211可包括配置成对输入执行操作且以类似于先前结合图1所描述的状态机111的方式产生输出的一或多个处理装置、电路组件和/或逻辑。举例而言,状态机211可传递存取信息(例如“i/o access info”)和控制消息(例如“mux ctrl”)进出存储器存取多路复用器209,和/或中断请求消息(例如“interrupt request”)进出分级存储器控制器213,如先前结合图1所描述。然而,相比于状态机111,应注意状态机211可不传递中断配置信息(例如“interrupt config”)进出控制器213。

65.分级存储器控制器213可以类似于先前结合图1所描述的控制器113的方式包括核心。在一些实施例中,分级存储器控制器213可以类似于控制器113的方式为pcie核心。

66.分级存储器控制器213可包括地址寄存器206-1到206-n和/或中断组件215。地址寄存器206-1到206-n可为基地址寄存器(bar),其可存储由分级存储器设备204或计算系统(例如,本文中图3和4中所说明的计算系统301/401)使用的存储器地址。

67.地址寄存器中的至少一个(例如地址寄存器206-1)可以类似于先前结合图1所描述的地址寄存器106-1的方式存储存储器地址,所述存储器地址提供从例如图4中所说明的超管理器412的外部位置对分级存储器设备204的内部寄存器的存取。地址寄存器中的又一个(例如地址寄存器206-2)可以类似于先前结合图1所描述的地址寄存器106-3的方式存储对应于对超管理器的存取和来自超管理器的地址。此外,至少一个地址寄存器(例如地址寄存器206-n)可以类似于先前结合图1所描述的地址寄存器106-n的方式存储地址且包括地址空间。然而,相比于控制器113,应注意控制器213可不包括类似于地址寄存器106-2的地址寄存器,所述地址寄存器106-2可存储对应于中断控制和映射dma读取和dma写入控制和/或状态寄存器的地址,如结合图1所描述。

68.如图2所展示(且相比于分级存储器设备104),分级存储器设备204可包括清除中断寄存器222和超管理器完成寄存器224。清除中断寄存器222可存储由中断组件215产生的中断信号作为读取或写入数据的请求的部分,如本文中先前所描述,且超管理器完成寄存器224可提供超管理器(例如,图4中所说明的超管理器412)存取分级存储器设备204的内部寄存器以映射地址以读取或写入数据的指示(例如到状态机211),如本文中先前所描述。一旦读取或写入请求已完成,中断信号便可从寄存器222清除,且寄存器224可提供超管理器不再存取分级存储器设备204的内部寄存器的指示(例如到状态机211)。

69.如图2中所展示(且相比于分级存储器设备104),分级存储器设备204可包括存取保持组件226。存取保持组件226可限制地址寄存器206-n的地址空间。举例来说,存取保持组件226可限制地址寄存器206-n的地址低于4k。

70.尽管图2中未明确展示,但分级存储器设备204可以类似于针对分级存储器设备104描述的方式耦合到主机计算系统。主机和分级存储器设备204可例如为服务器系统和/或高性能计算(hpc)系统和/或其一部分,如结合图1所描述。

71.图3为根据本公开的数个实施例的呈包括分级存储器设备304的计算系统301形式的功能框图。分级存储器设备304可分别类似于图1和2中所说明的分级存储器设备104和/或204。此外,计算系统201可包括输入/输出(i/o)装置310、持久存储器装置316、非持久存

储器装置330、中间存储器组件320和存储器管理组件314。可经由接口308促进分级存储器设备304、i/o装置310与持久存储器装置316、非持久存储器装置230和存储器管理组件314之间的通信。

72.i/o装置310可为配置成经由物理地址和/或虚拟机物理地址提供直接存储器存取的装置。在一些实施例中,i/o装置310可为网络接口卡(nic)或网络接口控制器、存储装置、图形渲染装置或其它i/o装置。i/o装置310可为物理i/o装置,或i/o装置310可为虚拟化i/o装置310。举例来说,在一些实施例中,i/o装置310可为经由总线或例如pcie接口或其它合适的接口的接口以物理方式耦合到计算系统的物理卡。在i/o装置310为虚拟化i/o装置310的实施例中,虚拟化i/o装置310可以分布的方式提供i/o功能性。

73.持久存储器装置316可包括数个存储器单元阵列。举例来说,阵列可为具有nand架构的快闪阵列。然而,实施例不限于特定类型的存储器阵列或阵列架构。存储器单元可例如分组成包括数个物理页的多个块。数个块可包括在存储器单元的平面中,且阵列可包括数个平面。

74.持久存储器装置316可包括易失性存储器和/或非易失性存储器。在数个实施例中,持久存储器装置316可包括多芯片装置。多芯片装置可包括数个不同存储器类型和/或存储器模块。举例来说,存储器系统可包括任何类型的模块上的非易失性或易失性存储器。在持久存储器装置316包括非易失性存储器的实施例中,持久存储器装置316可为例如nand或nor快闪存储器装置的快闪存储器装置。

75.然而,实施例不限于此,且持久存储器装置316可包括其它非易失性存储器装置,例如非易失性随机存取存储器装置(例如,nvram、reram、feram、mram、pcm)、例如电阻可变存储器装置(例如,电阻式和/或相变存储器装置,例如3d交叉点(3d xp)存储器装置)的“新兴”存储器装置、包括自选存储器(ssm)单元的阵列的存储器装置等,或其组合。非易失性存储器的电阻式和/或相变阵列可结合可堆叠交叉网格化数据存取阵列基于体电阻的改变来执行位存储。此外,相比于许多基于快闪的存储器,电阻式和/或相变存储器装置可执行就地写入操作,其中可在不预先擦除非易失性存储器单元的情况下对易失性存储器单元进行编程。相比于基于快闪的存储器,自选存储器单元可包括具有充当存储器单元的开关和存储元件两者的单个硫族化物材料的存储器单元。

76.持久存储器装置316可为计算系统301提供存储容量,且因此可用作整个计算系统301的额外存储器或存储装置、计算系统301的主存储器,或其组合。然而,实施例不限于特定类型的存储器装置,且持久存储器装置316可包括ram、rom、sram dram、sdram、pcram、rram和快闪存储器等等。此外,尽管在图3中说明单个持久存储器装置316,但实施例不限于此,且计算系统301可包括一或多个持久存储器装置316,其中的每一个可具有或可不具有与其相关联的相同架构。作为非限制性实例,在一些实施例中,持久存储器装置316可包含具有不同架构的两个离散存储器装置,例如nand存储器装置和电阻可变存储器装置。

77.非持久存储器装置330可包括易失性存储器,例如易失性存储器单元的阵列。在数个实施例中,非持久存储器装置330可包括多芯片装置。多芯片装置可包括数个不同存储器类型和/或存储器模块。在一些实施例中,非持久存储器装置330可充当计算系统301的主存储器。举例来说,非持久存储器装置330可为用以向计算系统301提供主存储器的动态随机存取(dram)存储器装置。然而,实施例不限于包含dram存储器装置的非持久存储器装置

330,且在一些实施例中,非持久存储器装置330可包括其它非持久存储器装置,例如ram、sram dram、sdram、pcram和/或rram等等。

78.非持久存储器装置330可存储可例如由主机计算装置请求的数据,作为计算系统301的操作的部分。举例来说,当计算系统301为多用户网络的部分时,非持久存储器装置330可存储在计算系统301的操作期间可在主机计算装置(例如,部署在多用户网络中的虚拟机)之间传递的数据。

79.在一些方法中,例如非持久存储器装置330的非持久存储器可存储由主机(例如,部署在多用户网络中的虚拟机)存取的所有用户数据。举例来说,归因于非持久存储器的速度,一些方法依赖于非持久存储器为部署在多用户网络中的虚拟机提供存储器资源。然而,在这些方法中,归因于非持久存储器通常比持久存储器(例如,持久存储器装置316)昂贵,成本可能成问题。

80.相反,如下文更详细描述,本文中的实施例可允许将存储在非持久存储器装置330中的至少一些数据存储在持久存储器装置316中。这可允许以比依赖于非持久存储器进行用户数据存储的方法低的成本将额外存储器资源提供到计算系统301,例如多用户网络。

81.计算系统301可包括存储器管理组件314,其可以通信方式耦合到非持久存储器装置330和/或接口308。在一些实施例中,存储器管理组件314可为可以通信方式将例如接口308的直接存储器存取总线耦合到非持久存储器装置330的输入/输出存储器管理单元(io mmu)。然而,实施例不限于此,且存储器管理组件314可为促进接口308和非持久存储器装置330之间的通信的其它类型的存储器管理硬件。

82.存储器管理组件314可将装置可见虚拟地址映射到物理地址。举例来说,存储器管理组件314可将与i/o装置310相关联的虚拟地址映射到非持久存储器装置330和/或持久存储器装置316中的物理地址。在一些实施例中,可通过本文中图1中所说明的读取缓冲器、写入缓冲器和/或i/o存取缓冲器或本文中图2中所说明的数据缓冲器和/或i/o存取缓冲器促进映射与i/o装置310相关联的虚拟条目。

83.在一些实施例中,存储器管理组件314可读取与i/o装置310相关联的虚拟地址,和/或将虚拟地址映射到非持久存储器装置330中的物理地址或映射到分级存储器设备304中的地址。在存储器管理组件314将虚拟i/o装置310地址映射到分级存储器设备304中的地址的实施例中,存储器管理组件314可将从i/o装置310接收到的读取请求(或写入请求)重导向到分级存储器设备304,其可将与i/o装置310读取或写入请求相关联的虚拟地址信息存储在分级存储器设备304的地址寄存器(例如地址寄存器306-n)中,如先前结合图1和2所描述。在一些实施例中,地址寄存器306-n可为分级存储器设备304的特定基地址寄存器,例如bar4地址寄存器。

84.重导向读取(或写入)请求可经由接口308从存储器管理组件314传递到分级存储器设备304。在一些实施例中,接口308可为pcie接口,且因此可根据pcie协议在存储器管理组件314和分级存储器设备304之间传送信息。然而,实施例不限于此,且在一些实施例中,接口308可为根据另一合适的协议起作用的接口或总线。

85.在虚拟nic地址存储在分级存储器设备304中之后,可将对应于虚拟nic地址的数据写入到持久存储器装置316。举例来说,对应于存储在分级存储器设备304中的虚拟nic地址的数据可存储在持久存储器装置316的物理地址位置中。在一些实施例中,可通过如本文

中结合图4所描述的超管理器促进传递数据进和/或出持久存储器装置316。

86.当数据例如由主机计算装置(例如,计算系统301中部署的虚拟机)请求时,所述请求可由存储器管理组件314从i/o装置310重导向到分级存储器设备304。由于对应于持久存储器装置316中的数据的物理位置的虚拟nic地址存储在分级存储器设备304的地址寄存器306-n中,因此分级存储器设备304可促从持久存储器装置316检索数据,如本文中先前所描述。举例来说,分级存储器设备304可促进结合超管理器从持久存储器装置316检索数据,如本文中结合图4更详细描述。

87.在一些实施例中,当已存储在持久存储器装置316中的数据传递出持久存储器装置316时(例如,当已存储在持久存储器装置316中的数据由主机计算装置请求时),数据可在提供到主机计算装置之前传递到中间存储器组件320和/或非持久存储器装置330。举例来说,由于传递到主机计算装置的数据可以确定性方式(例如,经由ddr接口)传递,因此数据可在满足数据请求之前暂时传递到使用ddr总线操作的存储器,例如中间存储器组件320和/或非持久存储器装置330。

88.图4为根据本公开的数个实施例的呈包括分级存储器设备的计算系统形式的另一功能框图。如图4中所展示,计算机系统401可包括分级存储器设备404,其可类似于图1、2和3中所说明的分级存储器设备104/204/304。另外,计算机系统401可包括i/o装置410、持久存储器装置416、非持久存储器装置430、中间存储器组件420、存储器管理组件414和超管理器412。

89.在一些实施例中,计算机系统401可为多用户网络,例如软件定义的数据中心、云计算环境等。在这类实施例中,计算机系统可配置成具有在其上运行的一或多个虚拟机417。举例来说,在一些实施例中,一或多个虚拟机417可部署在超管理器412上且可由多用户网络的用户存取。

90.i/o装置410、持久存储器装置416、非持久存储器装置430、中间存储器组件420和存储器管理组件414可类似于图3中所说明的i/o装置310、持久存储器装置316、非持久存储器装置330、中间存储器组件320和存储器管理组件314。可经由接口408促进分级存储器设备404、i/o装置410与持久存储器装置416、非持久存储器装置430、超管理器412和存储器管理组件414之间的通信,所述接口408可类似于图3中所说明的接口308。

91.如上文结合图3所描述,存储器管理组件414可致使将与i/o装置410相关联的读取请求或写入请求重导向到分级存储器设备404。分级存储器设备404可产生和/或存储对应于所请求数据的逻辑地址。如上文所描述,分级存储器设备404可将对应于所请求数据的逻辑地址存储在基地址寄存器中,例如分级存储器设备404的地址寄存器406-n。

92.如图4中所展示,超管理器412可经由接口408与分级存储器设备404和/或i/o装置410通信。超管理器412可经由分级存储器设备404的nic存取组件(例如图1和2中所说明的nic存取组件107/207)在分级存储器设备404之间发射数据。另外,超管理器412可与持久存储器装置416、非持久存储器装置430、中间存储器组件420和存储器管理组件414通信。超管理器可配置成执行专门指令来执行本文中所描述的操作和/或任务。

93.举例来说,超管理器412可执行指令以监测数据流量和数据流量模式以确定数据是否应存储在非持久存储器装置430中或数据是否应传递到持久存储器装置416。也就是说,在一些实施例中,超管理器412可执行指令以随时间学习用户数据请求模式,且基于所

述模式选择性地将数据的部分存储在非持久存储器装置430或持久存储器装置416中。此可允许较频繁存取的数据存储在非持久存储器装置430中,而较不频繁存取的数据存储在持久存储器装置416中。

94.由于相比于最近不太使用或最近不太检视的数据,用户可更频繁地存取最近使用或检视的数据,因此超管理器可执行专门指令以致使最近不太使用或检视的数据存储在持久存储器装置416中,和/或致使最近存取或检视的数据存储在非持久存储器装置430中。在非限制性实例中,相比于最近不太拍摄(例如,一个月以前、一年以前等)的照片,用户可更频繁地检视社交媒体上的最近拍摄(例如,一周内等)的照片。基于此信息,超管理器412可执行专门指令以致使最近不太检视或拍摄的照片存储在持久存储器装置416中,借此减小存储在非持久存储器装置430中的数据量。此可减少必需为计算系统401提供的非持久存储器的总量,借此减小成本且允许更多用户存取非持久存储器装置430。

95.在操作中,计算系统401可配置成拦截来自i/o装置410的数据请求且将请求重导向到分级存储器设备404。在一些实施例中,超管理器412可控制对应于数据请求的数据将存储在非持久存储器装置430中还是持久存储器装置416中(或从哪一个检索)。举例来说,超管理器412可执行指令以选择性地控制数据存储在持久存储器装置416中还是非持久存储器装置430中(或从哪一个检索)。

96.作为控制数据存储在持久存储器装置416中和/或非持久存储器装置430中(或从哪一个检索)的部分,超管理器412可致使存储器管理组件414映射与将重导向到分级存储器设备404且存储在分级存储器设备404的地址寄存器406中的数据相关联的逻辑地址。举例来说,超管理器412可执行指令来控制涉及将经由存储器管理组件414选择性地重导向到分级存储器设备404的数据的读取和写入请求。

97.存储器管理组件414可将邻接虚拟地址映射到基础片段物理地址。因此,在一些实施例中,存储器管理组件414可允许将虚拟地址映射到物理地址,而不必要求物理地址为邻接的。此外,在一些实施例中,存储器管理组件414可允许并不足够长地支持存储器地址以寻址的其对应物理存储器空间的装置在存储器管理组件414中寻址。

98.归因于与持久存储器装置416相关联的数据传递的非确定性性质,分级存储器设备404可在一些实施例中配置成告知计算系统401可能引发传递数据进出持久存储器装置316中的延迟。作为起始化延迟的部分,当将数据请求重导向到分级存储器设备404时,分级存储器设备404可为计算机系统401提供页错误处置。在一些实施例中,分级存储器设备404可产生和断言对超管理器412的中断,如本文中先前所描述,以起始将数据传递到持久存储器装置416中或从持久存储器装置416传递出数据的操作。举例来说,归因于与持久存储器装置416相关联的数据检索和存储的非确定性性质,分级存储器设备404可在请求传递存储在持久存储器装置416中的数据时产生超管理器中断415。

99.响应于由分级存储器设备404产生的页错误中断,超管理器412可从分级存储器设备404检索对应于数据的信息。举例而言,超管理器412可从分级存储器设备接收nic存取数据,其可包括对应于存储在分级存储器设备404的地址寄存器406中的数据的逻辑到物理地址映射,如本文中先前所描述。

100.一旦数据已存储在持久存储器装置416中,非持久存储器装置430的部分(例如页、块等)可标记为不可由分级存储器设备404存取,如本文中先前所描述,使得计算机系统401

不试图从非持久存储器装置430存取数据。这可允许数据请求被页错误拦截,其可由分级存储器设备404产生且在已存储在持久存储器装置416中的数据由i/o装置410请求时断言到超管理器412。

101.相比于响应于应用请求存取不由存储器管理单元(例如,存储器管理组件414)映射的存储器页而发生页错误异常的方法,在本公开的实施例中,上文所描述的页错误可由分级存储器设备404响应于数据在存储器管理组件414中映射到分级存储器设备404而产生,所述分级存储器设备404又将数据映射到持久存储器装置316。

102.在一些实施例中,中间存储器组件420可用以响应于由i/o装置410起始的数据请求而缓冲存储在持久存储器装置416中的数据。相比于可经由pcie接口传送数据的持久存储器装置416,中间存储器组件420可采用ddr接口来传送数据。因此,在一些实施例中,中间存储器组件420可以确定性方式操作。举例来说,在一些实施例中,存储在持久存储器装置416中的所请求的数据可经由将中间存储器组件420耦合到i/o装置410的ddr接口暂时从持久存储器装置416传递到中间存储器组件420且随后传递到主机计算装置。

103.在一些实施例中,中间存储器组件可包含在计算机系统401中部署的离散存储器组件(例如sram高速缓存)。然而,实施例不受如此限制,且在一些实施例中,中间存储器组件420可为可分配用于响应于数据请求而从持久存储器装置416传递数据的非持久存储器装置430的部分。

104.在非限制性实例中,存储器管理电路系统(例如存储器管理组件414)可耦合到分级存储器组件404(例如逻辑电路系统)。存储器管理电路系统可配置成接收将具有与其相关联的对应虚拟网络接口控制器地址的数据写入到非持久存储器装置(例如非持久存储器装置430)的请求。存储器管理电路系统可进一步配置成至少部分地基于数据的特性而重导向将数据写入到逻辑电路系统的请求。数据的特性可包括请求或存取数据的频繁程度,自从最后存取或请求数据以来已发生的时间量,数据的类型(例如,数据是否对应于特定文档类型,例如照片、文件、音频文档、应用文档等)等等。

105.在一些实施例中,存储器管理电路系统可配置成基于由超管理器412产生的命令和/或由超管理器412执行的指令而将请求重导向到逻辑电路系统。举例来说,如上文所描述,超管理器412可执行指令以控制对应于数据请求(例如,由i/o装置410产生的数据请求)的数据是存储在持久存储器装置416中还是非持久存储器装置430中。

106.在一些实施例中,超管理器412可促进通过将地址(例如逻辑地址)写入到存储器管理电路系统重导向请求。举例而言,如果超管理器412确定对应于特定数据请求的数据将存储在(或从其检索)持久存储器装置416中,那么超管理器412可致使对应于重导向将由存储器管理电路系统存储的请求的地址,使得数据请求重导向到逻辑电路。

107.在接收重导向请求后,逻辑电路系统可配置成响应于接收重导向请求而确定(例如产生)对应于数据的地址和/或将地址存储在逻辑电路系统内的地址寄存器406中,如本文中先前所描述。在一些实施例中,逻辑电路系统可配置成基于接收重导向请求而使指示数据不可由非持久存储器装置430存取的指示与数据相关联,如本文中先前描述。

108.逻辑电路系统可配置成至少部分地基于接收重导向请求而致使数据写入到持久存储器装置(例如持久存储器装置416)。在一些实施例中,逻辑电路系统可配置成产生中断信号且将中断信号断言到耦合到逻辑电路系统的超管理器(例如超管理器412),作为致使

数据写入到持久存储器装置416的部分,如本文中先前所描述。如上文所描述,持久存储器装置416可包含3d xp存储器装置、自选存储器单元阵列、nand存储器装置或其它合适的持久存储器或其组合。

109.在一些实施例中,逻辑电路系统可配置成从存储器管理电路系统接收重导向请求以从持久存储器装置416检索数据,将从持久存储器装置416检索数据的请求传递到超管理器412,和/或将中断信号断言到超管理器412,作为从持久存储器装置416检索数据的请求的部分,如本文中先前所描述。超管理器412可配置成从持久存储器装置416检索数据和/或将数据传递到非持久存储器装置430。一旦数据已从持久存储器装置416检索,超管理器412可配置成致使与待传递到存储器管理电路系统414的数据相关联的更新后的地址。

110.在另一非限制性实例中,计算机系统401可为多用户网络,例如软件定义的数据中心、云计算环境等。多用户网络可包括计算资源池,所述计算资源池包括非持久存储器装置430和持久存储器装置416。多用户网络可进一步包括耦合到包含多个地址寄存器406的分级存储器组件404(例如逻辑电路系统)的接口408。在一些实施例中,多用户网络可进一步包括耦合到接口408的超管理器412。

111.超管理器412可配置成接收存取对应于非持久存储器组件430的数据的请求,确定数据存储在持久存储器装置中,且致使存取将重导向到逻辑电路系统的数据的请求。存取数据的请求可为从持久存储器装置或非持久存储器装置读取数据的请求或将数据写入到持久存储器装置或非持久存储器装置的请求。

112.在一些实施例中,逻辑电路系统可配置成响应于确定数据存储在持久存储器装置416中而将存取来自持久存储器装置416的数据的请求传递到超管理器412。逻辑电路系统可配置成将中断断言到超管理器,作为超管理器412存取对应于持久存储器装置416的数据的请求的部分,如本文中先前所描述。

113.超管理器412可配置成基于从逻辑电路系统接收到的请求而致使数据使用持久存储器装置416进行存取。如上文所描述,持久存储器装置416可包含电阻可变存储器装置,例如电阻式存储器、相变存储器、自选存储器单元阵列或其组合。在一些实施例中,超管理器412可配置成致使数据传递到非持久存储器装置430,作为致使数据使用持久存储器装置416进行存取的部分。

114.超管理器412可进一步配置成响应于致使数据使用持久存储器装置416进行存取,更新存储在与多用户网络相关联的存储器管理组件414中的信息。举例来说,超管理器412可配置成致使对应于将存储在存储器管理组件414中的数据的更新后的虚拟地址。

115.在一些实施例中,多用户网络可包括耦合到逻辑电路系统的i/o装置410。在这类实施例中,逻辑电路系统可配置成响应于超管理器412而将通知发送到i/o装置410,从而致使数据使用持久存储器装置416进行存取。

116.图5为表示根据本公开的数个实施例的分级存储器设备的实例方法540的流程图。分级存储器设备可例如为先前结合图1、2、3和4所描述的分级存储器设备104/204/304/404。

117.在框542处,方法540可包括通过分级存储器设备经由接口从存储器管理电路系统接收存取存储在持久存储器装置的中数据的第一请求。存储器管理电路系统、接口和持久存储器装置可例如分别为先前结合图3和4所描述的存储器管理电路系统(例如组件)314/

414、接口308/408,和持久存储器装置316/416。第一请求可例如为来自i/o装置的重导向请求,如本文中先前所描述。

118.在框544处,方法540可包括响应于接收第一请求而使用分级存储器设备的第一地址寄存器确定对应于持久存储器装置中的数据的地址。第一地址寄存器可例如为先前结合图1和2所描述的地址寄存器106-n/206-n,且可用于以类似于结合图1和2所描述的方式确定对应于数据的地址。

119.在546处,方法540可包括响应于接收第一请求而使用分级存储器设备的第二地址寄存器产生中断信号,和存取数据的第二请求,其中第二请求包括在544处所确定的地址。第二地址寄存器可例如为先前结合图1和2所描述的地址寄存器106-2/206-2,且可用于以类似于先前结合图1和2所描述的方式产生中断信号。

120.在框548处,方法540可包括发送中断信号和存取数据的第二请求。中断信号和第二请求可以类似于先前结合图1和2所描述的方式发送。

121.图6为表示根据本公开的数个实施例的分级存储器设备的实例方法660的另一流程图。分级存储器设备可例如为先前结合图1、2、3和4所描述的分级存储器设备104/204/304/404。

122.在框662处,方法660可包括通过分级存储器设备经由接口从存储器管理电路系统接收将数据编程到持久存储器装置的第一请求。存储器管理电路系统、接口和持久存储器装置可例如分别为先前结合图3和4所描述的存储器管理电路系统(例如组件)314/414、接口308/408,和持久存储器装置316/416。第一请求可例如为来自i/o装置的重导向请求,如本文中先前所描述。

123.在框664处,方法660可包括响应于接收第一请求而使用分级存储器设备的第一地址寄存器确定对应于数据的地址。第一地址寄存器可例如为先前结合图1和2所描述的地址寄存器106-n/206-n,且可用于以类似于结合图1和2所描述的方式确定对应于数据的地址。

124.在框666处,方法660可包括响应于接收第一请求而使用分级存储器设备的第二地址寄存器产生中断信号,和将数据编程到持久存储器装置的第二请求,其中第二请求包括在框664处所确定的地址。第二地址寄存器可例如为先前结合图1和2所描述的地址寄存器106-2/206-2,且可用于以类似于先前结合图1和2所描述的方式产生中断信号。

125.在框668处,方法660可包括发送中断信号和将数据编程到持久存储器装置的第二请求。中断信号和第二请求可以类似于先前结合图1和2所描述的方式发送。

126.尽管已在本文中说明且描述了具体实施例,但本领域的一般技术人员应了解,经计算以实现相同结果的布置可取代所展示的具体实施例。本公开意图涵盖本公开的一或多个实施例的修改或变化形式。应理解,以上描述是以说明性方式而非限制性方式进行。对于本领域的一般技术人员而言在审阅上述描述之后上述实施例的组合和本文中未具体描述的其它实施例将为显而易见的。本公开的一或多个实施例的范围包括使用以上结构和过程的其它应用。因此,本公开的一或多个实施例的范围应参考所附权利要求书以及此类权利要求被赋予的等同物的完整范围而确定。

127.在实前述具体实施方式中,出于简化本公开的目的而将一些特征一起分组在单个实施例中。本公开的这一方法不应理解为反映本公开的所公开实施例必须使用比每个权利要求中明确陈述的特征更多的特征的意图。相反,如所附权利要求书所反映,本发明主题在

于单个所公开实施例的不到全部的特征。因此,所附权利要求书特此并入于具体实施方式中,其中每项权利要求就其自身而言作为单独实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。