一种pcie交换设备

技术领域

1.本发明创造属于交换机技术领域,尤其是涉及一种pcie交换设备。

背景技术:

2.pci-express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,简称pcie,是由英特尔在2001年提出的,旨在替代旧的pci,pci-x和agp总线标准。

3.现有技术的缺陷:

4.现在市面上越来越多的芯片,尤其是高速串行交换芯片,比如以太网、rapidio交换芯片采用pcie作为其配置管理、以及协议栈上送下发的通道,而且这类交换芯片经常多设备组网使用,而市面上的处理器单片只有有限的pcie接口,可能在数量上不足以满足系统内的交换芯片数量,而使用多片处理器有时又有些浪费,不论是成本还是功耗方面;这时就需要pcie交换设备,拓展pcie总线,用一个处理器作为rc,去管理多个ep设备,以及他们协议栈的上送下发。

5.在一些pcie相关的产品开发或者芯片开发过程中,标准的插卡式连接方式可能不方便,特别是一些fpga开发板或者原型验证板本身体积重量都比较大,作为ep(金手指)去插接到一些处理器(root)系统中可能会更加不便;另外随着芯片规模的提升,pcb板的层叠厚度也经常较大,而pcie要求的金手指厚度必须为1.6mm,这时就需要对pcb做特殊处理,提高了制板难度和成本。

技术实现要素:

6.有鉴于此,为克服上述缺陷,本发明创造旨在提出一种新型的pcie交换设备。

7.为达到上述目的,本发明创造的技术方案是这样实现的:

8.一种pcie交换设备,包括交换芯片,以及与该交换芯片连接的sfp 接口和qsfp 接口,所述sfp 接口数量为多个;

9.其中一路sfp 接口通过dac无源线缆连接外部处理器,用于作为pcie的root设备,其他接口均为下行端口,通过dac无源线缆连接外部的交换芯片或者pcie ep设备。

10.进一步的,所述交换芯片为89hpes12nt12g2芯片。

11.进一步的,所述sfp 接口的数量为8个;

12.每个所述sfp 接口均对应设有一个光纤连接器;

13.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe00tn0、pe00tp0、pe00rn0、pe00rp0针脚;

14.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe01tn0、pe01tp0、pe01rn0、pe01rp0针脚;

15.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe02tn0、pe02tp0、pe02rn0、pe02rp0针脚;

16.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe03tn0、pe03tp0、pe03rn0、pe03rp0针脚;

17.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe08tn0、pe08tp0、pe08rn0、pe08rp0针脚;

18.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe09tn0、pe09tp0、pe09rn0、pe09rp0针脚;

19.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe10tn0、pe10tp0、pe10rn0、pe10rp0针脚;

20.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe11tn0、pe11tp0、pe11rn0、pe11rp0针脚。

21.进一步的,所述qsfp 接口的数量为1个;

22.qsfp 接口采用qsfp-1888968连接器;

23.qsfp-1888968连接器的rx1p、rx1n、rx2p、rx2n、rx3p、rx3n、rx4p、rx4n、tx1p、tx1n、tx2p、tx2n、tx3p、tx3n、tx4p、tx4n针脚分别连接89hpes12nt12g2芯片的pe16tn0、pe16tp0、pe17tn0、pe17tp0、pe18tn0、pe18tp0、pe19tn0、pe19tp0、pe16rn0、pe16rp0、pe17rn0、pe17rp0、pe18rn0、pe18rp0、pe19rn0、pe19rp0针脚。

24.进一步的,还包括有用于控制交换芯片工作模式的config模块,所述config模块连接交换芯片。

25.进一步的,还包括用于为交换芯片和接口供电的供电电路。

26.进一步的,还包括时钟电路,所述时钟电路连接交换芯片。

27.进一步的,所述时钟电路包括8t49n0041芯片,该芯片的q0、nq0、q1、nq1针脚分别连接89hpes12nt12g2芯片的gclkp0、gclkn0、gclkp1、gclkn1针脚。

28.相对于现有技术,本发明创造所述的pcie交换设备具有以下优势:

29.(1)本发明创造所述的pcie交换设备板卡搭载pcie gen2交换芯片,支持最多11个下行通道,这样一个处理器的一个pcie rc可以管理多个带有pcie配置接口的高速eth、srio交换芯片或者其他的pcie ep设备。

30.(2)本发明创造所述的pcie交换设备板卡采用sfp /qsfp 接口的dac线缆与外部上行或下行设备连接,而芯片开发过程中用到的fpga原型验证板或者其他开发板多数都配备sfp 或者qsfp 的接口,他们之间互连就可以做到非常方便,解决了pcie连接器在开发过程中插接不便的问题。

附图说明

31.构成本发明创造的一部分的附图用来提供对本发明创造的进一步理解,本发明创造的示意性实施例及其说明用于解释本发明创造,并不构成对本发明创造的不当限定。在附图中:

32.图1为本发明创造实施例所述的pcie交换设备原理框图;

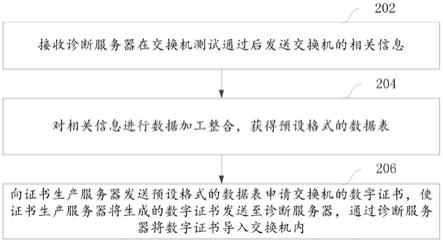

33.图2为本发明创造实施例所述的交换芯片部分结构图一;

34.图3为本发明创造实施例所述的交换芯片部分结构图二;

35.图4为本发明创造实施例所述的sfp 接口电路图;

36.图5为本发明创造实施例所述的qsfp 接口电路图;

37.图6为本发明创造实施例所述的供电模块电路图;

38.图7为本发明创造实施例所述的时钟电路图。

具体实施方式

39.需要说明的是,在不冲突的情况下,本发明创造中的实施例及实施例中的特征可以相互组合。

40.在本发明创造的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明创造和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明创造的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明创造的描述中,除非另有说明,“多个”的含义是两个或两个以上。

41.在本发明创造的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明创造中的具体含义。

42.下面将参考附图并结合实施例来详细说明本发明创造。

43.如图1所示,一种pcie交换设备,包括交换芯片,以及与该交换芯片连接的sfp 接口和qsfp 接口,所述sfp 接口数量为多个;

44.其中一路sfp 接口通过dac无源线缆连接外部处理器,用于作为pcie的root设备,其他接口均为下行端口,通过dac无源线缆连接外部的交换芯片或者pcie ep设备。

45.所述交换芯片为89hpes12nt12g2芯片。

46.所述sfp 接口的数量为8个;

47.每个所述sfp 接口均对应设有一个光纤连接器;

48.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe00tn0、pe00tp0、pe00rn0、pe00rp0针脚,如图3,图4所示;

49.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe01tn0、pe01tp0、pe01rn0、pe01rp0针脚;

50.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe02tn0、pe02tp0、pe02rn0、pe02rp0针脚;

51.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe03tn0、pe03tp0、pe03rn0、pe03rp0针脚;

52.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe08tn0、pe08tp0、pe08rn0、pe08rp0针脚;

53.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连

接89hpes12nt12g2芯片的pe09tn0、pe09tp0、pe09rn0、pe09rp0针脚;

54.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe10tn0、pe10tp0、pe10rn0、pe10rp0针脚;

55.其中一sfp 接口的光纤连接器的rx-dat 、rx-dat-、tx-dat 、tx-dat-针脚分别连接89hpes12nt12g2芯片的pe11tn0、pe11tp0、pe11rn0、pe11rp0针脚。

56.所述qsfp 接口的数量为1个;

57.qsfp 接口采用qsfp-1888968连接器;

58.如图3、图5所示,qsfp-1888968连接器的rx1p、rx1n、rx2p、rx2n、rx3p、rx3n、rx4p、rx4n、tx1p、tx1n、tx2p、tx2n、tx3p、tx3n、tx4p、tx4n针脚分别连接89hpes12nt12g2芯片的pe16tn0、pe16tp0、pe17tn0、pe17tp0、pe18tn0、pe18tp0、pe19tn0、pe19tp0、pe16rn0、pe16rp0、pe17rn0、pe17rp0、pe18rn0、pe18rp0、pe19rn0、pe19rp0针脚。

59.还包括有用于控制交换芯片工作模式的config模块,所述config模块连接交换芯片。

60.还包括用于为交换芯片和接口供电的供电电路,供电电路如图6所示。

61.还包括时钟电路,用于为交换芯片提供时钟信号;所述时钟电路包括8t49n0041芯片,如图2、图7所示,该芯片的q0、nq0、q1、nq1针脚分别连接89hpes12nt12g2芯片的gclkp0、gclkn0、gclkp1、gclkn1针脚。

62.本技术以idt的89hpes12nt12g2为交换芯片,其最大支持12个port,12个lane,其中8个port可以灵活配置为8个x1,4个x2,2个x4,1个x8。serdes最大支持5gt/s,也就是最高支持pcie gen2交换,向下兼容gen1。上行口通过sfp 接口外引,由于pcie不能通过普通光模块加光纤传输,所以使用sfp 接口的dac(direct attach cable)无源线缆连接外部处理器,作为pcie的root设备;其他port均为下行端口,通过dac线缆连接外部的交换芯片或者其他pcie ep设备。

63.板上还有为整板器件提供电源的电源模块以及为交换芯片提供时钟的时钟模块。config模块作用是配置交换芯片,使其工作在需要的模式。

64.以上所述仅为本发明创造的较佳实施例而已,并不用以限制本发明创造,凡在本发明创造的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明创造的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。