mipi信号解码方法、装置及其芯片

技术领域

1.本发明涉及半导体集成电路设计领域,尤其涉及一种mipi信号解码方法、装置及其芯片。

背景技术:

2.对于智能终端来说,如果设备内部包括各种不同接口会给手机的设计和元器件选择带来很大的难度。为此,移动行业处理器接口(mobile industry processor interface,mipi)联盟把智能终端内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少智能终端设计的复杂程度和增加设计灵活性。例如,mipi定义了一系列的手机内部接口标准,比如摄像头接口、显示接口、射频接口、麦克风/喇叭接口等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

3.mipi的d-phy(物理层)和信号电平如图1所示,d-phy包括hs-tx(高速发送器)、lp-tx(低功耗发送器)、hs-rx(高速接收器)和lp-rx(低功耗接收器)。mipi接口传输模式分为高速(high speed,hs)模式和低功耗(low power,lp)两种模式,在hs模式下采用低压差分信号,高电平幅值典型为200mv,功耗较大,但是可以传输很高的数据速率(如数据速率为80m~1gbps);在lp模式下采用单端信号,高电平幅值典型为1.2v,数据速率很低(如数据速率小于10mbps),但是相应的功耗也很低。两种传输模式的结合保证了mipi总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

4.但是,当依赖mipi接口传输图像信号时,目前无法将mipi数据转换为能够被并行接口解析的并行数据,为此,继续一种mipi信号解码方案来解决上述问题。

技术实现要素:

5.本发明提供一种mipi信号解码方法、装置及其芯片,用以实现在依赖mipi接口传输图像信号时,将mipi数据解码为满足并行接口的并行数据。

6.第一方面,本发明提供一种mipi信号解码方法,该方法可以应用于由fpga实现的芯片,该方法包括:通过mipi接口接收来自图像传感器的原始数据转换后的两通道mipi数据,所述原始数据的数据类型为raw格式,将所述两通道的mipi数据转换为两通道的比特数据,其中,不同通道的比特数据分时复用;将每个通道的比特数据按照像素点序号的奇偶顺序分别写入不同的存储器中;当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从不同的存储器中读取所行像素的比特数据,并输出满足并行接口的并行数据。

7.本发明提供的mipi信号解码方法的有益效果在于:上述方法可以在依赖mipi接口传输图像信号时,能够实现将mipi数据转换为满足并行接口的并行数据,该设计方法应用成本低,信号传输效果好。

8.一种可能的实现方案中,所述原始数据的数据类型为raw10,raw12格式中的任意一种。

9.一种可能的实现方案中,当原始数据的数据类型为raw10格式,所述将每个通道的比特数据按照像素点序号的奇偶顺序分别写入不同的存储器中,包括:将第一通道的第零像素点和第二像素点图像的高八位比特数据均写入第一存储器中;将第二通道的第一像素点和第三像素点的高八位比特数据均写入第二存储器中,以及,将第零像素点至第三像素点的剩余比特数据的数据均写入第三存储器中;将第二通道的第四像素点和第六像素点的高八位比特数据均写入第一存储器中;将第一通道的第五像素点和第七像素点的高八位比特数据均写入第二存储器中;将第四像素点至第七像素点的剩余比特数据的数据均写入第三存储器中;依次类推,直至将奇数序号的像素点的高八位比特数据均写入第二存储器中,将偶数数序号的像素点的比特数据均写入第一存储器中,所有像素点的剩余比特数据均写入第三存储器中。

10.一种可能的实现方案中,当原始数据的数据类型为raw10格式,当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从不同的存储器中读取所行像素的比特数据,包括:按照像素点序号顺序依次从第一存储器中读出第零像素点的高八位比特数据;从第二存储器中读出第一像素点的高八位比特数据;从第一存储器中读出第二像素点的高八位比特数据,从第二存储器中读出第三像素点的高八位比特数据,从第三存储器中读出第零像素点至第三像素点的剩余比特数据;将从第三存储器中读出的各像素点的剩余比特数据与对应的像素点的高八位比特数据组成10bit数据;

11.从第一存储器中读出第四像素点的高八位比特数据,从第二存储器中读出第五像素点的高八位比特数据,从第一存储器中读出第六像素点的高八位比特数据,从第二存储器中读出第七像素点的高八位比特数据,从第一存储器中读出第四像素点至第七像素点的剩余比特数据;将从第三存储器中读出的各像素点的剩余比特数据与对应的像素点的高八位比特数据组成10bit数据;依次类推,直至数据读取完成。

12.一种可能的实现方案中,当原始数据的数据类型为raw12格式,所述将每个通道的比特数据按照像素点序号的奇偶顺序分别写入不同的存储器中,包括:

13.将第一通道的第零像素点的高八位比特数据均写入第一存储器中;

14.将第二通道的第一像素点的高八位比特数据均写入第二存储器中;

15.将第零像素点至第一像素点的剩余比特数据的数据均写入第三存储器中;

16.将第二通道的第二像素点的高八位比特数据均写入第一存储器中;

17.将第一通道的第三像素点的高八位比特数据均写入第二存储器中;

18.将第二像素点至第三像素点的剩余比特数据的数据均写入第三存储器中;

19.依次类推,直至将奇数序号的像素点的高八位比特数据均写入第二存储器中,将偶数数序号的像素点的比特数据均写入第一存储器中,所有像素点的剩余比特数据均写入第三存储器中。

20.一种可能的实现方案中,当原始数据的数据类型为raw12格式,从第一存储器中读出第零像素点的高八位比特数据;从第二存储器中读出第一像素点的高八位比特数据;从第三存储器中读出第零像素点至第一像素点的剩余比特数据;将从第三存储器中读出的第零像素点和第一像素点的剩余比特数据与对应的像素点的高八位比特数据组成12比特数据;

21.从第一存储器中读出第二像素点的高八位比特数据,从第二存储器中读出第三像

素点的高八位比特数据,从第三存储器中读出第二像素点至第三像素点的剩余比特数据;将从第三存储器中读出的第一像素点和第二像素点的剩余比特数据与对应的像素点的高八位比特数据组成12比特数据;

22.依此类推,直至整行的像素点数据读取完成。

23.一种可能的实现方案中,当原始数据的数据类型为raw14格式,所述将每个通道的比特数据按照像素点序号的奇偶顺序分别写入不同的存储器中,包括:

24.将第一通道的第零像素点和第二像素点的高八位比特数据均写入第一存储器中;

25.将第二通道的第一像素点和第三像素点的高八位比特数据均写入第二存储器中;

26.将第零像素点至第三像素点的剩余比特数据的数据均写入第三存储器中;

27.将第二通道的第四像素点和第六像素点的高八位比特数据均写入第一存储器中;

28.将第一通道的第五像素点和第七像素点的高八位比特数据均写入第二存储器中;

29.将第四像素点至第七像素点的剩余比特数据的数据均写入第三存储器中;

30.依次类推,直至将奇数序号的像素点的高八位比特数据均写入第二存储器中,将偶数数序号的像素点的比特数据均写入第一存储器中,所有像素点的剩余比特数据均写入第三存储器中。

31.一种可能的实现方案中,当原始数据的数据类型为raw14格式,所述按照像素点序号顺序依次从不同的存储器中读取数据,包括:

32.从第一存储器中读出第零像素点的高八位比特数据;从第二存储器中读出第一像素点的高八位比特数据;从第一存储器中读出第二像素点的高八位比特数据,从第二存储器中读出第三像素点的高八位比特数据,从第三存储器中读出第零像素点至第三像素点的剩余比特数据;将从第三存储器中读出的第零像素点至第三像素点的剩余比特数据与对应的像素点的高八位比特数据组成14比特数据;

33.从第一存储器中读出第四像素点的高八位比特数据,从第二存储器中读出第五像素点的高八位比特数据,从第一存储器中读出第六像素点的高八位比特数据,从第二存储器中读出第七像素点的高八位比特数据,从第一存储器中读出第四像素点至第七像素点的剩余比特数据;将从第三存储器中读出的第四像素点至第七像素点的剩余比特数据与对应的像素点的高八位比特数据组成14比特数据;依此类推,直至整行的像素点数据读取完成。

34.第二方面,本发明实施例还提供一种mipi信号解码装置,该装置包括执行上述第一方面的任意一种可能的设计的方法的模块/单元。这些模块/单元可以通过硬件实现,也可以通过硬件执行相应的软件实现。

35.第三方面,本发明实施例提供一种mipi信号解码芯片,包括mipi接口,该mipi接口,用于接收来自图像传感器的mipi数据;其中,存储器用于存储一个或多个程序;当存储器存储的一个或多个程序被处理器执行时,使得该芯片能够实现上述第一方面的任意一种可能的设计的方法。

36.第四方面,本发明实施例中还提供一种可读存储介质,可读存储介质包括程序,当程序在芯片上运行时,使得芯片执行上述任一方面的任意一种可能的设计的方法。

37.第五方面,本发明实施例还提供一种程序产品,当程序产品在芯片上运行时,使得芯片执行上述任一方面的任意一种可能的设计的方法。

38.关于上述第二方面至第五方面的有益效果可以参见上述第一方面中的描述,不再

重复赘述。

附图说明

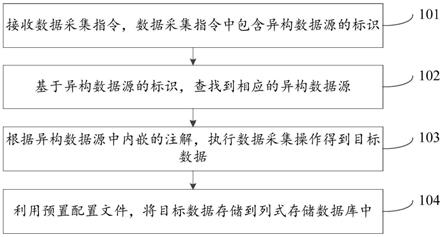

39.图1为本发明实施例提供的一种mipi的物理层和信号电平示意图;

40.图2为本发明实施例提供的一种通信系统;

41.图3为本发明实施例提供的一种mipi信号解码方法流程示意图;

42.图4为本发明实施例提供的一种两通道的比特数据示意图;

43.图5为本发明实施例提供的一种raw10格式的比特数据流中的存储格式示意图;

44.图6为本发明实施例提供的一种raw10格式的比特数据流读取方式示意图;

45.图7为本发明实施例提供的一种raw14格式的比特数据流中的存储格式示意图;

46.图8为本发明实施例提供的一种raw14格式的比特数据流读取方式示意图;

47.图9为本发明实施例提供的一种raw12格式的比特数据流中的存储格式示意图;

48.图10为本发明实施例提供的一种raw12格式的比特数据流读取方式示意图;

49.图11为本发明实施例提供的另一种mipi信号解码方法流程示意图;

50.图12为本发明实施例提供的一种四通道的比特数据示意图;

51.图13为本发明实施例提供的一种终端设备结构示意图。

具体实施方式

52.下面将结合附图,对本发明中的技术方案进行描述。

53.以下先对下文中涉及的部分用语进行解释说明,以便于本领域技术人员理解。

54.(1)移动产业处理器接口(mobile industry processor interface,mipi)联盟是mipi联盟发起的为移动应用处理器制定的开放标准和一个规范。

55.也就是说,mipi不只是一个联盟也是一套接口协议规范的名称。它下辖不同的工作组(work group),以满足移动终端各个子系统的不同需求。不同的工作组负责制定具体的协议,并分别针对不同的硬件设备定义了一套移动设备内部接口标准,比如摄像头串行接口、显示串行接口、射频接口等。

56.(2)raw图像是cmos或ccd图像感应器将捕捉到的光源信号转化为数字信号的原始数据。raw文件是一种记录了数码相机传感器的原始信息,同时记录了由相机拍摄所产生的一些元数据(metadata),如iso的设置、快门速度、光圈值、白平衡等的文件。raw是未经处理、也未经压缩的格式,可以把raw概念化为“原始图像编码数据”或更形象的称为“数字底片”。

57.(3)现场可编程门阵列(field programmable gate array,fpga),是由许多的逻辑单元构成的逻辑器件,其中逻辑单元包括门、查找表和触发器,它具有丰富硬件资源、强大并行处理能力和灵活可重配置能力,在数据处理、通信、网络等很多领域得到了越来越多的广泛应用。fpga是在pal、gal、cpld等可编程器件的基础上进一步发展的产物,它是作为专用芯片(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

58.本发明提供的基于fpga所实现的mipi信号解码芯片来解码mipi信号的方法可以先将mipi数据转换为比特数据,然后再将比特数据分类存储到不同的存储器中,之后按照

每行像素点序号顺序依次从不同的存储器中读取数据,就可以输出满足并行接口的并行数据,所以可以实现在依赖mipi接口传输图像信号时,能够实现将mipi数据转换为满足并行接口的并行数据,该设计方法应用成本低,信号传输效果好。

59.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行描述。其中,在本发明实施例的描述中,以下实施例中所使用的术语只是为了描述特定实施例的目的,而并非旨在作为对本发明的限制。如在本发明的说明书和所附权利要求书中所使用的那样,单数表达形式“一种”、“所述”、“上述”、“该”和“这一”旨在也包括例如“一个或多个”这种表达形式,除非其上下文中明确地有相反指示。还应当理解,在本发明以下各实施例中,“至少一个”、“一个或多个”是指一个或两个以上(包含两个)。术语“和/或”,用于描述关联对象的关联关系,表示可以存在三种关系;例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a、b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。

60.在本说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本发明的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。术语“连接”包括直接连接和间接连接,除非另外说明。“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。

61.在本发明实施例中,“示例性地”或者“例如”等词用于表示作例子、例证或说明。本发明实施例中被描述为“示例性地”或者“例如”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用“示例性地”或者“例如”等词旨在以具体方式呈现相关概念。

62.如图2所示,为适用于本发明实施例的通信系统,该系统包括图像传感器10、芯片20。其中,图像传感器10通过mipi接口向芯片20发送mipi数据。mipi数据除了包括mipi数据(如mipi data0、mipi data1、mipi data2和mipi data3),还包括mipi clk(时钟)信息。该mipi数据可以为来自显示屏接口的数字语音内插(digital-speech interpolation,dsi)信号或者来自摄像头接口的互补金属氧化物半导体图像传感器(cmos sensor interface,csi)信号,也可以是来自于移动终端其它mipi接口的信号,该mipi接口410可以为gtx、gth等接口。

63.芯片20中包括mipi接口,用于接收来自图像传感器的mipi数据。参见图2,该芯片20包括mipi解码模块201和dvp数据生成模块202。其中,mipi解码模块201连接mipi接口并且用于解码经过编码的mipi信号(mipi信号包括数据和恢复时钟信息),该mipi解码模块201可以为8b/10b解码器、64b/66b解码器或者曼彻斯特解码器。在一个实施例中,mipi解码模块201通过内置锁相环(phase locked loop,pll)电路的专用时钟恢复芯片恢复时钟信息,恢复后的时钟信息为后续电路提供时钟源及数据采样基准。数字视频端口(digital video port,dvp)数据生成模块202,用于生成并行数据。图像信号处理器30,用于接收并行数据,然后进行后续的降噪等处理。

64.本实施例中,因图像传感器10输出的mipi数据是差分信号,芯片20可以实现将接收的来自图像传感器10的串行数据转换为满足并行接口的并行数据。

65.上述芯片20也可以替换为包含asic芯片的终端设备或者包含fpga的终端设备,又或者是包含asic/fpga的嵌入式系统。本发明中的包含asic/fpga的终端设备也可以称为用户设备(user equipment,ue)、接入终端、用户单元、用户站、移动站、移动台、远方站、远程终端、移动设备、用户终端、终端、无线通信设备、用户代理或用户装置。本发明的实施例中的终端设备可以是手机(mobile phone)、平板电脑(pad)、智能打印机、火车探测器、加油站探测器、带无线收发功能的电脑、虚拟现实(virtual reality,vr)终端设备、增强现实(augmented reality,ar)终端设备、工业控制(industrial control)中的无线终端、无人驾驶(self driving)中的无线终端、远程医疗(remote medical)中的无线终端、智能电网(smart grid)中的无线终端、运输安全(transportation safety)中的无线终端、智慧城市(smart city)中的无线终端、智慧家庭(smart home)中的无线终端等等。本发明的实施例对应用场景不做限定。

66.应理解,图2仅为便于理解而示例的简化示意图,该通信系统中还可以包括其他图像信号处理器或者还可以包括其他终端设备,图2中未予以画出。

67.本发明实施例提供的一种mipi信号解码方法,该方法可以由图2所示的通信系统中的芯片20来执行。应理解,本发明中,由芯片20执行的步骤也可以具体由芯片20的一个或多个模块或部件执行。如图3所示,示出本发明实施例提供的一种mipi信号解码方法,该方法包括:

68.s301,通过所述mipi接口接收来自图像传感器的原始数据转换后两通道的mipi数据,所述原始数据的数据类型为raw格式。

69.该步骤中,一种可能的实施方式中,mipi数据的raw格式可以raw10、raw12或raw14格式中的任意一种。

70.s302,将所述两通道的mipi数据转换为两通道的比特数据,其中,不同通道的比特数据分时复用。

71.将所述两通道的mipi数据转换后的两通道的比特数据如图4所示。从图4中可见,两通道的比特数据分别为lane1和lane2,其中,lane1包括byte0、byte2、byte4、...、byteb-6、byteb-4和byteb-2。lane2包括byte1、byte3、byte5、...、byteb-5、byteb-3和byteb-1。

72.s303,将每个通道的比特数据按照像素点的奇偶顺序分别写入不同的存储器中。

73.s304,当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从不同的存储器中读取所行像素的比特数据,并输出满足并行接口的并行数据。

74.场景一

75.示例性地,当原始数据的数据类型为raw10格式,比特数据流中的存储格式如图5所示,其中,p0[9:2]至p

2n 1

[9:2]分别代表第0像素点至2n 1像素点的高八位比特数据,p

x0

[1:0]代表第零像素点至第三像素点的低两位比特数据、p

x1

[1:0]代表第四像素点至第七像素点的低两位比特数据,依次类推,代表第2n 1像素点至第2n-2像素点的低两位比特数据。

[0076]

之后,如图6所示,通过第一时钟将第一通道(lane1)的p0[9:2]、p2[9:2]均写入第

一存储器中;通过第二时钟将第二通道(lane2)的p1[9:2]、p3[9:2]均写入第二存储器中;通过第三时钟将第零像素点至第三像素点的p

x0

[1:0]均写入第三存储器中。之后重复通过第一时钟将第二通道的p4[9:2]、p6[9:2]均写入第一存储器中;通过第二时钟将第一通道的p5[9:2]、p7[9:2]均写入第二存储器中;将p

x1

[1:0]均写入第三存储器中;依次类推,直至将偶数数序号的像素点的比特数据均写入第一存储器中,将奇数序号的像素点的高八位比特数据均写入第二存储器中,所有像素点的低两位比特数据均写入第三存储器中。

[0077]

之后,在数据读取阶段,当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从第一存储器中读取p0[9:2]、从第二存储器中读取p1[9:2],从第一存储器中读取p2[9:2]、从第二存储器中读取p3[9:2],另外,在读p0[9:2]同时从第三存储器中读取p

x0

[1:0],这样对p0[9:2]和p

x0

[1:0]中的两比特数据进行拼接,可以得到10bit数据。之后,依次类推,读取该行所有像素点的比特数据,并输出满足并行接口的并行数据。

[0078]

场景二

[0079]

示例性地,当原始数据的数据类型为raw14格式,比特数据流中的存储格式如图7所示,其中,p0[13:6]至p

2n 1

[13:6]分别代表第0像素点至2n 1像素点的高八位比特数据,p

x0

[5:0]、p

x1

[5:0]和p

x2

[5:0]代表第零像素点至第三像素点的低六位比特数据、p

x3

[5:0]、p

x4

[5:0]和p

x5

[5:0]代表第四像素点至第七像素点的低六位比特数据,依次类推,代表第2n 1像素点至第2n-2像素点的低六位比特数据。

[0080]

之后,如图8所示,通过第一时钟将第一通道(lane1)的p0[13:6]、p2[13:6]均写入第一存储器中;通过第二时钟将第二通道(lane2)的p1[13:6]、p3[13:6]均写入第二存储器中;通过第三时钟将第零像素点至第三像素点的p

x0

[5:0]、p

x1

[5:0]和p

x2

[5:0]均写入第三存储器中。之后重复通过第一时钟将第二通道的p4[13:6]、p6[13:6]均写入第一存储器中;通过第二时钟将第一通道的p5[13:6]、p7[13:6]均写入第二存储器中;将第四像素点至第七像素点的p

x3

[5:0]、p

x4

[5:0]和p

x5

[5:0]均写入第三存储器中;依次类推,直至将偶数数序号的像素点的比特数据均写入第一存储器中,将奇数序号的像素点的高八位比特数据均写入第二存储器中,所有像素点的低六位比特数据均写入第三存储器中。

[0081]

当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从第一存储器中读取p0[13:6]、从第二存储器中读取p1[13:6],从第一存储器中读取p2[13:6]、从第二存储器中读取p3[13:6],另外,在读p0[13:6]同时从第三存储器中读取p

x0

[5:0],这样对p0[13:6]和p

x0

[5:0]进行拼接,可以得到14bit数据。之后,依次类推,读取该行所有像素的比特数据,并输出满足并行接口的并行数据。

[0082]

场景三

[0083]

示例性地,当原始数据的数据类型为raw12格式,比特数据流中的存储格式如图9所示,其中,p0[11:4]至p

2n 1

[11:4]分别代表第0像素点至2n 1像素点的高八位比特数据,p

x0

[3:0]代表第零像素点至第一像素点的低四位比特数据、p

x1

[3:0]代表第二像素点至第三像素点的低四位比特数据,依次类推,p

xn

[3:0]代表第2n 1像素点至第2n像素点的低四位比特数据。

[0084]

之后,如图10所示,通过第一时钟将第一通道(lane1)的p0[11:4]写入第一存储器中;通过第二时钟将第二通道(lane2)的p1[11:4]写入第二存储器中;通过第三时钟将第零

像素点至第三像素点的低四位比特数据的数据p

x0

[3:0]、写入第三存储器中。之后重复通过第一时钟将第二通道的p2[11:4]写入第一存储器中;通过第二时钟将第一通道的p3[11:4]写入第二存储器中;将第二像素点至第三像素点的低四位比特数据的数据p

x1

[3:0]写入第三存储器中;依次类推,直至将偶数数序号的像素点的比特数据均写入第一存储器中,将奇数序号的像素点的高八位比特数据均写入第二存储器中,所有像素点的低四位比特数据均写入第三存储器中。

[0085]

当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从第一存储器中读取p0[11:4]、从第二存储器中读取p1[11:4],另外,在读p0[11:4]同时从第三存储器中读取p

x0

[3:0],这样对p0[11:4]和p

x0

[3:0]进行拼接,可以得到12bit数据。之后,依次类推,读取该行所有像素的比特数据,并输出满足并行接口的并行数据。

[0086]

上述方法中,因mipi信号在高速传输模式下为低压差分信号,具有抗干扰性强的优点,在低功耗传输模式下为单端信号,具有功耗低的优点。芯片的mipi接口可以正确将在高速传输模式下的mipi信号解码为能够被并行解析的并行数据。值得说明的是,针对数据类型为raw8格式或raw16格式的原始数据,可以不执行上述方法,按顺序读取即可。

[0087]

一般地,一帧数据由1080行组成,一行由1920个像素点组成,这样,mipi接口接收了1080行串行有效数据后,就可以得到一帧数据,然后按照上述方法依次把串行有效数据最后转成类似于数字视频端口(digital video port)形式的并行数据信号,以便于数字视频显示设备正确显示图像。这样,在依赖mipi接口传输图像信号时,能够实现将mipi数据转换为满足并行接口的并行数据,该设计方法应用成本低,信号传输效果好。

[0088]

本发明实施例还提供的另一种mipi信号解码方法,该方法可以与上述方法的主要区别在于mipi接口接收的是四通道的mipi数据,如图11所示,该方法包括:

[0089]

s1101,通过所述mipi接口接收来自图像传感器的原始数据转换后的四通道mipi数据,所述原始数据的数据类型为raw格式。

[0090]

该步骤中,一种可能的实施方式中,mipi数据的raw格式可以为raw10、raw12或raw14格式中的任意一种。

[0091]

s1102,将所述四通道的mipi数据转换为四通道的比特数据,其中,不同通道的比特数据分时复用。

[0092]

将所述四通道的mipi数据转换后的四通道的比特数据如图12所示。从图12中可见,四通道的比特数据分别为lane1、lane2、lane3和lane4。

[0093]

s1103,将每个通道的比特数据按照像素点的奇偶顺序分别写入不同的存储器中。

[0094]

s1104,当一行像素点的比特数据写入完成后,按照像素点序号顺序依次从不同的存储器中读取所行像素的比特数据,并输出满足并行接口的并行数据。

[0095]

针对不同raw格式的原始数据,数据的存储方式和读取方式可以参照上述场景一至场景五所述的方式,在此不再一一举例示出。

[0096]

值得说明的是,当mipi接口接收的是三通道mipi数据时,针对不同raw格式的原始数据,数据的存储方式和读取方式也可以参照上述场景一至场景五所述的方式,在此不再一一举例示出。

[0097]

图13示意了一种终端设备1300的结构示意图。终端设备1300可用于实现上述方法实施例中描述的方法,可以参见上述方法实施例中的说明。所述终端设备1300可以是网络

设备(如基站)、终端设备或者其它设备等。

[0098]

所述终端设备1300包括一个或多个处理器1301。所述处理器1301可以指代上述芯片,例如可以是基带处理器、或中央处理器。基带处理器可以用于对通信协议以及通信数据进行处理,中央处理器可以用于对通信装置(如,基站、终端、或芯片等)进行控制,执行软件程序,处理软件程序的数据。

[0099]

可选的,一种可能的实施方式中,处理器1301也可以包括指令1303,所述指令可以在所述处理器上被运行,使得所述终端设备1300执行上述方法实施例中描述的方法。

[0100]

在又一种可能的实施方式,所述终端设备1300中可以包括一个或多个存储器1302,其上存有指令1304,所述指令可在所述处理器上被运行,使得所述终端设备1300执行上述方法实施例中描述的方法。可选的,所述存储器中还可以存储有数据。可选的处理器中也可以存储指令和/或数据。例如,所述一个或多个存储器1302可以存储上述实施例中所描述的对应关系,或者上述实施例中所涉及的相关的参数或表格等。所述处理器和存储器可以单独设置,也可以集成在一起。

[0101]

在一种可能的实施方式,所述终端设备1300还可以包括通信接口1305以及天线1306。所述处理器1301可以称为处理单元,对通信装置(终端或者基站)进行控制。所述通信接口1305可以称为收发机、收发电路、或者收发器等,用于通过天线1306实现通信装置的收发功能。

[0102]

应理解,在本发明实施例中的处理器可以是中央处理单元(central processing unit,cpu),该处理器还可以是其他通用处理器、数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现成可编程门阵列(field programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。

[0103]

本发明实施例还提供了一种可读介质,其上存储有程序,该程序被芯片执行时实现上述任一方法实施例所述方法。

[0104]

本发明实施例还提供了一种程序产品,该程序产品被芯片执行时实现上述任一方法实施例所述方法。

[0105]

本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、或者软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。

[0106]

所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的系统、装置和单元的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

[0107]

在本发明所提供的几个实施例中,应该理解到,所揭露的系统、装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦

合或通信连接,可以是电性,机械或其它的形式。

[0108]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0109]

另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

[0110]

所述功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该软件产品存储在一个存储介质中,包括若干指令用以使得一台设备(可以是个人,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

[0111]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

[0112]

总之,以上所述仅为本发明技术方案的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。