1.本公开涉及芯片技术领域,尤其涉及一种芯片、加速卡以及电子设备、数据处理方法。

背景技术:

2.近年来,神经网络广泛应用于图像处理、故障诊断、视频安防等各种领域中。相关技术中,一般需要通过host端的主处理器(例如,host cpu)与加速卡进行配合来实现神经网络的训练/推理,因而在ai训练/推理的过程中存在host cpu对加速卡的大量访存操作,且大量数据需要在加速卡的内存与host cpu之间传输,导致加速卡的内存压力与host cpu的数据处理压力都较大。

技术实现要素:

3.第一方面,本公开实施例提供一种芯片,所述芯片包括:控制单元、片上缓存单元和处理单元,所述处理单元包括第一处理子单元和第二处理子单元;所述控制单元,用于将神经网络的网络参数调度到所述第一处理子单元;所述第一处理子单元,用于基于调度到本处理单元的网络参数对待处理视频帧进行第一处理,得到第一视频帧,并将所述第一视频帧输出至所述片上缓存单元进行缓存;所述第二处理子单元,用于从所述片上缓存单元中读取所述第一视频帧,对读取的所述第一视频帧进行第二处理,得到第二视频帧并输出。

4.在一些实施例中,所述处理单元还包括第三处理子单元,用于对所述待处理视频帧进行第三处理后输出至所述片上缓存单元进行缓存;所述第一处理子单元用于从所述片上缓存单元中读取经第三处理的所述待处理视频帧,并对经第三处理的所述待处理视频帧进行第一处理。

5.在一些实施例中,所述芯片还包括:视频解码单元,所述视频解码单元用于在所述控制单元的控制下,对输入视频进行视频解码,得到所述待处理视频帧。

6.在一些实施例中,所述控制单元还用于基于第一预设条件从所述待处理视频帧中筛选出第一目标视频帧;所述芯片还包括:第一图像编码单元,用于对所述第一目标视频帧进行图像压缩,压缩后的第一目标视频帧用于输出至外部处理单元。

7.在一些实施例中,所述控制单元还用于基于第二预设条件从所述第二视频帧中筛选出第二目标视频帧;所述芯片还包括:第二图像编码单元,用于对所述第二目标视频帧进行图像压缩,压缩后的第二目标视频帧用于输出至外部处理单元。

8.在一些实施例中,所述处理单元的数量大于1,第i 1个处理单元中的第一子单元用于读取第i个处理单元中的第二处理子单元输出的第二视频帧,并将所述第i个处理单元中的第二处理子单元输出的第二视频帧作为待处理视频帧进行所述第一处理,i为正整数。

9.在一些实施例中,所述神经网络包括多个子网络,各个子网络的网络参数均存储在加速卡的内存单元中;所述控制单元用于从所述内存单元中将神经网络的网络参数调度到所述第一处理子单元。

10.在一些实施例中,第i个处理单元采用所述神经网络包括的第i个子网络执行所述第一处理。

11.在一些实施例中,所述内存单元包括多个分区;所述多个子网络中的至少两个子网络的网络参数被存储在不同的分区中。

12.第二方面,本公开实施例提供一种加速卡,所述加速卡包括:内存单元,用于存储神经网络的网络参数;以及任一实施例所述的芯片。

13.第三方面,本公开实施例提供一种电子设备,所述电子设备包括:第二方面所述的加速卡;以及外部处理单元,用于将所述神经网络的网络参数输出至所述内存单元。

14.第四方面,本公开实施例提供一种数据处理方法,应用于本公开任一实施例所述的芯片,所述方法包括:所述控制子单元将神经网络的网络参数调度到所述第一处理子单元;所述第一处理子单元基于调度到本处理单元的网络参数对待处理视频帧进行第一处理,得到第一视频帧,并将所述第一视频帧输出至所述片上缓存单元进行缓存;所述第二处理子单元从所述片上缓存单元中读取所述第一视频帧,对读取的所述第一视频帧进行第二处理,得到第二视频帧并输出。

15.在一些实施例中,所述处理单元还包括第三处理子单元,用于对所述待处理视频帧进行第三处理后输出至所述片上缓存单元进行缓存;所述方法还包括:所述第一处理子单元从所述片上缓存单元中读取经第三处理的所述待处理视频帧,并对经第三处理的所述待处理视频帧进行第一处理。

16.在一些实施例中,所述方法还包括:所述控制单元控制视频解码单元对输入视频进行视频解码,得到所述待处理视频帧。

17.在一些实施例中,所述方法还包括:所述控制单元基于第一预设条件从所述待处理视频帧中筛选出第一目标视频帧,并将所述第一目标视频帧输出至第一图像编码单元进行图像压缩,压缩后的第一目标视频帧用于输出至外部处理单元。

18.在一些实施例中,所述方法还包括:所述控制单元基于第二预设条件从所述第二视频帧中筛选出第二目标视频帧,并将所述第二目标视频帧输出至第二图像编码单元进行图像压缩,压缩后的第二目标视频帧用于输出至外部处理单元。

19.在一些实施例中,所述处理单元的数量大于1,第i 1个处理单元中的第一子单元用于读取第i个处理单元中的第二处理子单元输出的第二视频帧,并将所述第i个处理单元中的第二处理子单元输出的第二视频帧作为待处理视频帧进行所述第一处理,i为正整数。

20.在一些实施例中,所述神经网络包括多个子网络,各个子网络的网络参数均存储在加速卡的内存单元中;所述方法还包括:所述控制单元从所述内存单元中将神经网络的网络参数调度到所述第一处理子单元。

21.在一些实施例中,第i个处理单元采用所述神经网络包括的第i个子网络执行所述第一处理。

22.在一些实施例中,所述内存单元包括多个分区;所述多个子网络中的至少两个子网络的网络参数被存储在不同的分区中。

23.第五方面,本公开实施例提供一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现本公开任一实施例所述的芯片中的控制单元执行的方法。

24.本公开实施例通过芯片内部的控制单元实现对网络参数的调度,并通过芯片内部

的第二处理子单元实现对神经网络处理后的第一视频帧进行的后处理。这样,实现了将host cpu的调度及后处理下沉到芯片,有效减少了host cpu对加速卡的内存访问频率,减小了host cpu的数据处理压力;此外,本公开采用片上缓存单元来缓存神经网络处理后的第一视频帧,无需将第一视频帧存储到加速卡的内存单元中,从而减少了加速卡的内存占用量,实现了加速卡的内存优化,减小了加速卡的内存压力。

25.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。

附图说明

26.此处的附图被并入说明书中并构成本公开的一部分,这些附图示出了符合本公开的实施例,并与说明书一起用于说明本公开的技术方案。

27.图1是本公开实施例的芯片的示意图;

28.图2是相关技术中host cpu与加速卡之间的交互过程的示意图;

29.图3是本公开实施例的host cpu与加速卡之间的交互过程的示意图;

30.图4是相关技术中的ai推理过程的时序图;

31.图5是本公开实施例的加速卡的硬件结构示意图;

32.图6是本公开实施例的ai推理过程的时序图;

33.图7是本公开根据一示例性实施例示出的一种加速卡的示意图;

34.图8是本公开根据一示例性实施例示出的加速卡数据传输过程的示意图;

35.图9是本公开根据一示例性实施例示出的一种电子设备的示意图;

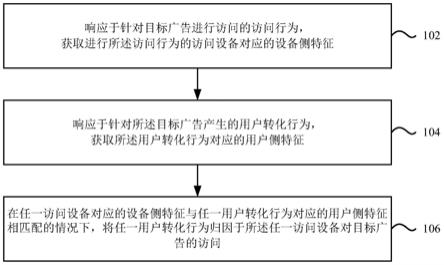

36.图10是本公开根据一示例性实施例示出的一种数据处理方法的示意图。

具体实施方式

37.这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本公开相一致的所有实施方式。相反,它们仅是与如所附权利要求书中所详述的、本公开的一些方面相一致的装置和方法的例子。

38.在本公开使用的术语是仅仅出于描述特定实施例的目的,而非旨在限制本公开。在本公开和所附权利要求书中所使用的单数形式的“一种”、“所述”和“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。还应当理解,本文中使用的术语“和/或”是指并包含一个或多个相关联的列出项目的任何或所有可能组合。另外,本文中术语“至少一种”表示多种中的任意一种或多种中的至少两种的任意组合。

39.应当理解,尽管在本公开可能采用术语第一、第二、第三等来描述各种信息,但这些信息不应限于这些术语。这些术语仅用来将同一类型的信息彼此区分开。例如,在不脱离本公开范围的情况下,第一信息也可以被称为第二信息,类似地,第二信息也可以被称为第一信息。取决于语境,如在此所使用的词语“如果”可以被解释成为“在

……

时”或“当

……

时”或“响应于确定”。

40.近年来,神经网络广泛应用于图像处理、故障诊断、视频安防等各种领域中,在神经网络技术领域,通过样本数据对神经网络模型进行训练的过程可以称为ai训练,利用神

经网络算法对对象进行处理的过程可以称为ai推理。相关技术中,终端一般借助更适合执行运算任务的加速卡来完成ai训练/推理。然而,在ai训练/推理的过程中存在host cpu对加速卡的大量访存操作,且大量数据需要在加速卡的内存与host cpu之间传输,导致加速卡的内存压力与host cpu的数据处理压力都较大。

41.基于此,本公开实施例提供一种芯片,用于解决上述问题。

42.为了使本技术领域的人员更好的理解本公开实施例中的技术方案,并使本公开实施例的上述目的、特征和优点能够更加明显易懂,下面结合附图对本公开实施例中的技术方案作进一步详细的说明。

43.如图1所示,是本公开实施例的芯片的示意图。所述芯片包括:

44.控制单元101、片上缓存单元102和处理单元103,所述处理单元103包括第一处理子单元1031和第二处理子单元1032;

45.所述控制单元101用于将神经网络的网络参数调度到所述第一处理子单元1031;

46.所述第一处理子单元1031用于基于调度到本处理单元的网络参数对待处理视频帧进行第一处理,得到第一视频帧,并将所述第一视频帧输出至所述片上缓存单元102进行缓存;

47.所述第二处理子单元1032用于从所述片上缓存单元102中读取所述第一视频帧,对读取的所述第一视频帧进行第二处理,得到第二视频帧并输出。

48.在本公开实施例中,神经网络的网络参数可以存储在加速卡的内存单元中,所述控制单元101可以从所述内存单元中将神经网络的网络参数调度到所述第一处理子单元1031。后续实施例均以ai加速卡为例进行说明。ai加速卡是一种专门设计的用来加速ai算法执行的处理器产品,该ai加速卡可以是包括用于进行ai运算的芯片、通信接口等硬件模块的电路板,该用于进行ai运算的芯片可以是gpu(graphics processing unit,图形处理器)、fpga(field programmable gate array,现场可编程逻辑门阵列)、asic(application specific integrated circuit,专用集成电路)中的任意一种,也可以是其他类型的芯片,本公开对此不作限制。ai加速卡可以插设在插槽中并通过通信接口,例如pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)接口与host cpu进行通信,当然,在其他实施例中,ai加速卡也可以通过其他类型的通信接口,如qpi(quick path interconnect,快速通道互联)接口,作为与host cpu之间的交互通道。

49.上述内存单元可以是dram(dynamic random access memory,动态随机存取存储器)或sdram(synchronous dynamic random access memory,同步动态随机存取存储器),也可以是其他类型的存储器,本公开对此不作限制。在本实施例中,该内存单元用于存储神经网络的网络参数,该网络参数可以包括算子(例如,加法算子、乘法算子等)和算子进行运算所需的参数。

50.上述处理单元103是ai加速卡中执行ai运算任务的功能模块,可以称为运算单元(computing unit,cu)。所述处理单元可以包括第一处理子单元和第二处理子单元,第一处理子单元中可以包括执行加法运算的子单元、执行乘法运算的子单元、执行卷积乘运算的子单元等多个子单元,这些子单元可以称为可重构簇,这些可重构簇可以组合起来,通过重构的方式形成不同的运算通路去执行不同的任务。第一处理子单元1031基于调度到本处理单元的神经网络的网络参数对待处理视频帧进行第一处理,该第一处理的具体内容可以根

据该神经网络所实现的功能来确定,例如,一个神经网络可以用于对待处理视频帧进行人脸分割,则基于该神经网络所进行的第一处理可以是指从待处理视频帧中分割出人脸图像,所述第一视频帧可以是分割出的所述人脸图像。需要说明的是,本实施例的方案可用于神经网络的训练阶段,也可以用于神经网络的推理阶段,后续内容以神经网络的推理阶段为例进行描述。

51.在本实施例中,第一处理子单元1031基于神经网络的网络参数对待处理视频帧进行第一处理的操作是在控制单元的控制调度下执行的。可选地,该控制单元可以是mcu(microcontroller unit,微控制单元)。也就是说,不同于相关技术中单纯作为slave设备的ai加速卡,本实施例通过在ai加速卡中增设mcu,用以替代host cpu来对神经网络进行控制调度,从而减少host cpu对ai加速卡的内存访问频率。当然,在其他实施例中,该控制单元也可以是arm、risc-v、powerpc等架构的处理器芯片。在一些实施例中,所述芯片还包括视频解码单元,所述视频解码单元用于在所述控制单元的控制下,对输入视频进行视频解码,得到所述待处理视频帧。

52.在实际应用中,经常需要对神经网络处理后的视频帧进行加工处理,如裁剪、锐化、缩放等等,这些加工处理称为后处理。相关技术中,由于gpu或ai加速卡受限于硬件条件不支持通用性的处理操作,因此,后处理过程一般是由host cpu来实现的。在这一过程中,需要将神经网络处理后的视频帧先输出至ai加速卡的内存单元中进行存储,再由host cpu从ai加速卡的内存单元中读取处理后的视频帧并进行后处理,然后将经过后处理的视频帧返回至ai加速卡的内存中,由ai加速卡继续进行其他处理。可以看出,上述过程产生了较多的访存操作。在神经网络包括多个子网络,且每个子网络的输出结果都需要进行后处理的情况下,或者在神经网络需要对输入的视频帧进行多次处理,且每次处理得到的输出结果都需要进行后处理的情况下,随着子网络数量的增加或者神经网络对输入的视频帧进行的总处理次数的增加,访存次数以及host cpu进行的后处理次数也会增加,这会同时增加ai加速卡的内存压力以及host cpu的数据处理压力。

53.而本实施例通过在ai加速卡中增设第二处理子单元,替代host cpu来执行模型后处理任务,从而能将host cpu上执行的后处理操作下沉到芯片,从而减轻了host cpu的数据处理压力,同时也减少了host cpu对ai加速卡内存的访问频率,减轻了ai加速卡的内存单元的数据传输压力。此外,本公开采用片上缓存单元来缓存神经网络处理后的第一视频帧,无需将第一视频帧存储到ai加速卡的内存单元中,从而减少了ai加速卡的内存占用量,实现了ai加速卡的内存优化,减小了ai加速卡的内存的数据存储压力。所述的第二处理可以包括裁剪处理、锐化处理、旋转处理、缩放处理、透明处理、nms(non-maximum suppression,非极大值抑制)等图像处理中的至少一种。

54.为了便于理解本公开实施例的技术效果,下面结合附图,对相关技术以及本公开实施例中host cpu与加速卡之间的交互过程分别进行说明。如图2所示,以ai加速卡为例,是相关技术中host cpu与ai加速卡之间的交互过程的示意图。假设需要通过神经网络对输入的视频帧进行n(n为正整数)次处理,host cpu通过视频解码模块对视频码流进行解码后,将解码后的视频帧pic1传递给ai加速卡的内存单元;ai加速卡中的模型推理模块基于神经网络对视频帧pic1进行处理,并将处理后的视频帧pic1a存于内存单元中;host cpu从ai加速卡的内存单元中读取视频帧pic1a,以通过模型后处理单元进行模型后处理;之后,

host cpu将经模型后处理的视频帧pic1b传递给ai加速卡的内存,由ai加速卡基于神经网络对视频帧pic1b再次进行处理;以此类推,直至host cpu获取到想要的结果(图中记为pic1n)。在这一过程中,神经网络处理次数越多,则对ai加速卡的访存操作次数也越多。

55.以ai加速卡为例,如图3所示,是本公开实施例的host cpu与ai加速卡之间的交互过程的示意图。host cpu通过pcie或以太网接口将视频码流传递给ai加速卡的内存单元;视频解码单元从内存单元中读取视频码流并进行解码,得到视频帧pic2,ai加速卡的第一处理子单元基于神经网络对视频帧pic2进行处理并将处理后的视频帧pic2a传递给片上缓存单元,第二处理子单元从片上缓存单元中获取视频帧pic2a,对视频帧pic2a进行模型后处理,并将经模型后处理的视频帧pic2b再传递给第一处理子单元;重复上述过程,直至第二处理子单元输出所需的视频帧pic2n,并将视频帧pic2n输出至内存单元,由内存单元将视频帧pic2n回传给host cpu。在这一过程中,无论神经网络处理了多少次,host cpu只需要将待处理视频帧传递给ai加速卡的内存以及从ai加速卡的内存读取最后的ai推理结果即可,访存频率较低,host cpu的处理压力以及host cpu与ai加速卡的内存之间的数据传输压力较小。同时,由于第一处理子单元与第二处理子单元的中间处理结果可以通过片上缓存单元进行缓存,因此,减轻了内存单元的数据存储压力。

56.一些应用场景下可能需要多个神经网络配合起来才能执行一个具体的任务,例如,在美颜场景下,需要通过人脸检测网络从视频帧中检测出人脸,再通过五官检测网络从人脸图像中检测出五官的位置,然后通过五官美化网络对检测出的五官进行美化处理。因此,在一些例子中,神经网络可以包括多个子网络,每个子网络可以是一个独立的神经网络,也可以包括神经网络的一个或多个网络层。这种情况下,ai加速卡的内存单元可以用于存储神经网络包括的多个子网络中每个子网络的网络参数。一个子网络可以通过其对应的网络参数,将输入映射成输出。不同的子网络可以实现不同的功能,例如,在上述美颜场景下,神经网络包括的各个子网络分别为人脸检测网络、五官检测网络和五官美化网络。需要说明的是,一个子网络的类型可以是cnn(convolutional neural network,卷积神经网络)、rnn(recurrent neural network,循环神经网络)、lstm(long short-term memory,长短期记忆网络)等的任意一种,不同子网络的类型可以相同,也可以不同,本公开对此不作限制。

57.针对神经网络包括多个子网络的情况,在一些例子中,上述内存单元可以设置有多个分区,不同子网络的网络参数存储在不同分区中。也就是说,该内存单元的存储空间可以采用层次化的分区结构,以实现对各子网络的网络参数的分区存储管理。进一步地,为了方便对指定子网络的网络参数的读取,可以创建分区表,该分区表可以记录每个分区的起始地址、大小、对应的子网络的标识等信息,这样其他单元可以通过查找该分区表来确定指定子网络的存储地址,进而根据该存储地址读取到该指定子网络的网络参数;或者,可以为不同子网络设置不同的分区标识,内存单元根据子网络的分区标识确定分区路径,并将该子网络的网络参数存储在该分区路径对应的分区中,相对应地,其他单元也可以根据指定子网络的分区标识从内存单元中查找到该指定子网络的网络参数。当然,在其他实施例中,也可以根据具体场景的需要设置其他的存储管理方式。

58.在神经网络包括多个子网络的情况下,第一处理子单元可以基于调度到本处理单元的子网络的网络参数对待处理视频帧进行第一处理,该第一处理的具体内容可以根据子

网络所实现的功能来确定。在一些例子中,该控制单元可以通过向第一处理子单元发送使能信号的方式,将网络参数调度到第一处理子单元中。该使能信号类似一个触发信号,通过这一信号可以触发第一处理子单元读取网络参数,进而基于读取的子网络的网络参数对待处理视频帧进行第一处理。可选地,该控制单元可以在使能第一处理子单元后,为该第一处理子单元配置需要读取的子网络的网络参数的存储地址,以使该第一处理子单元到该存储地址下读取相应的数据。

59.在一个可选的实施例中,若神经网络包括串接的多个子网络,即神经网络的功能基于多个子网络的功能实现,且一个子网络的输出是下一个子网络的输入,控制单元可以先将第一个子网络的网络参数调度到第一处理子单元,再将第二个子网络的网络参数调度到第一处理子单元,依次类推,以保证各个子网络的有序运行。而在另一个可选的实施例中,在只包括一个神经网络的情况下,控制单元也可以将神经网络的网络参数调度到第一处理子单元,并多次使能该第一处理子单元,以使第一处理子单元基于该神经网络对待处理视频帧进行多次处理,从而提升ai推理的效果。

60.为了保证控制单元对多个子网络的网络参数的合理调度,在一些例子中,该第一处理子单元可以在当前的第一处理执行完成的情况下,向控制单元发送中断信号;该控制单元在接收到该中断信号的情况下,将下一个子网络的网络参数调度到该第一处理子单元上。也就是说,第一处理子单元在基于一个子网络对待处理视频帧的处理完成的情况下,可以通过向控制单元发送中断信号的方式通知控制单元,以使控制单元调度下一个子网络的网络参数。这样,第一处理子单元可以基于下一个子网络的网络参数对待处理视频帧进行处理。如此,ai加速卡可以在完成第一个子网络的ai推理后,立即启用第二个子网络的ai推理,依次类推,直到完成最后一个子网络的ai推理,从而提升处理效率。

61.在一些实施例中,所述处理单元还包括第三处理子单元,用于对所述待处理视频帧进行第三处理后输出至所述片上缓存单元进行缓存。所述第一处理子单元用于从所述片上缓存单元中读取经第三处理的所述待处理视频帧,并对经第三处理的所述待处理视频帧进行第一处理。第三处理子单元也可以称为预处理单元或前处理单元,相应地,第三处理可以称为预处理或前处理。具体地,所述第三处理可以包括但不限于调整尺寸大小、图像分割和数据归一化等中的至少一者。在相关技术中,预处理过程一般也是由host cpu执行的,而本公开实施例通过将预处理下沉到芯片端来执行,从而减轻了host cpu的处理压力。

62.在上述实施例中,第一处理子单元、第二处理子单元和第三处理子单元可以是从功能上划分的子单元,即,第一处理子单元用于基于神经网络的网络参数对待处理视频帧进行处理,第二处理子单元用于进行后处理,第三处理子单元用于进行预处理。在实际应用中,各个子单元的数量可以根据实际需要设置为大于或等于1的数值,本公开对此不做限制。例如,可以通过两个第三处理子单元依次进行预处理,再将这两个第三处理子单元最终输出的视频帧作为待处理视频帧,并输入到第一处理子单元进行处理。

63.在一些实施例中,所述处理单元的数量大于1,第i 1个处理单元中的第一子单元用于从所述内存单元中读取第i个处理单元中的第二处理子单元输出的第二视频帧,并将所述第i个处理单元中的第二处理子单元输出的第二视频帧作为待处理视频帧进行所述第一处理,i为正整数。其中,第i个处理单元可以采用所述神经网络包括的第i个子网络执行所述第一处理。

64.处理单元103的数量可以大于或等于神经网络包括的子网络的数量,也可以小于神经网络包括的子网络的数量。在处理单元103的数量大于或等于神经网络包括的子网络的数量的情况下,可以分别将各个子网络的网络参数调度到不同的处理单元上。在处理单元103的数量小于神经网络包括的子网络的数量的情况下,可以先将一部分子网络的网络参数调度到处理单元上,在某个处理单元处理完成的情况下,再向该处理单元调度其他子网络的网络参数。

65.在上述实施例中,第i个处理单元可以是固定的某个处理单元,例如,第i个处理单元是编号为xxxxxyi的处理单元。或者,第i个处理单元可以是第i个处于空闲状态(即未执行任何数据处理)的处理单元。例如,编号为xxxxxy3的处理单元为第1个处于空闲状态的处理单元,编号为xxxxxy6的处理单元为第2个处于空闲状态的处理单元,则将编号为xxxxxy3的处理单元确定为第1个处理单元,并将编号为xxxxxy6的处理单元确定为第2个处理单元。但在其他的情况下,第1个处理单元和第2个处理单元也可能是其他编号的处理单元。

66.进一步地,每个处理单元103均可以包括至少一个第三处理子单元,第i个处理单元103中的第三处理子单元用于对待处理视频帧进行预处理,并将预处理后的待处理视频帧输出至片上缓存单元102,第i个处理单元103中的第一处理子单元可以从片上缓存单元102中读取预处理后的待处理视频帧并进行第一处理。这样,由于ai加速卡的内存单元无需对第三处理子单元输出的中间数据进行存储,减小了内存单元的存储压力。

67.应当说明的是,本公开实施例中,一个处理单元中的第一处理子单元所处理的待处理视频帧,可以是上一个处理单元中的第二处理子单元处理完成的视频帧。第一个处理单元中的第一处理子单元所处理的待处理视频帧,可以是从视频流中解码得到的视频帧经第一个处理单元中的第三处理子单元处理完成后得到的视频帧。

68.考虑到ai加速卡的内存单元需要存储多个子网络的网络参数,ai加速卡的内存空间的占用可能较大,因此,为了减少内存空间的占用,在一些例子中,芯片的控制单元可以用于基于第一预设条件从待处理视频帧中筛选出第一目标视频帧;芯片还可以包括第一图像编码单元,该第一图像编码单元用于对该第一目标视频帧进行图像压缩后输出至内存单元,压缩后的第一目标视频帧用于输出至外部处理单元。该第一预设条件是对待处理视频帧进行筛选的选图条件,可选地,该第一预设条件可以与待处理视频帧的时间戳、序号或者包括的对象相关,例如,第一目标视频帧可以是每隔预设时间从待处理视频帧中筛选出来的,也可以是每隔预设帧数从待处理视频帧中筛选出来的,也可以是图像内容中包括特定目标的待处理视频帧。也就是说,芯片可以对解码得到的待处理视频帧进行筛选以及图像压缩,这样可以避免因未压缩的视频帧占用较多的存储空间而导致开销较大的问题。其中,该第一图像编码单元可以包括图像编解码器,即能够对图像进行压缩或者解压缩的程序或者设备;该外部处理单元可以是host cpu,以由host cpu对压缩后的第一目标视频帧进行相应处理后,输出给用于显示视频的显示组件,或者,该外部处理单元也可以包括用于显示视频的显示组件,即压缩后的第一目标视频帧直接输出给显示组件进行显示。

69.在一个可选的实施例中,控制单元可以是响应于第一处理子单元所发送的中断信号,控制第一图像编码单元开始进行图像压缩的;该中断信号可以是第一处理子单元在第一处理完成的情况下向控制单元发送的。也就是说,第一处理子单元在完成对待处理视频帧的第一处理的情况下,可以以中断信号的形式,将第一处理完成的消息通知给控制单元,

以使控制单元立即控制第一图像编码单元开始进行图像压缩,如此,提升ai加速卡内部的处理效率。

70.而在另一些例子中,芯片的控制单元可以用于基于第二预设条件从第二视频帧中筛选出第二目标视频帧;芯片还可以包括第二图像编码单元,该第二图像编码单元用于对该第二目标视频帧进行图像压缩后输出至内存单元,压缩后的第一目标视频帧用于输出至外部处理单元。该第二预设条件是对第二视频帧进行筛选的选图条件,同样的,该第二预设条件可以与第二视频帧的时间戳、序号或者包括的对象相关,例如,第二目标视频帧可以是每隔预设时间从第二视频帧中筛选出来的,也可以是每隔预设帧数从第二视频帧中筛选出来的,也可以是图像内容中包括特定目标的第二视频帧。也就是说,芯片也可以对ai推理完成后的视频帧进行筛选以及图像压缩,这样同样可以避免因未压缩的视频帧占用较多的存储空间而导致开销较大的问题。相对应地,该第一图像编码单元也可以包括图像编解码器;该外部处理单元可以是host cpu,也可以包括用于显示视频的显示组件。同样地,控制单元可以响应于第二处理子单元所发送的中断信号,控制第二图像编码单元开始进行图像压缩;该中断信号可以是第二处理子单元在第二处理完成的情况下向控制单元发送的。也就是说,第二处理子单元在完成对第一视频帧的第二处理的情况下,可以以中断信号的形式,将第二处理完成的消息通知给控制单元,以使控制单元立即控制第二图像编码单元开始进行图像压缩,如此,提升ai加速卡内部的处理效率。上述第一图像编码单元和第二图像编码单元可以是相同的图像编码单元,也可以是两个相互独立的、不同的图像编码单元。

71.外部处理单元获取到解码后的视频帧和/或ai推理后的视频帧后,可以利用些视频帧输出显示画面,在提升ai推理的处理效率后,显示画面的流畅性能够得到提升。

72.需要说明的是,上述的第一预设条件和第二预设条件还可以根据预设的图像质量参数来确定,例如,第一目标视频帧可以是待处理视频帧中信噪比超过预设的信噪比阈值的视频帧;第二目标视频帧可以是第二视频帧中分辨率超过预设的分辨率阈值的视频帧。当然,所选择的图像质量参数以及阈值可以根据具体场景的需要来设置,该第一预设条件和该第二预设条件可以相同,也可以不同,本公开对此不作限制。

73.为了对本公开实施例的芯片做更为详细的说明,接下来介绍一具体实施例:

74.本实施例的芯片应用于ai加速卡,该ai加速卡插设在终端的主板插槽中。本实施例的场景是该终端利用神经网络技术对接收到的视频进行人脸识别的场景,该场景中,需要经视频解码、人脸区域识别、人脸局部特征分析等多个步骤提取特征才能实现最终的人脸识别,其中涉及n个神经网络,以这n个神经网络包括子网络1和子网络2为例,子网络1是用于人脸区域识别的神经网络,子网络2是用于人脸局部特征分析的神经网络。这2个神经网络的网络参数存在host主存里。

75.相关技术中,加速卡一般是作为纯slave设备,用于辅助host cpu的工作,以ai加速卡为例,终端执行ai推理的过程如图4所示,其过程包括:

76.s401、host cpu对视频进行解码,得到帧数据;

77.s402、host cpu将帧数据以及子网络1的网络参数下载到ai加速卡的内存里;

78.s403、ai加速卡通过子网络1对帧数据进行模型推理,并将结果存放在内存中;

79.s404、host cpu从ai加速卡的内存中读取子网络1输出的结果;

80.s405、host cpu对子网络1输出的结果进行后处理;

81.s406、host cpu将加工处理后的数据和子网络2下载到ai加速卡的内存里;

82.s407、ai加速卡通过子网络2对处理后的数据进行模型推理,并将结果存放在内存中;

83.s408、host cpu读取ai加速卡的内存中存放的推理结果。

84.上述流程存在大量的host与加速卡间的内存访问动作,需要占用较多的host cpu资源,ai推理的效率较低。相关技术中,终端也可以借助gpu来执行ai训练/推理任务,然而,gpu同样常常需要等待host cpu进行访存操作而处于空闲状态,造成资源浪费,其效率同样较低。

85.而本实施例中,在加速卡内部做了硬件改进,以ai加速卡为例,图5是本公开实施例示出的一种ai加速卡的硬件结构示意图,其中,该ai加速卡包括mcu(即上述控制单元)、dram(即ai加速卡的内存单元)、video codec(即上述视频解码单元)、jpeg codec(即上述第一图像编码单元和第二图像编码单元)、pcie以及若干个cu;其中,dram是ai加速卡的内存单元,用于存储神经网络的网络参数以及处理前后的视频帧;mcu用于调度模型的网络参数到cu中,以及对video codec和jpeg codec进行控制调度;每个cu用于基于神经网络对视频帧进行模型推理,cu中包括前处理单元和后处理单元,前处理单元用于负责模型的前处理任务,后处理单元用于负责模型的后处理任务;video codec是视频编解码器,用于对视频进行解码;jpeg codec是图像编解码器,用于对视频帧进行压缩;pcie是ai加速卡与host cpu之间的交互通路,用于实现ai加速卡与host cpu之间的命令下发、数据传输等,视频码流也可通过该pcie传输到ai加速卡的内存中;另外,在ai加速卡内,上述的各模块通过noc(network on chip,片上网络)等互联总线和内存实现互联。

86.本实施例中,终端执行ai推理的过程如图6所示,其过程包括:

87.s601、host cpu将待处理视频、子网络1的网络参数和子网络2的网络参数传输至ai加速卡的内存中;

88.s602、ai加速卡内的mcu控制video codec对内存中的视频进行解码,并控制前处理单元对解码后的视频帧进行数据预处理(例如,调整尺寸大小、图像分割和数据归一化)后,将得到的帧大图存放到内存中;

89.s603、ai加速卡内的mcu控制cu读取解码得到的帧大图并传输到子网络1,再使能子网络1开始进行第一阶段的模型推理,得到的结果数据传输到后处理单元,同时,mcu基于第一预设条件挑选部分帧大图传输到jpeg codec进行图像压缩,压缩后的帧大图存放到内存中,等待host cpu读取;

90.s604、ai加速卡内的mcu控制后处理单元将模型1的输出数据进行图像分割,得到符合要求的帧小图(例如,去掉背景特征,并保留人脸局部特征等),并将帧小图存放到内存中;

91.s605、ai加速卡内的mcu控制cu读取帧小图并传输到子网络2,再使能子网络2开始进行第二阶段的模型推理,得到的结果数据传输到后处理单元,同时,mcu基于第二预设条件挑选部分帧小图传输到jpeg codec进行图像压缩,压缩后的帧小图存放到内存中,等待host cpu读取;

92.s606、将ai加速卡的内存中所存储的压缩后的帧大图和压缩后的帧小图传输至host cpu,用于终端显示。其中,压缩后的帧大图和压缩后的帧小图可以在不同的步骤中进

行传输,例如,压缩后的帧大图的步骤也可以在步骤s603中进行图像压缩完成后即开始传输。

93.需要说明的是,本实施例中以子网络1和子网络2为例,但在实际应用中,神经网络的数量可以大于等于3,即可以有多个神经网络,而针对子网络2之后的子网络的推理过程,可以参见s604和s605的步骤,本实施例在此不再赘述。本实施例中,ai加速卡针对视频人脸识别任务时的部分参数设置如表1所示。

94.表1 参数设置

[0095][0096]

基于该参数设置,ai加速卡在采用图像压缩与不采用图像压缩时内存占比的对比情况如表2所示。

[0097]

表2 内存占比对比

[0098][0099]

其中,节点i1、fb1、fb2、o1、o2、o3依次是指前面步骤中提到的待处理视频、数据预处理后得到的帧大图、图像分割后得到的帧小图、压缩后的帧大图、压缩后的帧小图、子网络2模型推理得到的图像;同时,jpg这一列是指采用图像压缩时的内存占用情况,rgb24这一列是指不采用图像压缩时的内存占用情况,对比可见,针对同一码率为4mb/s的视频,在不做图像压缩的情况下,该图像在ai推理过程中需要占用2100mb的内存空间,导致ai推理的速度很慢,在试验时每秒仅能够处理1至2张图像;而在使用了图像压缩的技术后,该图像在ai推理过程中所占用的内存空间仅为104.8mb,ai推理的速度较快。由此可见,本实施例

的方案可以有效地减少内存占用。

[0100]

本实施例的方案至少具有以下优点:

[0101]

(1)将视频解码、图像编码、模型前后处理等业务下沉到ai加速卡端,host cpu只需将相关模型和视频码流传输给ai加速卡即可,极大地减轻了host cpu的工作负担;

[0102]

(2)将所有的网络参数一次性下载到ai加速卡端,通过ai加速卡内的mcu控制调度,实现了多模型间的pipeline,而且,“模型前处理-模型推理-模型后处理”在ai加速卡内部执行,实现更好的pipeline处理;

[0103]

(3)模型间的数据传递不再需要依赖host cpu控制调度,减少了host cpu对ai加速卡的内存访问频率,因而进一步提升了处理效率;

[0104]

(4)采用图像压缩技术从帧大图与帧小图中挑选出一个子集来做压缩,减少了对内存空间的占用,同时减少了pcie的数据量和交互次数,因而提升了处理效率。

[0105]

经试验发现,经本实施例的方案得到的终端显示结果,相较于相关技术方案得到的终端显示结果而言,有效避免了掉帧的情况,终端显示的画面更加流畅。

[0106]

与前述的芯片的实施例相对应,本公开还提供了加速卡及其对应的设备的实施例。如图7所示,是本公开根据一示例性实施例示出的一种加速卡的示意图,所述加速卡包括:

[0107]

内存单元702,用于存储神经网络的网络参数;以及

[0108]

芯片702。

[0109]

上述芯片702可以采用前述任一实施例所述的芯片。加速卡中各部分的数据传输过程如图8所示。其中,模型1和模型2分别为前述实施例中的神经网络中的两个子网络。为了简洁,上述实施例以子网络数量为2的情况进行说明,在其他实施例中,子网络的数量也可以是其他数量,此处不再赘述。

[0110]

如图9所示,是本公开实施例的一种电子设备的示意图,所述电子设备包括加速卡901以及外部处理单元902,其中,所述加速卡901可以采用前述任一实施例中的加速卡;所述外部处理单元902可以是前述实施例中的host cpu,用于将所述神经网络的网络参数输出至所述内存单元。

[0111]

上述加速卡以及电子设备中各个组件的功能和作用的实现过程具体详见上述芯片中对应组件的实现过程,在此不再赘述。需要说明的是,上述芯片所对应的其他改进内容同样适用于加速卡以及电子设备。

[0112]

如图10所示,本公开实施例还提供一种数据处理方法,所述方法应用于本公开任一实施例所述的芯片,所述方法包括:

[0113]

步骤1001:所述控制子单元将神经网络的网络参数调度到所述第一处理子单元;

[0114]

步骤1002:所述第一处理子单元基于调度到本处理单元的网络参数对待处理视频帧进行第一处理,得到第一视频帧,并将所述第一视频帧输出至所述片上缓存单元进行缓存;

[0115]

步骤1003:所述第二处理子单元从所述片上缓存单元中读取所述第一视频帧,对读取的所述第一视频帧进行第二处理,得到第二视频帧并输出。

[0116]

在一些实施例中,所述处理单元还包括第三处理子单元,用于对所述待处理视频帧进行第三处理后输出至所述片上缓存单元进行缓存;所述方法还包括:所述第一处理子

单元从所述片上缓存单元中读取经第三处理的所述待处理视频帧,并对经第三处理的所述待处理视频帧进行第一处理。

[0117]

在一些实施例中,所述方法还包括:所述控制单元控制视频解码单元对输入视频进行视频解码,得到所述待处理视频帧。

[0118]

在一些实施例中,所述方法还包括:所述控制单元基于第一预设条件从所述待处理视频帧中筛选出第一目标视频帧,并将所述第一目标视频帧输出至第一图像编码单元进行图像压缩,压缩后的第一目标视频帧用于输出至外部处理单元。

[0119]

在一些实施例中,所述方法还包括:所述控制单元基于第二预设条件从所述第二视频帧中筛选出第二目标视频帧,并将所述第二目标视频帧输出至第二图像编码单元进行图像压缩,压缩后的第二目标视频帧用于输出至外部处理单元。

[0120]

在一些实施例中,所述处理单元的数量大于1,第i 1个处理单元中的第一子单元用于从所述内存单元中读取第i个处理单元中的第二处理子单元输出的第二视频帧,并将所述第i个处理单元中的第二处理子单元输出的第二视频帧作为待处理视频帧进行所述第一处理,i为正整数。

[0121]

在一些实施例中,所述神经网络包括多个子网络,各个子网络的网络参数均存储在加速卡的内存单元中;所述方法还包括:所述控制单元从所述内存单元中将神经网络的网络参数调度到所述第一处理子单元。

[0122]

在一些实施例中,第i个处理单元采用所述神经网络包括的第i个子网络执行所述第一处理。

[0123]

在一些实施例中,所述内存单元包括多个分区;所述多个子网络中的至少两个子网络的网络参数被存储在不同的分区中。

[0124]

本公开实施例还提供一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现本公开任一实施例所述的芯片中的控制单元执行的方法。

[0125]

计算机可读介质包括永久性和非永久性、可移动和非可移动媒体可以由任何方法或技术来实现信息存储。信息可以是计算机可读指令、数据结构、程序的模块或其他数据。计算机的存储介质的例子包括,但不限于相变内存(pram)、静态随机存取存储器(sram)、动态随机存取存储器(dram)、其他类别的随机存取存储器(ram)、只读存储器(rom)、电可擦除可编程只读存储器(eeprom)、快闪记忆体或其他内存技术、只读光盘只读存储器(cd-rom)、数字多功能光盘(dvd)或其他光学存储、磁盒式磁带,磁带磁磁盘存储或其他磁性存储设备或任何其他非传输介质,可用于存储可以被计算设备访问的信息。按照本文中的界定,计算机可读介质不包括暂存电脑可读媒体(transitory media),如调制的数据信号和载波。

[0126]

通过以上的实施方式的描述可知,本领域的技术人员可以清楚地了解到本公开实施例可借助软件加必需的通用硬件平台的方式来实现。基于这样的理解,本公开实施例的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品可以存储在存储介质中,如rom/ram、磁碟、光盘等,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本公开实施例各个实施例或者实施例的某些部分所述的方法。

[0127]

上述实施例阐明的模块或单元,具体可以由计算机芯片或实体实现,或者由具有某种功能的产品来实现。一种典型的实现设备为计算机,计算机的具体形式可以是个人计

算机、膝上型计算机、蜂窝电话、相机电话、智能电话、个人数字助理、媒体播放器、导航设备、电子邮件收发设备、游戏控制台、平板计算机、可穿戴设备或者这些设备中的任意几种设备的组合。

[0128]

以上所描述的各实施例仅仅是示意性的,其中所述作为分离部件说明的模块可以是或者也可以不是物理上分开的,在实施本公开实施例方案时可以把各模块的功能在同一个或多个软件和/或硬件中实现。也可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性劳动的情况下,即可以理解并实施。

[0129]

以上所述仅是本公开实施例的具体实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本公开实施例原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本公开实施例的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。