1.本发明属于图形显示技术领域,更具体地,涉及一种相同分辨率下多屏显示质量的控制方法以及控制系统。

背景技术:

2.随着图形处理任务的日益复杂,gpu不仅需要完成单个屏幕的图像显示,还需要进行双屏或者多屏的扩展显示。在显示存储带宽确定的条件下,每扩展一个屏幕,实际占用的显存带宽都会成倍进行增加,势必会影响显示的质量。尤其对于2k和4k分辨率的显示扩展,对gpu的带宽造成很大的压力,显示甚至会出现条纹、闪烁等严重问题。这些显示都是通过阴极射线管控制器(cathode ray tude controller,简称crtc)进行控制的。除了实际呈现到显示屏幕的有效数据时间外,还有大量的行同步时间和列同步时间,非常耗费时间。

3.申请号为201710907571.7中国专利申请公开了一种画面显示质量的调控方法、装置及存储介质,具体的,先输入像素数据,叠加已处理像素数据舍去的误差,对叠加后的像素数据进行伽玛校正,生成并输出伽玛校正数据至显示屏,接着,将伽玛校正后被舍去的误差数据经计算后进行保存,留待未处理像素数据叠加使用,直至所有像素数据处理并输出完毕。该方法是通过对像素数据的叠加处理和矫正来改进显示质量。

4.申请号为201610209567.9的中国专利申请公开一种视频显示质量的计算方法及设备,具体的,首先,其获取视频的屏幕显示质量、视频的帧率、视频的码率,根据屏幕显示质量、视频的帧率及视频的码率按照第一预设算法计算视频显示质量,其中,屏幕显示质量用于指示视频在显示屏幕上的显示质量的最高取值。其本质是一种显示质量的计算方法。

5.申请号为202010831936.4的中国专利申请公开了一种多屏显示系统、多屏显示系统的控制方法、存储介质,具体的,其公开了一种多屏显示系统,多屏显示系统包括显示装置,显示装置包括嵌入式主控板、分屏器和显示屏,所述嵌入式主控板连接有至少两个所述分屏器,每个分屏器连接有至少两个所述显示屏;所述分屏器用于分割所述嵌入式主控板发送的多媒体信号,并将分割后的多媒体信号输出至与所述分屏器连接的显示屏,其用于多屏显示中的多媒体信号分屏管理。

6.以上专利申请公开了多种关于多屏显示的技术,但是,在工程实践中如何快速有效地的提高相同分辨率下多屏显示质量还不得而知,因此,需要开发一种相同分辨率下多屏显示质量的控制方法和控制系统。

技术实现要素:

7.针对现有技术的缺陷,本发明的目的在于提供一种相同分辨率下多屏显示质量的控制方法以及控制系统,对每一个通道的时序进行错时触发,避免图形显示出现条纹、闪烁问题,从而获得较好的显示稳定性。

8.为实现上述目的,本发明提供了一种相同分辨率下多屏显示质量的控制方法,根据当前分辨率和时钟信息,计算出每一路显示控制器起始行扫描的时间点,对每一个通道

的时序进行错时触发,进而保证在每个行扫周期内,降低对显存带宽的平均压力,从而有效改进显示质量。

9.进一步的,其包括如下步骤:

10.s1:对当前连接的显示通道数进行检测,获取当前连接的显示通道数,

11.s2:对所有的显示设备执行模式信息检测,获得显示模式信息,显示模式信息包括像素时钟、显示设备的分辨率和行扫总时间,

12.s3:根据当前连接的显示通道数、像素时钟、显示设备的分辨率和分辨率行扫总时间进行计算,获得每个显示通道最佳触发时间偏移,

13.s4:根据每个显示通道数最佳触发时间偏移和其他时序信息,每个通道的最佳时间启动行扫进行数据显示,实现分时触发显示。

14.进一步的,步骤s1中,通过连接线接口通道进行探测,获取连接的显示通道数,探测手段包括hpd热插拔中断或者ddc回读相关寄存器一共两种方式。

15.进一步的,步骤s2中,对所有的显示设备执行模式信息检测时,通过ddc读取所有显示设备edid,如果edid符合标准规范,则进行edid解析获取显示模式信息,否则通过vesa标准获取显示模式信息。

16.进一步的,步骤s3中,计算获得每个显示通道最佳触发时间偏移时,控制每一个显示通道的显示控制器的触发时间间隔为td,td为行扫总时间的n等分,n为显示通道数。

17.进一步的,步骤s4中,设置好每一路显示器的分辨率和时序控制器后,使能第一路显示器进行显示,同时记录当前的系统时间,延时td后进行下一路显示,依次类推,最终触发所有的显示通道。

18.进一步的,其适用于linux操作系统和vxworks操作系统。

19.按照本发明的第二个方面,还提供一种实现如上所述的控制方法的控制系统,其包括显示通道检测模块、模式信息检测模块、时延计算模块和分时触发显示模块,

20.显示通道检测模块用于当前连接的显示通道数进行检测,获取当前连接的显示通道数,

21.模式信息检测模块用于对所有的显示设备执行模式信息检测,获得显示模式信息,显示模式信息包括像素时钟、显示设备的分辨率和行扫总时间,

22.时延计算模块同时与显示通道检测模块和模式信息检测模块存在信息交互,用于根据当前连接的显示通道数、像素时钟、显示设备的分辨率和分辨率行扫总时间进行计算,获得每个显示通道最佳触发时间偏移,

23.分时触发显示模块用于根据每个显示通道数最佳触发时间偏移和其他时序信息,在每个通道的最佳时间启动行扫进行数据显示,实现分时触发显示。

24.进一步的,模式信息检测模块通过ddc读取显示设备edid,如果edid符合标准规范,则进行edid解析获取显示模式信息,否则通过vesa标准获取显示模式信息。

25.进一步的,时延计算模块还用于计算出每一路显示控制器起始行扫描的时间点,每一路显示控制器显示使能的时间间隔为td,td为每一路的行扫的总时间time_htotal除以显示通道数n,

26.分时触发显示模块工作时,记录第一路显示器开始显示时间t0,延时td后,时间为t0 td,使能第二路显示器开始显示,再次延时td后,时间为t0 td*2时,使能第三路显示器

开始显示,以此类推,当时间为t0 td*(n-1)时,使能第n路显示器进行显示。

27.总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:

28.在gpu进行多路crtc显示且gpu显存带宽无法进一步提高的情况下,为了保证多屏显示的显示质量,对于相同分辨率下多屏扩展显示,利用每一行的空白和同步时间,通过错时行扫的模式,减少有效显示数据的重叠,进而减轻因带宽过大而造成显示质量降低的现象,有效提高显示的稳定性,避免多屏显示出现条纹、闪烁等问题,从而获得较好的用户体验。

附图说明

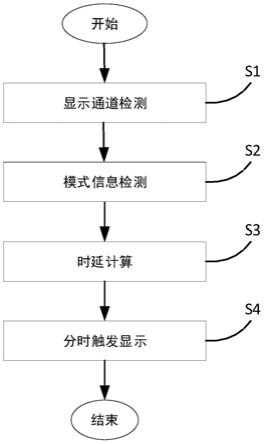

29.图1是本发明实施例提供的相同分辨率下多屏显示质量的控制方法流程图;

30.图2是本发明实施例提供的crtc显示触发流程图;

31.图3是本发明实施例中提供的接口检测和显示信息检测图;

32.图4是本发明实施例中提供的显示模式信息简要图;

33.图5是本发明实施例中提供的改进前的crtc时序和带宽占比模拟图;

34.图6是本发明实施例中提供的改进后的crtc时序和带宽占比模拟图。

具体实施方式

35.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

36.本发明公开一种相同分辨率下多屏显示质量的控制方法以及控制系统,其为一种多屏扩展显示质量的控制方法和控制系统,其通过错时行扫的模式,可以有效利用空闲回扫的时间空白,减少有效显示数据的重叠时间,避免因带宽过大而造成显示稳定性下降,提高显示质量。

37.图1是本发明实施例提供的相同分辨率下多屏显示质量的控制方法流程图,由图可知,其包括如下几个步骤:

38.s1:对当前连接的显示通道数进行检测,获取当前连接的显示通道数。本步骤中,通过连接线接口通道进行探测,获取连接的显示通道数,探测手段包括hpd热插拔中断或者ddc回读相关寄存器一共两种方式。

39.s2:对所有的显示设备执行模式信息检测,获得显示模式信息,显示模式信息包括像素时钟、显示设备的分辨率和行扫总时间。具体的,对所有的显示设备执行模式信息检测时,通过ddc读取所有显示设备edid,如果edid符合标准规范,则进行edid解析获取显示模式信息,否则通过vesa标准获取显示模式信息。

40.s3:根据当前连接的显示通道数、像素时钟、显示设备的分辨率和分辨率行扫总时间进行计算,获得每个显示通道最佳触发时间偏移。具体的,计算获得每个显示通道最佳触发时间偏移时,控制每一个显示通道的显示控制器的触发时间间隔为td,td为行扫总时间的n等分,n为显示通道数。

41.s4:根据每个显示通道数最佳触发时间偏移和其他时序信息,每个通道的最佳时

间启动行扫进行数据显示,实现分时触发显示。本步骤中,设置好每一路显示器的分辨率和时序控制器后,使能第一路显示器进行显示,同时记录当前的系统时间,延时td后进行下一路显示,依次类推,最终触发所有的显示通道。

42.实现如上所述的控制方法的控制系统,其包括显示通道检测模块、模式信息检测模块、时延计算模块和分时触发显示模块。其中,显示通道检测模块用于当前连接的显示通道数进行检测,获取当前连接的显示通道数,模式信息检测模块用于对所有的显示设备执行模式信息检测,获得显示模式信息,显示模式信息包括像素时钟、显示设备的分辨率和行扫总时间。时延计算模块同时与显示通道检测模块和模式信息检测模块存在信息交互,用于根据当前连接的显示通道数、像素时钟、显示设备的分辨率和分辨率行扫总时间进行计算,获得每个显示通道最佳触发时间偏移。分时触发显示模块用于根据最佳触发时间偏移和其他时序信息,在最佳时间一一启动每个通道进行行扫,实现分时触发显示。更具体的,模式信息检测模块通过ddc读取显示设备edid,如果edid符合标准规范,则进行edid解析获取显示模式信息,否则通过vesa标准获取显示模式信息。时延计算模块还用于计算出每一路显示控制器起始行扫描的时间点,每一路显示控制器显示使能的时间间隔为td,td为每一路的行扫的总时间time_htotal除以显示通道数n。分时触发显示模块工作时,记录第一路显示器开始显示时间t0,延时td后,时间为t0 td,使能第二路显示器开始显示,再次延时td后,时间为t0 td*2时,使能第三路显示器开始显示,以此类推,当时间为t0 td*(n-1)时,使能第n路显示器进行显示。

43.本发明的方法和系统适用于linux操作系统和vxworks操作系统,针对多屏相同分辨率显示的情况,通过错时扫描的方式来控制显示质量。

44.图2是本发明实施例提供的crtc显示触发流程图,如图2所示,每一路显示控制器触发显示使能顺序按以下步骤执行:

45.第一步:获取显示通道数。具体获得显示通道数的流程如图3所示。首先通过hpd信号进行探测是否有hdmi通道连接。如果有hpd信号,则表示连接了hdmi通道,统计连接的hdmi通道数,否则通过ddc通道探测是否有dvi接口连接。如果通过ddc检测到信号,则表示连接了dvi通道,统计连接的dvi通道数,否则表示显示通道无连接。显示总通道数为hdmi和dvi通道数量的总和。

46.第二步:获取每一路的显示模式信息。对于检测到连接的设备,通过ddc读取显示设备edid,如果edid符合标准规范,则进行edid解析获取显示模式信息,否则通过vesa标准获取显示模式信息。显示模式信息的简要信息如图4所示,图4中,left margin为左扫描空白时间,right margin为右扫描空白时间,upper margin为上扫描空白时间,lower margin为下扫描空白时间,hsynclen为水平同步长度,vsynclen为垂直同步长度,time_htotle为水平行扫总时间,time_vtotle为垂直扫描总时间,xres为水平有效数据刷新时间,yres为垂直有效数据刷新时间。显示器通过电子枪轰击完成显示,电子枪必须完成从左到右的水平扫描和从上到下的垂直扫描。当电子枪完成一行扫描重新回到下一行的开始,为一个水平折回。当一屏幕全部扫描完毕,电子枪从底部回到左上角,为一个垂直折回。水平折回的时间是左扫描空白时间、右扫描空白时间和水平同步长度的总和,垂直折回的时间是上扫描空白时间、下扫描空白时间和垂直同步长度的总和。显示模式信息的获取主要包括像素时钟、行扫总时间。本发明申请有效利用第一屏的空闲回扫的时间空白进行第二屏的有效

数据扫描,从而改进显示质量。

47.第三步、时延计算,根据当前显示通道数、分辨率以及时钟信息,计算出每一路crtc起始行扫描的时间点,每一路crtc显示使能的时间间隔为每路行扫的总时间除以通道数,即td=time_h total/n。

48.第四步、时序和图像数据生成,当第一路crtc开始显示时,记录时间为t0。延时td后,即时间为t0 td时,使能第二路crtc开始显示。再次延时td后,即时间为t0 td*2时,使能第三路crtc开始显示。以此类推,当时间为t0 td*(n-1)时,使能第n路crtc进行显示。

49.图5是本发明实施例中提供的改进前的crtc时序和带宽占比模拟图,图6是本发明实施例中提供的改进后的crtc时序和带宽占比模拟图,如图5和图6模拟图所示,以4路显示通道为例,改进前的带宽占比最大为单屏带宽的4倍,改进后的带宽占比最大为单屏带宽的2-3倍。改进后的带宽占比与改进前的带宽占比有了改善,可见,对于相同分辨率的多屏显示,通过错时扫描的方式,可以有效减轻带宽影响,提高显示的质量。

50.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。