交叉开关阵列装置和使用该装置的模拟乘积累加操作方法

1.相关申请的交叉引用

2.本技术基于于2020年10月7日在韩国知识产权局提交的第10-2020-0129509号韩国专利申请并要求其优先权,其公开内容通过引用整体并入本文。

技术领域

3.本公开涉及与神经形态计算相关的硬件装置、以及使用该硬件装置的模拟乘积累加(analog multiply-accumulate,mac)操作方法。

背景技术:

4.为了克服基于传统冯

·

诺依曼结构的芯片的结构限制,集成电路(integrated circuit,ic)芯片开发者一直在开发神经网络硬件和/或神经形态计算硬件。这种硬件可以基于神经网络,神经网络包括神经元和连接神经元的突触,神经元是人脑的基本单元。神经网络可能会超过传统机器学习算法的限制,并且特别是在图像识别、模式学习和认知能力方面显示出潜力,并且可能能够接近人类的能力。神经网络硬件和/或神经形态计算硬件用于各种领域。此外,正在考虑和开发用于使用低功率快速执行神经网络的操作操作的专门的专用集成芯片(application specific integrated chip,asic)。

技术实现要素:

5.本发明构思涉及基于压缩截断奇异值分解(compressed-truncated singular value decomposition,c-tsvd)的阵列装置和使用该阵列装置的模拟乘积累加(mac)操作方法,该阵列装置能够减少阵列划分(array partitioning)中的子阵列的数量,同时最小化推理准确度(inference accuracy)和延迟的恶化。

6.根据本发明构思的一些方面,提供了基于压缩截断奇异值分解(c-tsvd)的交叉开关阵列(crossbar array)装置,其包括在m

×

n矩阵中的原始交叉开关阵列,该m

×

n矩阵具有n个行输入线和m个列输出线并且包括电阻存储器设备的单元,或者其包括通过基于c-tsvd划分原始交叉开关阵列获得的两个部分交叉开关阵列,其中n和m是自然数。该装置还包括:模数转换器(adc),被配置为转换通过经过阵列划分来划分原始交叉开关阵列或这两个部分交叉开关阵列而获得的子阵列的列输出线的输出值;加法器,被配置为将adc的结果求和以对应于列输出线;以及控制器,被配置为控制原始交叉开关阵列或这两个部分交叉开关阵列的应用。基于c-tsvd的交叉开关阵列装置可以对应于神经形态计算中的神经网络的一层。输入值可以被输入到行输入线,权重可以乘以输入值,并且累加结果可以作为列输出线的输出值输出,并且权重对应于原始交叉开关阵列或这两个部分交叉开关阵列。

7.根据本发明构思的一些方面,提供了基于c-tsvd的交叉开关阵列装置,包括通过划分在m

×

n矩阵中的原始交叉开关阵列而获得的两个部分交叉开关阵列,m

×

n矩阵具有n个行输入线和m个列输出线,并且包括基于c-tsvd的电阻存储器设备的单元,其中n和m是自然数。该装置还包括:模数转换器(adc),其被配置为转换经过阵列划分来划分两个部分交

叉开关阵列而获得的子阵列的列输出线的输出值;以及加法器,其被配置为将adc的结果求和,以对应于列输出线。基于c-tsvd的交叉开关阵列装置可以对应于神经形态计算中的神经网络的一层。输入值可以被输入到行输入线,权重可以乘以输入值,并且累加结果作为列输出线的输出值被输出,并且权重可以对应于两个部分交叉开关阵列。

8.根据本发明构思的一些方面,提供了模拟乘积累加(mac)操作方法,包括计算在具有n个行输入线和m个列输出线并包括电阻存储器设备的单元的m

×

n矩阵中的原始交叉开关阵列(其中n和m是自然数),选择性地执行将原始交叉开关阵列划分为两个部分交叉开关阵列的压缩截断奇异值分解(c-tsvd),根据选择性地执行c-tsvd的结果将原始交叉开关阵列或两个部分交叉开关阵列划分成子阵列,将输入值输入到子阵列的行输入线,将输入值乘以权重,并累加在子阵列中的乘法结果,并且将输出值输出到子阵列的列输出线,通过使用模数转换器(adc)对列输出线的输出值进行模数转换,并通过使用加法器对adc结果求和,以对应于列输出线。可以在神经形态计算中使用对应于神经网络的一层的交叉开关阵列装置。交叉开关阵列装置可以包括原始交叉开关阵列或两个部分交叉开关阵列、adc、加法器和控制器。在选择性地执行c-tsvd时,可以由控制器控制原始交叉开关阵列或两个部分交叉开关阵列的应用。

附图说明

9.从下面结合附图的详细描述中,将更清楚地理解本发明构思的实施例,其中:

10.图1a和图1b是示出了神经网络中的乘法和累加操作的概念以及激活函数的概念图;

11.图2是示出与权重相对应的交叉开关阵列的结构的概念图;

12.图3a至图3c是示出阵列划分的概念图;

13.图4a和图4b是示出了根据本发明构思的一些实施例的在基于交叉开关阵列装置中采用的奇异值分解(singular value decomposition,svd)和截断奇异值分解(truncated singular value decomposition,tsvd)、将原始交叉开关阵列划分为部分交叉开关阵列的概念的概念图;

14.图5a和图5b是通过应用tsvd来按尺寸顺序布置矩阵s的对角矩阵分量的曲线图;

15.图6是示出根据矩阵s的对角矩阵分量当中的取数比(taken ratio)的推理准确度的曲线图;

16.图7a和7b是示意性地示出了与正则化参数对根据取数比的推理准确度的影响有关的两种学习方法的流程图;

17.图8a和8b是示出了根据本发明构思的一些实施例的在基于交叉开关阵列装置中采用的压缩截断奇异值分解(compressed-truncated singular value decomposition,c-tsvd)、将原始交叉开关阵列划分成部分交叉开关阵列的概念的概念图;

18.图9a和9b是示出根据一些实施例的交叉开关阵列装置可以应用于神经形态计算中的神经网络的多个层的概念图;

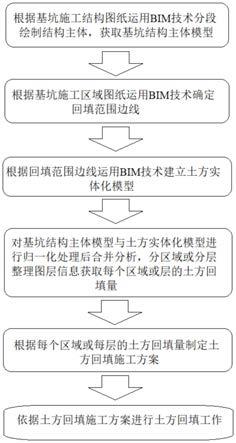

19.图10是示出根据本发明构思的一些实施例的使用交叉开关阵列装置的模拟乘法-累加(mac)操作方法的流程图;并且

20.图11a和11b是示出与神经形态计算中的神经网络的层有关的图10的模拟mac操作

方法的流程图。

具体实施方式

21.在下文中,将参考附图详细描述本发明构思的一些实施例。贯穿全文,相同的附图标记指代相同的元件,并且将省略先前给出的元件描述。

22.图1a和图1b是示出了神经网络中的乘法和累加操作以及激活函数的概念的概念图,并且图2是示出与权重值相对应的交叉开关阵列的结构的概念图。

23.参考图1a、图1b和图2,神经网络可以包括将输入值乘以权重并累加乘法结果的操作和激活函数。图1a展示了神经网络的形状。神经网络可以通常包括在左侧阴影化的输入层、在右侧阴影化的输出层以及布置在输入层和输出层之间的多个隐藏层。输入到层中的每个层的输入值可以乘以权重并累加,并且可以通过激活函数来激活。这种过程由图1b中的等式表示。在图1b中,ai可以表示输入值,并且wi可以表示权重。这里,b代表偏差。各种函数之一可以用作激活函数σ。代表性地,sigmoid函数或整流线性单位(rectified linear unit,relu)函数可以用作激活函数σ。激活函数σ和本公开不限于上述函数。

24.在一些实施例中,权重可以在矩阵中,并且权重可以被表示为包括电阻存储器设备112的单元的交叉开关阵列110,如图2所示。这里,电阻存储器设备112的每个电阻存储器设备可以由例如电阻随机存取存储器(resistive random access memory,rram)、磁性随机存取存储器(magnetic random access memory,mram)、相变随机存取存储器(phase-change random access memory,pram)或铁电随机存取存储器(ferroelectric random access memory,feram)来实现。然而,电阻存储器设备112和本公开不限于上述存储器。在一些实施例中,在图2中,可以省略单元晶体管。在下文中,交叉开关阵列110可以是包括电阻存储器设备112的单元的硬件概念,并且表示交叉开关阵列110的交叉开关阵列矩阵可以是与交叉开关阵列110的操作或功能相关的数学概念。

25.交叉开关阵列110的操作可以用电压和电流来描述。当对应于电压的输入值被输入到交叉开关阵列110的字线wl时,对应于电流的输出值被输出到位线bl。输出值的电流可以对应于由神经网络执行的乘法和累加操作的结果。交叉开关阵列110的操作由等式1表示,如下。

26.im=∑gmnvn

ꢀꢀ

(1)

27.在等式1中,im表示作为输出值的电流,vn表示作为输入值的电压,并且gmn表示电导率。在等式1中,m和n是自然数,可以分别对应于输出值的数量和输入值的数量。

28.等式1可以用等式2中所示的矩阵的概念表示,如下所示。

29.z=w*a

ꢀꢀ

(2)

30.在等式2中,a可以表示n

×

1列矩阵,w可以表示m

×

n矩阵,并且z可以表示m

×

1列矩阵。结合等式2,a的分量可以对应于作为输入值的电压,z的分量可以对应于作为输出值的电流,并且w的分量可以对应于电导率。

31.当权重矩阵被映射到交叉开关阵列110时,权重矩阵的尺寸可能非常大,并且当乘法和累加操作结果要通过模数转换器(analog-to-digital converter,adc)(参考图3a的120)从模拟转换为数字时,可能需要高准确度。另一方面,当adc的精确度增加时,adc电路的面积可能迅速增加,并且adc电路的性能可能迅速降低,可能希望或者甚至需要将adc的

精确度保持在不超过均匀水平,例如,大约几位(bit)。因此,具有大尺寸的权重矩阵可以不按原样计算,并且可以执行阵列划分,使得具有大尺寸的权重矩阵可以被划分成具有小尺寸的多个权重矩阵。权重矩阵的阵列划分将参考图3a、图3b和图3c更详细地描述。

32.图3a至图3c是示出阵列划分的概念图。

33.参考图3a至图3c,当与具有512

×

128尺寸的权重矩阵相对应的交叉开关阵列110中的乘法和累加操作结果将通过使用例如不超过5位的adc 120a来转换时,具有512

×

128尺寸的权重矩阵可以被划分成具有32

×

32尺寸的64个子阵列110a,并且可以执行乘法和累加操作。此外,子阵列的每个子阵列的adc结果可以通过包括加法器130的加法器树130来求和。

34.更详细地,当与尺寸为512

×

128的权重矩阵相对应的交叉开关阵列110被划分成尺寸为32

×

32的子阵列时,子阵列的数量可以是512/32*128/32=16*4=64。此外,当adc 120a在子阵列的每个子阵列的列上执行模数转换时,adc 120a的操作的数量可以是64*32=2048。当adc 120a的结果通过加法器130求和时,对于一列可以获得16个adc结果。从图3c中可以看出,求和可以在第一步中执行八次,在第二步中执行四次,在第三步中执行两次,在第四步中执行一次。因此,对于一列,加法器130可以执行15次求和。此外,由于列的数量是32*4,由加法器130执行的求和操作的次数可以是15*32*4=1920。当求和的步骤被称为加法器130的级时,加法器130的级数可以是4。如上所述,加法器130可以以多级的形式配置加法器树。结果,总操作电流可以被计算为单元电流的512*128=64*32*32=65536倍。

35.当adc 120a的尺寸较大时,可能难以在每列中布置一个adc 120a,并且一个adc 120a通常可以通过使用多路复用器mux来对多列执行ad转换。一个加法器130可以布置在加法器树130t的每一级中,从而可以执行求和。然而,根据一些实施例,在每一级中可以布置不同数量的加法器130。

36.下面的表1通过概括交叉开关阵列的矩阵的尺寸,示出了子阵列的子阵列数量#、adc的adc操作数量#、加法的加法器的操作数量(#)、加法器级(adder stage)的加法器级的数量#以及电流单元的操作电流数量#的等式。

37.权重m x n512x128单元/权重_元素b1子阵列尺寸s x s32x32子阵列的数量#ns=ceil(m/s)*ceil(n/s)*b16*4*1=64adc的数量#ns*s64*32=2048加法的数量#{ns-ceil(n/s)*b}*s{64-4}*32=1920加法器级的数量#ceil(log

2 ceil(m/s))4单元电流的数量#ns*s*s64*32*32=65536

38.[表1]

[0039]

在表1中,权重表示原始交叉开关阵列的矩阵的尺寸,并且b表示每个权重元素所需的单元的数量。例如,在权重元素是8位的情况中,当单元是1位的单级单元(single level cell,slc)时,b是8;在单元是2位的多级单元的情况中,b是4;并且在单元是4位的四级单元的情况中,b是2。另一方面,当单元是3位的三级单元(triple level cell,tlc)时,因为b=8/3=2.xx,不是整数,所以b可能通常不被考虑。然而,如果要考虑b,b可以通过绑

定三个权重元素来表示为八个tlc。作为参考,在表1中,b可以被计算为1。

[0040]

在本文中,ceil()是一个向上舍入函数(或取整函数),并且ceil(x)表示不小于x的最小整数。加法器130的操作的数量可以归纳为{ceil(m/s)-1}*ceil(n/s)*b*s=ceil(m/s)*ceil(n/s)*b*s-ceil(n/s)*b*s=ns*s-ceil(n/s)*b*s={ns-ceil(n/s)*b}*s。

[0041]

根据本发明构思的一些实施例的交叉开关阵列装置100可以通过将交叉开关阵列110分解成几个部分交叉开关阵列(参考图4b的110a或图8b的110b),并且经过阵列划分将部分交叉开关阵列的每个部分交叉开关阵列划分成子阵列110,而不是经过阵列划分将交叉开关阵列110直接划分成子阵列110来减少(并且在一些实施例中可以显著减少)子阵列的数量。此外,根据本发明构思的一些实施例的交叉开关阵列装置100可以通过减少子阵列的数量来减少adc的操作的数量、加法器的操作的数量、加法器级的数量以及操作电流。在下文中,在图4a和图4b中,将更详细地描述将交叉开关阵列分解成部分交叉开关阵列的方法。

[0042]

图4a和图4b是示出了根据本发明构思的一些实施例的基于在交叉开关阵列装置中采用的奇异值分解(svd)和截断奇异值分解(tsvd)、将原始交叉开关阵列分解成部分交叉开关阵列的概念的概念图。

[0043]

参考图4a和图4b,根据线性代数,尺寸为m

×

n的矩阵w可以表示为三个矩阵u、s和v

t

通过svd的乘积。矩阵u可以具有m

×

m的尺寸,矩阵s可以具有m

×

n的尺寸,并且矩阵v

t

可以具有n

×

n的尺寸。此外,在矩阵s中,只有对角矩阵分量可以具有不为0的值。当矩阵w的秩为k时,矩阵s中有k个非0的对角矩阵分量。因此,矩阵u、s和v

t

可以分别简化为尺寸为m

×

k、k

×

k和k

×

n的矩阵。虽然进行了这样的减少,但是矩阵w的值可以不受影响。

[0044]

秩k不超过m和n的最小值。也就是说,秩k不超过m和n中的较小值。此时,当从矩阵s的对角矩阵分量中以大的顺序(in large order)仅选择一部分时,可以减少k。当通过选择对角矩阵分量的一部分来减少k时,矩阵w可以变成近似值,这被称为tsvd。当不应用tsvd时,矩阵w可以通过分区阵列1级来实现。当应用tsvd时,因为必须实现三个矩阵u、s和v

t

,所以矩阵w可以通过分区阵列3级来实现。当矩阵w由分区阵列3级实现时,矩阵w的尺寸可以显著减小。

[0045]

在图4a中,当矩阵w被划分成三个矩阵u、s和v

t

,并且矩阵w的秩为k时,矩阵u、s和v

t

可以分别简化为m

×

k、k

×

k和k

×

n的矩阵。此外,当从矩阵s的对角矩阵分量中以大的顺序选择一部分并且k被减小为k'(k'≤k)时,矩阵u、s和v

t

可以被进一步简化为分别具有m

×

k'、k'

×

k'和k'

×

n尺寸的矩阵。

[0046]

在图4b中,示出了分别对应于矩阵u、s和v

t

的第一、第二和第三部分交叉开关阵列110a1、110a2和110a3。本文将描述部分交叉开关阵列110a1、110a2和110a3的操作。列矩阵a的分量可以作为输入值输入到对应于矩阵v

t

的第一部分交叉开关阵列110a1的输入线,并且可以作为输出线的输出值输出。来自第一部分交叉开关阵列110a1的输出值可以作为输入值输入到对应于矩阵s的第二部分交叉开关阵列110a2的输入线,并且可以作为输出线的输出值输出。来自第二部分交叉开关阵列110a2的输出值可以作为输入值输入到对应于矩阵u的第三部分交叉开关阵列110a3的输入线,并且可以作为输出线的输出值输出。结果,对应于矩阵u的第三部分交叉开关阵列110a3的输出值实际上可以等于通过将列矩阵a的分量输入到对应于矩阵w的交叉开关阵列100a的输入线作为输入值、并将列矩阵a的分量输出到

输出线而获得的w*a。

[0047]

部分交叉开关阵列110a1、110a2和110a3中的每一个部分交叉开关阵列可以通过像交叉开关阵列100a那样的阵列划分被划分成子阵列。在图4b中,省略了阵列划分,并且示出了对应于部分交叉阵列110a1、110a2和110a3的仅三级。

[0048]

为了实际使用tsvd,需要考虑两个问题。首先是神经元网络的推理精确度下降的可接受性,这可能是由用近似代替矩阵w引起的。第二,由矩阵的尺寸减小引起的优点应该比由3级实现引起的缺点更大,并且最好大得多。推理精确度将参考图5a至图6进行描述,并且将参考图8a和图8b描述由矩阵的尺寸减小引起的优点。

[0049]

图5a和图5b是通过应用tsvd按尺寸顺序布置矩阵s的对角矩阵分量的曲线图。x轴表示矩阵s的对角矩阵分量的索引(index),并且y轴表示奇异值。

[0050]

参考图5a和图5b,在使用改进的国家标准和技术研究所数据库(modified national institute of standards and technology,mnist数据库)学习了用于手写数字分类的784-512-128-10深度神经网络(deep neural network,dnn)之后,通过将tsvd用于图5a中第一层l1的784-512权重矩阵w和图5b中第二层l2的512

–

128权重矩阵w,矩阵s的对角矩阵分量可以以大的顺序排列。

[0051]

正则项可以在学习期间除以正则化参数。随着正则化的加强,接近0的矩阵分量可能增加,从而可以估计当取相同数量的分量时矩阵w的近似值更接近矩阵的真实值。示出了在图5a和在图5b中更详细描述地当正则化参数可以是0.0、0.05、0.10、0.20和0.50时的对角矩阵分量。随着正则化参数的增加,对应于高索引的大多数奇异值变为0。因此,当通过选择诸如0.20或0.50的大值作为正则化参数来加强正则化时,尽管可以采用例如几十个对角矩阵分量的一部分,但是可以估计矩阵w的近似值不会显著偏离矩阵w的真实值。

[0052]

作为参考,正则化(regularization)作为通过减少权重矩阵分量的数量来减少过拟合(over-fitting)的dnn学习方法之一,可以随着dnn尺寸的增加而被更广泛地使用。正则化参数可以对应于所引入的正则项的超参数,以便在执行学习时防止过拟合,从而利用损失函数或成本函数的概念最小化损失。例如,正则化参数可以对应于用于脊回归(ridge regression)、最小绝对收缩和选择算子(least absolute shrinkage and selection operator,lasso)回归或弹性网回归的正则项的超参数,尽管本公开不限于此。

[0053]

图6是示出了根据矩阵s的对角矩阵分量当中的取数比的推理准确度的曲线图。x轴表示取数比,y轴表示推理准确度,并且x轴和y轴都没有单位。

[0054]

参考图6,取数比可定义为k’/(m或n),其为矩阵s的所选择的对角矩阵分量的数量k’与对角矩阵分量的数量m或n的比值,或作为为百分比的k’/(m或n)*100。在图6的曲线图中,x轴上的取数比可以表示为k’/(m或n)并且可以除以正则化参数。从图6的曲线图可以看出,排除正则化参数为0.00的情况,在不大于0.1的取数比中,推理准确度可以对应于不小于0.9。因此,尽管在通过预定正则化参数进行正则化的情况中,取数比不超过10%,但是推理准确度可能不会受到显著影响。

[0055]

下面的表2示出了根据正则化参数和取数比的推理准确度,“训练的”示出了通过学习来计算的原始交叉矩阵w的推理准确度,并且“tsvd”示出了通过tsvd划分的矩阵的推理准确度。

[0056][0057][0058]

[表2]

[0059]

从表2中可以注意到,尽管在正则化参数0.10和0.20中取数比不超过10%,但是推理准确度几乎没有损失。

[0060]

图7a和7b是示意性地示出了与调节参数对根据取数比的推理准确度的影响有关的两种学习方法的流程图。图7a是示出推理准确度受正则化参数影响的学习方法的流程图,并且图7b是示出推理准确度不受正则化参数影响的学习方法的流程图。

[0061]

参考图7a,首先,在操作s110中,可以通过学习来计算原始交叉开关阵列的矩阵。在学习中,可以包括用于防止过拟合的正则项。接下来,在操作s130中,可以通过svd将原始交叉开关阵列划分成部分交叉开关阵列。然后,在操作s150中,可以选择作为矩阵s的k个分量的一部分的k’个分量。这里,选择k’分量可以包括采用取数比,这可能意味着通过tsvd将原始交叉开关阵列的矩阵分解成部分交叉开关阵列的矩阵。此外,tsvd的执行可以包括经过阵列划分将部分阵列的每个部分阵列划分成子阵列。

[0062]

然后,在操作s170中,可以执行推理。推理可以意味着通过向权重矩阵输入新的输入值来提取输出值,并且权重矩阵可以意味着通过tsvd获得的部分交叉开关阵列的矩阵和部分交叉开关阵列的矩阵的子阵列的矩阵。推理准确度可以基于输出值与真值的相似程度来确定,并且可以基于比较输出值与真值来确定。如上所述,当执行图7a所示的学习方法时,根据取数比的推理准确度——即k’/(m或n)——可能受到用于学习的正则项的正则化参数的影响。因此,当要采用低的取数比时,可以选择合适的正则化参数。

[0063]

参考图7b,首先,在s210操作中,可以选择任意的第一原始交叉开关阵列的矩阵。接下来,在操作s230中,可以通过svd将第一原始交叉开关阵列的矩阵划分为部分交叉开关阵列的矩阵。然后,在操作s250中,可以选择作为矩阵s的k个分量的一部分的k’个分量。选择k’个分量可以包括采用取数比,这意味着通过tsvd将第一原始交叉开关阵列的矩阵划分为部分交叉开关阵列的矩阵。

[0064]

然后,在操作s270中,可以用第二原始交叉开关阵列的矩阵来执行学习。这里,第二原始交叉开关阵列的矩阵可以对应于通过对包括k’个分量的部分交叉开关阵列的矩阵进行整合而获得的矩阵,并且可以不同于第一原始交叉开关阵列的矩阵。通过学习,可以计算新的原始交叉开关阵列的矩阵。此外,在学习中,可以包括用于防止过拟合的正则项。

[0065]

然后,在操作s290中,可以执行推理。在一些实施例中,在执行推理之前,还可以包括图7a的操作s130至s150。当执行图7b所示的学习方法时,根据取数比的推理准确度——

即k’/(m或n)——可能不会受到正则项的正则化参数的显著影响。因此,在图7b的学习方法中,可以不考虑正则化参数而采用取数比。

[0066]

图8a和8b是示出了根据本发明构思的一些实施例的基于在交叉开关阵列装置100b中采用的压缩截断奇异值分解(c-tsvd)将原始交叉开关阵列划分成部分交叉开关阵列的概念的概念图。

[0067]

参考图8a和8b,如上所述,因为在tsvd方法中可以使用三个矩阵,所以三个级可以由三个部分交叉开关阵列来配置。取代像图8a和图8b中那样使用矩阵s和矩阵v

t

,当使用两个矩阵的乘法s*v

t

时,级数可以减少到2,同时减小矩阵的尺寸。这种方法可以被称为压缩tsvd(c-tsvd),并且可以被采用到交叉开关阵列装置100b。在根据一些实施例的交叉开关阵列装置100b中,通过两级实现减小矩阵的尺寸所带来的优点将被描述如下。

[0068]

首先,子阵列的数量可以如下计算。当原始交叉开关阵列的矩阵w的尺寸为m

×

n,并且由1级实现时,子阵列的数量为ns(w)=ceil(m/s)*ceil(n/s)*b。因此,当原始交叉开关阵列的矩阵w的尺寸为512

×

128时,ns(w)=16*4*1=64。

[0069]

另一方面,当通过c-tsvd实现2级时,子阵列的数量为ns(wt)=nu nv=ceil(m/s)*ceil(k/s)*b ceil(k/s)*ceil(n/s)*b。这里,nu表示矩阵u的子阵列的数量,nv表示矩阵s*v

t

的子阵列的数量。当原始交叉开关阵列的矩阵w的尺寸为512

×

128,并且取数比为10%时,ns(wt)=16 4=20。供参考,因为取数比为10%,k'=128*0.1=12.8且小于32。因此,当k被k’代替时,ceil(k/s)为1。

[0070]

当取数比减小,使得k’不超过m或n的一半时,可以估计在阵列划分中子阵列的数量减少。例如,当取数比小于0.5时,通常,ns(wt)小于ns(w),可以减少adc和加法器的操作的数量,并且可以减少操作电流。在表3中,在取数比为10%的情况中的子阵列的数量、adc的操作的数量、加法器的操作的数量、加法器级的数量以及操作电流将被比较性地示出。

[0071][0072]

[表3]

[0073]

作为参考,当通过c-tsvd实现2级时,adc的操作的数量、加法器的操作的数量、加法器级的数量和操作电流分别表示为ns(wt)*s、{ns(wt)-(ceil(k/s) ceil(n/s))*b}*s、ceil(log

2 ceil(m/s))和ns(wt)*s*s。因此,可以推导出表3所示的结果值。

[0074]

从表3中可以注意到,除了加法器级的数量之外,子阵列的数量、adc的操作的数量、和操作电流减少到31%,并且加法器的操作的数量减少到25%。操作电流的降低可能导致能量的相应降低,这可能意味着功率随着级数从1级增加到2级而进一步降低。

[0075]

一般来说,随着矩阵的尺寸的增加,这种减少的程度可能进一步增加。也就是说,随着矩阵的尺寸的增加,功率可以进一步降低。表4示出了子阵列的数量、adc的操作的数量和操作电流减少而矩阵的尺寸增加的比率。如表3所示,因为这些参数的每个参数的减小率是相同的,所以在表4中,减小率可以用一个值来表示。

[0076]

m\n51225612864325120.250.190.310.561.062560.190.250.380.631.131280.310.380.500.751.25640.560.630.751.001.50321.031.131.251.502.00

[0077]

[表4]

[0078]

从表4可以注意到,随着原始交叉开关阵列的矩阵的尺寸增加,减小率的值可以减小。在10%的取数比计算中,对于256,256*0.1=25.6被计算为一个子阵列,并且对于512,512*0.1=51.2可以被计算为两个子阵列。

[0079]

图9a和9b是示出根据一些实施例的交叉开关阵列装置可以应用于神经形态计算中的神经网络的层的概念图。

[0080]

参考图9a和图9b,图9a示出了处理层1和层2中的原始交叉开关阵列100-1和100-2的矩阵w并将矩阵w的输出输入到下一层的方法(以下称为“原始方法”)。如图9a所示,在层1和层2中,原始交叉开关阵列100-1和100-2可以经过阵列划分被划分为子阵列。

[0081]

图9b示出了处理在层1和层2中配置2级的部分交叉开关阵列100b1和100b2的矩阵并将当前层的输出输入到下一层的方法(以下称为“c-tsvd方法”)。部分交叉开关阵列100b1和100b2的矩阵可以通过如参考图8a和图8b所述的c-tsvd生成。此外,如图9b所示,在各个级,部分交叉阵列100b1和100b2可以经过阵列划分被划分成子阵列。

[0082]

在原始方法中,在每一层的最后一步,激活可以由激活函数电路140(诸如整流线性单元(relu))来执行。也就是说,加法器树130t的输出值可以由激活函数电路140激活。另一方面,在c-tsvd方法中,因为每个层在被分成矩阵sv

t

和矩阵u的同时被操作,所以来自矩阵sv

t

的输出可以原样传输到矩阵u。因此,可以在矩阵sv

t

的最后一个步骤中设置恒等函数(identity function)电路160,使得矩阵sv

t

的输出值——即加法器树130t1的输出值——可以原样输入到矩阵u。此外,在矩阵u的最后步骤中,其可以是每一层的最后步骤,像在原始方法中一样,可以布置激活函数电路140a,使得可以执行激活。也就是说,加法器树130t2的输出值可以由激活函数电路140a激活。

[0083]

另一方面,为了让用户选择原始方法或c-tsvd方法,可以在激活函数电路中实现恒等函数,并且在映射期间由控制器150执行设置。通过这样做,当可能难以允许伴随着应

用c-tsvd方法的甚至轻微的准确度损失和延迟损失时,可以通过使用控制器150来映射和使用原始方法。换句话说,用户可以选择性地应用原始方法或tsvd方法。

[0084]

下表5示出了当原始交叉开关阵列的矩阵具有m

×

n的尺寸时,用于计算1级原始方法的延迟和2级c-tsvd方法的延迟的等式。这里,延迟可以表示执行相应方法的操作所花费的时间。

[0085][0086][0087]

[表5]

[0088]

这里,作为读取一个单元所花费的时间的单元读取可以表示紧接在读取单元的电流被输入到读出放大器(s/a)并开始确定0/1之前的时间t_cell。此外,由于所有单元都可以同时读取,因此读取所有单元也需要t_cell。

[0089]

接下来,当adc的精确度为q位时,可以通过输入2^q-1参考来确定q位adc。当s/a需要t_sa来确定每个参考的0/1时,可能需要t_sa*(2^q-1)来输出所有参考的0或1。因为adc的尺寸很大,所以可能很难在每条位线(或子阵列的一列)中提供adc。因此,当一个adc被分

配给p_mux条位线并且需要t_mux来改变连接到adc的位线时,一个位线可能需要t_mux t_sa*(2^q-1)。此外,因为每个子阵列提供s条位线,所以一个子阵列可能需要s*(t_mux t_sa*(2^q-1))。另一方面,假设所有子阵列分别具有adc电路并同时执行adc,则所有子阵列的adc时间可以与一个子阵列的adc时间相同。

[0090]

当在每个子阵列中执行adc时,每个adc结果可以被发送到加法器树,以便将它们求和。此时,加法器树包括如上所述的ceil(log

2 ceil(m/s))个级。当每一级一次可处理的位线的数量为p_at并且需要时钟cycles_at来处理一条位线时,一个子阵列执行加法器树的一级可能需要s/p_at*cycles_at。因为ceil(n/s)个子阵列在一个阵列中在列方向上被提供,所以对于所有阵列来说,可以花费ceil(n/s)*(s/p_at)*cycles_at来执行加法器树的一级。当级数相乘时,可能需要ceil(log 2

ceil(m/s))*ceil(n/s)*(s/p_at)*cycles_at才能执行加法器树。

[0091]

激活可能意味着在执行加法器树之后执行激活所花费的时间。当一次可激活的位线的数量为p_ac时,一个阵列中的每个子阵列可能需要s/p_ac*cycles_ac。因为ceil(n/s)个子阵列是在一个阵列中以列方向提供的,所以所有阵列可能需要ceil(n/s)*s/p_ac*cycles_ac。

[0092]

最后,在c-tsvd方法中,因为具有尺寸m

×

n的矩阵被划分成分别具有尺寸k

×

n和m

×

k的两个矩阵,所以通过上述方法可以获得各个矩阵的相应的时间,并进行求和。

[0093]

表6示出了当在原始交叉开关阵列的矩阵的各种尺寸中取数比为10%时,c-tsvd方法中的2级与原始方法中的1级的延迟增加率。

[0094]

m\n51225612864325121.091.081.201.441.912561.021.081.211.451.921281.041.101.221.471.95641.051.111.241.491.97321.061.131.261.512.00

[0095]

[表6]

[0096]

这里,t_cell设为10ns,p_mux设为8,t_mux设为1个周期,t_sa设为10ns,q设为3位,p_at和p_ac中的每一个设为8,cycles_at设为1个周期,cycles_ac设为1个周期,并且频率设为1ghz。

[0097]

一般来说,随着矩阵的尺寸增加,增加比率可能会减小。因此,即使当矩阵的尺寸不小于256

×

256时,增加比率也可以不大于9%,这远小于子阵列数量、adc操作的数量、加法器操作的数量和操作电流的减少比率69%(100%

‑‑

》31%),这在上面被描述为优点。因此,当推理准确度的恶化和延迟的恶化在一定程度上被允许时,根据一些实施例的交叉开关阵列装置100b可以采用c-tsvd方法的两级配置。然而,当不允许推理准确度的恶化和/或延迟的恶化时,根据一些实施例的交叉开关阵列装置100b可以采用原始方法的1级配置。

[0098]

图10是示出了根据本发明构思的一些实施例的使用交叉开关阵列装置的模拟乘积累加(mac)操作方法的流程图。先前参考图1a至图9b给出的描述,为了简洁起见,可以省略。

[0099]

参考图10,在使用根据一些实施例的交叉开关阵列装置的模拟mac操作方法(以下

称为“模拟mac操作方法”)中,首先,在操作s310中,可以通过学习来计算原始交叉开关阵列的矩阵。接下来,在操作s320中,可以确定是否执行c-tsvd。也就是说,可以确定是否通过c-tsvd将原始交叉开关阵列的矩阵分解成两个部分交叉开关阵列的矩阵。可以确定是否考虑或基于与根据如上所述的子阵列数量的减少的优点相比的推理准确度的恶化和/或延迟的恶化来执行c-tsvd。

[0100]

当确定执行c-tsvd(来自操作s320的是分支)时,在操作s330中,原始交叉开关阵列的矩阵可以通过c-tsvd分解成两个部分交叉开关阵列的矩阵。此外,在操作s333中,两个部分交叉开关阵列可以被划分成子阵列。否则,当不执行c-tsvd时(操作s320的“否”分支),在操作s335中,原始交叉开关阵列可以被划分成子阵列。

[0101]

然后,在操作s340中,可以将输入值输入到子阵列的输入线,在操作s350中,可以在子阵列的每个子阵列中执行乘法和累加操作,并且可以输出输出线的输出值,在操作s360中,可以通过adc 120a对输出值进行模数转换,在操作s370中,并且可以通过加法器树130对adc 120a的结果求和。如上所述,通过对adc 120a的结果求和,可以完成一层中的模拟mac操作方法。

[0102]

图11a和11b是示出与神经形态计算中的神经网络的层有关的图10的模拟mac操作方法的流程图。先前参考图9a、图9b和图10给出的描述,为了简洁起见,在这里可以省略。

[0103]

参考图11a,根据一些实施例的模拟mac操作方法可以示意性地如图9a所示操作,并且可以通过使用采用原始方法的1级配置的交叉开关阵列装置100a来执行。更详细地,在操作s310中,可以通过学习来计算原始交叉开关阵列的矩阵,在操作s335中,可以将原始交叉开关阵列划分成子阵列,在操作s340中,可以将输入值输入到子阵列的输入线,在操作s350中,可以在子阵列的每个子阵列中执行乘法和累加操作,并且输出输出线的输出值,在操作s360中,可以通过adc 120a对输出值进行模数转换,并且在操作s370,可以通过加法器树130对adc 120a的结果求和。然后,在操作s380中,激活函数电路140可以执行激活,并且激活结果可以被转换成下一层的输入值。这里,下一层被图示为第二层2。然而,下一层不限于第二层2。

[0104]

参考图11b,根据一些实施例的模拟mac操作方法可以示意性地如图9b所示操作。并且可以通过使用采用c-tsvd方法的两级配置的交叉开关阵列设备100b来执行。更具体地,在操作s310中,可以通过学习来计算原始交叉开关阵列的矩阵,在操作s330中,可以通过c-tsvd方法将原始交叉开关阵列的矩阵分解成两个部分交叉开关阵列的矩阵,在操作s333中,可以将两个部分交叉开关阵列划分成子阵列,在操作s340a中,可以将输入值输入到与第一部分交叉开关阵列相对应的子阵列的输入线,在操作s350,可以在子阵列的每个子阵列中执行乘法和累加操作,并且可以输出输出线的输出值,在操作s360,可以通过adc 120a对输出值进行模数转换,并且在操作s370,可以通过加法器树130对adc 120a的结果求和。

[0105]

然后,在操作s390中,加法器树130t的结果可以通过恒等函数电路160来保持,在操作s340b中,输入值可以被输入到与第二部分交叉开关阵列相对应的子阵列的输入线,在操作s350中,可以在子阵列的每个子阵列中执行乘法和累加操作,并且输出输出线的输出值,在操作s360中,可以通过adc120a对输出值进行模数转换,在操作s370,adc 120a的结果可以通过加法器树130求和,并且激活可以由激活函数电路140a执行,并且在操作s380,激

活结果可以被转换成下一层的输入值。

[0106]

虽然已经参照本发明构思的一些实施例具体示出和描述了本发明构思,但是应当理解,在不脱离所附权利要求的范围的情况中,可以在形式和细节上进行各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。