一种双核异构soc芯片

技术领域

1.本发明属于智能电表和工业控制集成电路领域,尤其涉及一种双核异构soc芯片。

背景技术:

2.随着计算机的广泛应用,无论是通用工业领域,还是细分的电力电表智能终端领域,都对芯片的性能、能耗等要求越来越高。随着智能电网的推广以及电力新国标又提出计量芯与管理芯分离的双芯电能表计数方案,使得通用工业芯片无法满足新国标提出的计量芯法制独立要求。因此现有芯片方案,无法对通用工业领域和电力领域同时高度适配,通用工业芯片不能适用于电表芯中。现有的双核异构智能电表芯片,虽然有两个独立的管理单元和计量单元,可以较好的适用于电力电表领域。但是应用在通用工业领域,由于存在两个并行独立的系统,并且都有各自的处理器,因此,就给软件编写两个核的运行代码造成较大困难,同时,两个处理器均可对两个系统中的模块进行访问,会引起重大的系统安全漏洞,因此对系统安全性提出较大挑战。

技术实现要素:

3.发明目的:本发明所要解决的技术问题是针对现有技术的不足,提供一种双核异构soc(system on chip,系统级芯片)芯片,在满足电力电表领域新国标要求的情况下,同时能更好的适用于普通工业控制领域,大大减少了芯片研发成本。

4.为了解决上述技术问题,本发明公开了一种双核异构soc芯片,应用于电力电表领域和工业控制领域,包括管理模块、计量模块、低功耗模块和访问总线选择器;

5.进一步地,所述管理模块包括主处理器、第一ahb(advanced high performance bus,高级高性能总线)总线、主存储单元、主寄存器、第一ahb2apb桥和第一apb(advanced peripheral bus,外围总线)总线,所述计量模块包括计量处理器、总线桥、计量存储单元、计量寄存器、第二ahb总线、第二ahb2apb桥和第二apb总线;

6.所述主处理器和第一ahb总线连接,通过第一ahb总线访问主存储单元和主寄存器;所述计量处理器和第二ahb总线连接,通过第二ahb总线访问计量存储单元和计量寄存器;

7.第一ahb总线和第二ahb总线通过总线桥连接,使得主处理器能够访问计量模块;

8.第一ahb总线和第一apb总线通过第一ahb2apb桥连接,第二ahb总线和第二apb总线通过第二ahb2apb桥连接,第一apb总线和第二apb总线均与访问总线选择器连接,使得主处理器或计量处理器能够被选择访问低功耗模块;

9.所述低功耗模块包括第三apb总线和低功耗寄存器,所述第三apb总线分别与访问总线选择器和低功耗寄存器连接,所述低功耗寄存器,用于低功耗模块参数配置。

10.进一步地,所述主处理器能够为管理模块内部的所有部件设置安全级别,主处理器访问管理模块内的其他部件时所发出的读写访问权限,只有不低于其访问的目标部件的安全级别,才能正常访问。

11.为管理模块内部件设置安全级别,就可以有效区分安全区和非安全区。安全区可以用来存放非用户可修改的数据,或者执行非用户可更改的功能,这样防止出现安全漏洞,大大提高芯片安全性。而非安全区可以开放给客户,使客户可以灵活自用的配置使用部分芯片功能。

12.进一步地,所述低功耗寄存器包括芯片模式寄存器,

13.所述芯片模式寄存器,用于配置芯片模式,所述芯片模式包括双核工控芯片模式和电表芯片模式;

14.当芯片模式为双核工控芯片模式,所述双核异构soc芯片应用于工业控制领域,计量模块从属于管理模块,主处理器能够访问计量模块中的所有部件和访问低功耗模块、能够控制计量模块是否工作以及能够控制计量模块是否访问低功耗模块,计量处理器无法访问管理模块;

15.当芯片模式为电表芯片模式,所述双核异构soc芯片应用于电力电表领域,管理模块和计量模块相互独立,主处理器仅能够访问计量存储单元中的静态随机存储器sram,无法访问计量模块的其他部件以及低功耗模块,计量处理器能够访问低功耗模块,控制所述双核异构soc芯片进入或退出低功耗模式。

16.所述双核异构soc芯片能够同时应用于工业控制领域和电力电表领域,降低了芯片研发成本和程序设计复杂度,同时提升了芯片的安全性。

17.进一步地,所述低功耗寄存器还包括低功耗访问控制寄存器和低功耗访问权限寄存器,所述低功耗访问控制寄存器用于配置低功耗模块自身的安全属性,所述低功耗访问权限寄存器用于配置计量模块访问低功耗模块的安全属性,所述安全属性包括安全和不安全两种属性;

18.当芯片模式为双核工控芯片模式,主处理器能够控制计量模块是否访问低功耗模块包括:

19.当主处理器将低功耗访问控制寄存器配置为安全,将低功耗访问权限寄存器配置为安全,则计量模块能够访问低功耗模块;

20.当主处理器将低功耗访问控制寄存器配置为安全,将低功耗访问权限寄存器配置为不安全,则计量模块无法访问低功耗模块;

21.当主处理器将低功耗访问控制寄存器配置为不安全,计量模块能够访问低功耗模块。

22.上述配置大大增加了芯片的安全性。

23.进一步地,主存储单元和计量存储单元均包括闪存flash、只读存储器rom和静态随机存储器sram,用于存储数据和程序;主寄存器和计量寄存器分别用于管理模块和计量模块参数配置。

24.进一步地,所述总线桥包括译码单元,所述译码单元用于实现管理模块和计量模块之间的连通性;

25.当芯片模式为双核工控芯片模式,译码单元译码计量模块中所有部件的地址,使得主处理器能够访问计量模块中的所有部件,使得计量模块从属于管理模块,而计量处理器无法访问管理模块;

26.当芯片模式为电表芯片模式,译码单元仅译码计量模块中的静态随机存储器sram

地址,使得主处理器仅能够通过第一ahb总线访问到连接于第二ahb总线上的计量静态随机存储器sram,从而完成与计量处理器的通信。计量模块中的其他部件,主处理器不能访问,这样,管理模块和计量模块独立运行,互不影响。

27.进一步地,芯片模式寄存器配置的初始芯片模式为双核工控芯片模式,若需要配置为电表芯片模式,配置过程包括:主处理器在管理模块闪存flash中将双核异构soc芯片的芯片模式烧写为电表芯片模式,存储在管理模块只读存储器rom中的程序根据烧写信息,改写芯片模式寄存器中的芯片模式为电表芯片模式。

28.进一步地,所述低功耗寄存器还包括芯片模式锁定寄存器,所述芯片模式锁定寄存器用于存放锁定芯片模式寄存器的密钥,在改写芯片模式寄存器中的芯片模式为电表芯片模式后,主处理器向芯片模式锁定寄存器写入密钥,锁定芯片模式寄存器,这样能够保证后续无法对芯片模式寄存器进行改写,防止客户误操作发生错误,或者在特定场景下错误的模式造成安全漏。

29.进一步地,所述计量寄存器包括软复位寄存器和时钟寄存器,所述软复位寄存器用于配置计量模块是否进行软复位,所述时钟寄存器用于配置计量模块的时钟单元开启或关闭;

30.当芯片模式为双核工控芯片模式,主处理器能够控制计量模块是否工作包括:

31.主处理器通过配置软复位寄存器和时钟寄存器,将计量模块的软复位置位以及关闭时钟,使计量模块不再工作;此时所述双核异构soc芯片可以当做单核芯片使用,在此工作场景下,就大大降低了芯片功耗。

32.主处理器通过配置软复位寄存器和时钟寄存器,将计量模块的软复位释放以及开启时钟,使计量模块恢复工作。

33.进一步地,所述主寄存器包括第一管理模块低功耗模式寄存器,所述低功耗寄存器还包括第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,所述第一管理模块低功耗模式寄存器和第二管理模块低功耗模式寄存器均用于配置管理模块是否进入低功耗模式,所述计量模块低功耗模式寄存器用于配置计量模块是否进入低功耗模式;

34.主处理器能够配置第一管理模块低功耗模式寄存器,让管理模块自主进入低功耗模式;

35.当芯片模式为电表芯片模式,计量处理器能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式;主处理器无法配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器;

36.当芯片模式为双核工控芯片模式,主处理器能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式;当主处理器配置计量模块能够访问低功耗模块时,计量处理器也能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式。

37.有益效果:

38.本技术提供的一种双核异构soc芯片,在满足电力电表领域新国标要求的情况下,同时能更好的适用于普通工业控制领域,大大减少了芯片研发成本。管理模块和计量模块不再是并行的独立关系,而是计量模块从属于管理模块,计量模块可视为双核异构soc芯片的一个单纯的计量模块,受管理模块的管理。同时,计量模块处理器无法访问管理模块的模

块,在软件难度和系统安全性上,就有了较大提升。

附图说明

39.下面结合附图和具体实施方式对本发明做更进一步的具体说明,本发明的上述和/或其他方面的优点将会变得更加清楚。

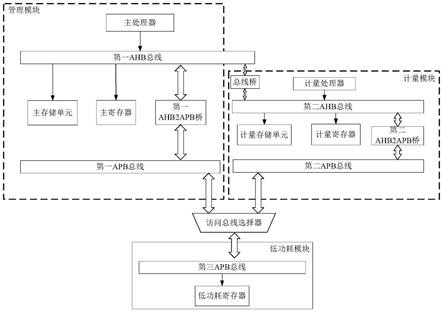

40.图1为本技术实施例提供的一种双核异构soc芯片的结构示意图。

具体实施方式

41.下面将结合附图,对本发明的实施例进行描述。

42.本技术实施例公开了一种双核异构soc芯片,应用于电力电表领域和工业控制领域,如图1所示,包括管理模块、计量模块、低功耗模块和访问总线选择器;

43.所述管理模块包括主处理器、第一ahb总线、主存储单元、主寄存器、第一ahb2apb桥和第一apb总线,所述计量模块包括计量处理器、总线桥、计量存储单元、计量寄存器、第二ahb总线、第二ahb2apb桥和第二apb总线;

44.所述主处理器和第一ahb总线连接,通过第一ahb总线访问主存储单元和主寄存器;所述计量处理器和第二ahb总线连接,通过第二ahb总线访问计量存储单元和计量寄存器;

45.主存储单元和计量存储单元均包括闪存flash、只读存储器rom和静态随机存储器sram,用于存储数据和程序;

46.主寄存器和计量寄存器分别用于管理模块和计量模块参数配置;

47.第一ahb总线和第二ahb总线通过总线桥连接,使得主处理器能够访问计量模块;

48.第一ahb总线和第一apb总线通过第一ahb2apb桥连接,第二ahb总线和第二apb总线通过第二ahb2apb桥连接,第一apb总线和第二apb总线均与访问总线选择器连接,使得主处理器或计量处理器能够被选择访问低功耗模块。

49.管理模块和计量模块还包括其他单元,属于现有技术,例如两个模块均包括复位单元和时钟单元等,本发明实施例在此不做限定。

50.第一apb总线和第二apb总线上还挂着其他部件,属于现有技术,例如工控芯片中的通用架构,本发明实施例在此不做限定。

51.所述低功耗模块包括第三apb总线和低功耗寄存器,所述第三apb总线分别与访问总线选择器和低功耗寄存器连接,所述低功耗寄存器,用于低功耗模块参数配置。

52.第三apb总线上还挂着其他模块部件,属于现有技术,例如工控芯片中的通用架构,本发明实施例在此不做限定。

53.本实施例中,所述主处理器能够为管理模块内部的所有部件设置安全级别,主处理器访问管理模块内的其他部件时所发出的读写访问权限,只有不低于其访问的目标部件的安全级别,才能正常访问。例如,主处理器向主存储单元的sram发出的访问为非安全级别访问,而主存储单元的sram被设置为安全级别,那么被访问的主存储单元的sram权限高于此次访问权限,则此次不能被主处理器访问;如果主处理器改为安全级别访问,则可以访问被设置为安全级别的主存储单元的sram。

54.本实施例中,所述低功耗寄存器包括芯片模式寄存器,

55.所述芯片模式寄存器,用于配置芯片模式,所述芯片模式包括双核工控芯片模式和电表芯片模式;

56.当芯片模式为双核工控芯片模式,所述双核异构soc芯片应用于工业控制领域,计量模块从属于管理模块,主处理器能够访问计量模块中的所有部件和访问低功耗模块、能够控制计量模块是否工作以及能够控制计量模块是否访问低功耗模块,计量处理器无法访问管理模块;

57.当芯片模式为电表芯片模式,所述双核异构soc芯片应用于电力电表领域,管理模块和计量模块相互独立,主处理器仅能够访问计量存储单元中的静态随机存储器sram,无法访问计量模块的其他部件以及低功耗模块,计量处理器能够访问低功耗模块,控制所述双核异构soc芯片进入或退出低功耗模式。

58.本实施例中,所述低功耗寄存器还包括低功耗访问控制寄存器和低功耗访问权限寄存器,所述低功耗访问控制寄存器用于配置低功耗模块自身的安全属性,所述低功耗访问权限寄存器用于配置计量模块访问低功耗模块的安全属性,所述安全属性包括安全和不安全两种属性;

59.当芯片模式为双核工控芯片模式,主处理器能够控制计量模块是否访问低功耗模块包括:

60.当主处理器将低功耗访问控制寄存器配置为安全,将低功耗访问权限寄存器配置为安全,则计量模块能够访问低功耗模块;

61.当主处理器将低功耗访问控制寄存器配置为安全,将低功耗访问权限寄存器配置为不安全,则计量模块无法访问低功耗模块;

62.当主处理器将低功耗访问控制寄存器配置为不安全,计量模块能够访问低功耗模块。

63.本实施例中,所述总线桥包括译码单元,所述译码单元用于实现管理模块和计量模块之间的连通性;

64.当芯片模式为双核工控芯片模式,译码单元译码计量模块中所有部件的地址,使得主处理器能够访问计量模块中的所有部件,而计量处理器无法访问管理模块;

65.当芯片模式为电表芯片模式,译码单元仅译码计量模块中的静态随机存储器sram地址,使得主处理器仅能够通过第一ahb总线访问到连接于第二ahb总线上的计量静态随机存储器sram,从而完成与计量处理器的通信。

66.本实施例中,芯片模式寄存器配置的初始芯片模式为双核工控芯片模式,若需要配置为电表芯片模式,配置过程包括:主处理器在管理模块闪存flash中将双核异构soc芯片的芯片模式烧写为电表芯片模式,存储在管理模块只读存储器rom中的程序根据烧写信息,改写芯片模式寄存器中的芯片模式为电表芯片模式;

67.所述低功耗寄存器还包括芯片模式锁定寄存器,所述芯片模式锁定寄存器用于存放锁定芯片模式寄存器的密钥,在改写芯片模式寄存器中的芯片模式为电表芯片模式后,主处理器向芯片模式锁定寄存器写入密钥,锁定芯片模式寄存器。

68.本实施例中,所述计量寄存器包括软复位寄存器和时钟寄存器,所述软复位寄存器用于配置计量模块是否进行软复位,所述时钟寄存器用于配置计量模块的时钟单元开启或关闭;

69.当芯片模式为双核工控芯片模式,主处理器能够控制计量模块是否工作包括:

70.主处理器通过配置软复位寄存器和时钟寄存器,将计量模块的软复位置位以及关闭时钟,使计量模块不再工作;主处理器通过配置软复位寄存器和时钟寄存器,将计量模块的软复位释放以及开启时钟,使计量模块恢复工作。

71.本实施例中,所述主寄存器包括第一管理模块低功耗模式寄存器,所述低功耗寄存器还包括第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,所述第一管理模块低功耗模式寄存器和第二管理模块低功耗模式寄存器均用于配置管理模块是否进入低功耗模式,所述计量模块低功耗模式寄存器用于配置计量模块是否进入低功耗模式;

72.主处理器能够配置第一管理模块低功耗模式寄存器,让管理模块自主进入低功耗模式;

73.当芯片模式为电表芯片模式,计量处理器能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式;主处理器无法配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器;

74.当芯片模式为双核工控芯片模式,主处理器能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式;当主处理器配置计量模块能够访问低功耗模块时,计量处理器也能够配置第二管理模块低功耗模式寄存器和计量模块低功耗模式寄存器,分别让管理模块和计量模块进入低功耗模式。

75.主处理器和/或计量处理器能够控制所述双核异构soc芯片退出低功耗模式,决定了从低功耗模式下退出的唤醒方式,例如,uart(universal asynchronous receiver/transmitter,异步收发传输器)、io(input/output,输入/输出)、定时器timer和电压监测等都可以作为管理模块和计量模块的唤醒源。例如,计量处理器配置低功耗模块寄存器中的计量模块低功耗模式寄存器,可使计量模块进入低功耗模式。此后,多种唤醒源可以将计量模块从低功耗模式唤醒,进入正常工作模式。例如,可设置timer为1秒过后唤醒计量模块;当唤醒单元中的uart收到芯片外部数据后,唤醒计量模块;io平时为低电平,当被拉高为高电平时,可唤醒计量模块;电压监测可监测双核异构soc芯片主电源电压是否正常,当监测不正常时,可唤醒计量模块,通知芯片电压出现异常,需要计量模块及时上报和处理。

76.上述配置最终实现不同电表应用场景下功耗的最小化。

77.本发明提供了一种双核异构soc芯片的思路及方法,具体实现该技术方案的方法和途径很多,以上所述仅是本发明的具体实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。本实施例中未明确的各组成部分均可用现有技术加以实现。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。