ram的读写控制方法

技术领域

1.本发明涉及数据缓存交互领域,更具体地涉及一种ram的读写控制方法。

背景技术:

2.随机存取存储器(英语:random access memory,缩写:ram),也叫主存,是与cpu直接交换数据的内部存储器。它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。ram工作时可以随时从任何一个指定的地址写入或读出数据。其在计算机和数字系统中用来暂时存储程序、数据和中间结果;因此,ram在各数据缓存交互领域被广泛应用。比如在某项目中,涉及到数据缓存、dma操作、数据流交互等功能,其中ram位宽为64bit,a模块数据位宽为32bit,b模块数据位宽为16bit;a模块部分由于数据位宽与ram位宽是两倍关系,通过时钟二分频信号对读写使能控制以及数据位宽转换;b模块部分由于数据位宽与ram位宽是四倍关系,通过计数方式进行读写使能控制以及数据位宽转换。

3.但在上述所使用的ram控制方中,在同一个项目中,当有多个模块需要对ram进行访问时,由于各个模块的数据位宽以及读写使能各不相同,就需要多次编写读写控制逻辑;当开发新项目时,模块之间又发生了变化,控制逻辑又要重新进项编写;因此不仅限制了使用的灵活性与应用范围,同时还给开发人员带来了很多重复性工作,降低了工作效率。

4.因此,有必要提供一种改进的ram的读写控制方法来克服上述缺陷。

技术实现要素:

5.本发明的目的是提供一种ram的读写控制方法,本发明的ram的读写控制方法减少了开发人员的重复性工作,且可适用于同一个项目中不同的模块以及不同的项目模块,提高了通用性。

6.为实现上述目的,本发明提供了一种ram的读写控制方法,其包括如下步骤:

7.a.外部数据输入ram控制顶层的输入模块,获取输入数据的位宽信息;

8.b.根据ram的位宽信息配置输入模块中输入数据的位宽比与ram控制顶层的输出模块中输出数据的位宽比;

9.c.产生ram写使能信号与写地址信息,根据输入模块中的输入数据的位宽比将外部数据写入ram内;

10.d.产生ram读使能信号与读地址信息,根据输出模块中的输出数据的位宽比从ram中将数据读出至输出模块。

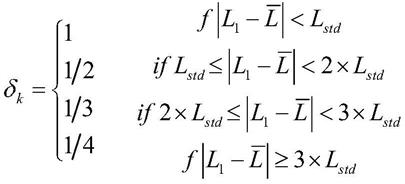

11.较佳地,设定ram的位宽为k,输入数据的位宽为a,输出数据的位宽为b,输入数据的位宽比为k1,输出数据的位宽比为k2,则满足:k1*a=k=k2*b,其中k1与k2为自然数。

12.较佳地,根据输入模块中的输入数据的位宽比将外部数据写入ram内具体地为:计数器计数k1次,在输入所述输入模块的信号有效时,每计数一次且信号有效时,输入数据赋值给ram,且每次赋值给ram的位数为a。

13.较佳地,当输入信号有效时,计数器从0开始计算,输入数据按[a(k1-n)-1:a(k1-n-1)]的方式赋值给ram],n为计数器当前的计数值,且0≤n<k1。

[0014]

较佳地,计数器计数次数达到k1次且信号有效时,所述写地址加1。

[0015]

较佳地,根据输出模块中的输出数据的位宽比从ram中将数据读出至ram控制顶层的输出模块具体地为:计数器在外部读使能信号有效时开始计数,计数器计数k2次,每计数一次,ram赋值给输出模块,且每次赋值给输出模块的位数为b。

[0016]

较佳地,计数器的初始值为0,当外部读使能信号有效时开始计数,当计数完k2则置1;当外部读使能信号无效时,且计数完k2时则清0;循环计数。

[0017]

较佳地,计数器从0开始计数,并将计数器延迟一拍,ram从延迟计数器的计数值为1开始赋值给输出模块,且延迟计数器每计数一次,ram按[b(k2-m 1)-1:b(k2-m)]的方式赋值给输出模块,m为延迟计数器当前的计数值,1≤m≤k2。

[0018]

较佳地,计数器计数值为1时,ram读使能有效,所述读地址加1。

[0019]

与现有技术相比,本发明的ram的读写控制方法,通过参数配置对数据输入端以及数据输出端的位宽进行设置,同时也可以对ram地址深度和数据位宽的参数进行配置,通过计数器的有效标志进行计数来实现高低位宽的数据转换,同时控制ram的读写使能,从而实现输入数据、输出数据与ram之间的位宽匹配,实现数据的正常交互,使得在不同的模块中不再需要反复地控制逻辑编写,减少了开发人员的重复性工作,也提高了通用性。

[0020]

通过以下的描述并结合附图,本发明将变得更加清晰,这些附图用于解释本发明的实施例。

附图说明

[0021]

图1为本发明ram的读写控制方法的流程图。

[0022]

图2为实现本发明ram的读写控制方法的结构框图。

[0023]

图3为本发明ram的读写控制方法中写入数据的时序图。

[0024]

图4为本发明ram的读写控制方法中读出数据的时序图。

具体实施方式

[0025]

现在参考附图描述本发明的实施例,附图中类似的元件标号代表类似的元件。如上所述,本发明提供了一种ram的读写控制方法,本发明的ram的读写控制方法减少了开发人员的重复性工作,且可适用于同一个项目中不同的模块以及不同的项目模块,提高了通用性。

[0026]

请结合参考图1与图2,如图所示,本发明的ram的读写控制方法包括如下步骤:

[0027]

步骤s001,外部数据输入ram控制顶层的输入模块,获取输入数据的位宽信息;在本步骤中,在所述ram控制顶层的输入模块中获取输入数据的位宽信息,以方便后续调整该输入数据的位宽比。

[0028]

步骤s002,根据ram的位宽信息配置输入模块中输入数据的位宽比与ram控制顶层的输出模块中输出数据的位宽比;在本步骤中,根据ram的位宽信息分配配置输入所述ram的数据的位宽比与输出所述ram的数据的位宽比,当然,在不同的应用场合,ram的位宽并不固定,可根据实际的应用场合进行配置;具体地,设定ram的位宽为k,输入数据的位宽为a,

输出数据的位宽为b,输入数据的位宽比为k1,输出数据的位宽比为k2,则满足:k1*a=k=k2*b,其中k1与k2为自然数,则可根据方程式k1*a=k=k2*b对ram的位宽、输入数据的位宽比、输出数据的位宽比进行合理配置,配置的参数满足上式即可;而且,通过上式也可得出,当在某些特殊情况下,输入数据的位宽比或输出数据的位宽比不便于进行改变时,可相应调整配置所述ram的位宽,以使上式成立,即可实现对ram的读写。

[0029]

步骤s003,产生ram写使能信号与写地址信息,根据输入模块中的输入数据的位宽比将外部数据写入ram内;在本步骤中,在ram中产生写使能信号与写地址信息,以此确保ram已准备好能写入数据;具体地,计数器计数k1次,在输入所述输入模块的信号(wr_vld)有效时,每计数一次输入数据赋值给ram,且每次赋值给ram的位数为a,也即是,计数器依输入数据的位宽比为次数进行计数,每进行一次有效计数就输入数据赋值给ram,而且每一次赋值的位数为a,即实现对ram的k1次赋值,满足式子k1*a=k;更进一步地,当输入信号(wr_vld)有效时,计数器从0开始计数,输入数据按[a(k1-n)-1:a(k1-n-1)]的方式赋值给ram],n为计数器当前的计数值,且0≤n<k1,而当n=k1时计数器清零;例如,若k=64,a=16,k1=4,当计数器从0开始计数,当计数器的计数值n为0时,输入数据赋值给ram[63:48],当计数器的计数值n为1时,输入数据赋值给ram[47:32],当计数器的计数值n为2时,输入数据赋值给ram[31:16],当计数器的计数值n为3时,输入数据赋值给ram[15:0]即完成0、1、2、3的四次赋值;另外,在本步骤中,当完成一次完整的数据写入过程,也即计数器计数次数达到k1次且信号(wr_vld)有效时,所述写地址加1,以为下一次的数据写入准备好地址信号。具体时序如图3所示,其中,在图3中,clk为时钟信号,divld为输入信号,din为输入数据,wrcnt为写计数器,ramwr为ram写使能信号,ramdi为写入数据,ramaddr为ram地址信号。在本步骤中,使输入数据与ram数据位宽匹配,并同时给出ram的写使能和写地址信号,将输入数据的位宽进行转换并成功写入ram空间。

[0030]

步骤s004,产生ram读使能信号与读地址信息,根据输出模块中的输出数据的位宽比从ram中将数据读出至输出模块;在本步骤中,在ram中产生读使能信号与读地址信息,以此确保ram已准备好能读出数据,并在外部读使能信号有效时即可对ram正常读取数据;具体地,计数器在外部读使能信号有效时开始计数,计数器计数k2次,每计数一次ram赋值给输出模块,且每次赋值给输出模块的位数为b。也即是,计数器依输出数据的位宽比为次数进行计数,每进行一次有效计数ram就赋值给输出模块,而且每一次赋值的位数为b,即实现ram对输出模块的k2次赋值,满足式子k2*b=k。更进一步地,计数器的初始值为0,当外部读使能信号有效时开始计数,当计数完k2则置1,以开始下一轮的计数;当外部读使能信号无效时,且计数完k2时则清0,以等待下一个外部读使能信号有效而开始重新计数;也即是,所述计数器按上述两种方式不断循环计数,直到计数结束,具体时序如图4所示。其中,计数器从0开始计数,同时,并将计数器延迟一拍,ram从延迟计数器的计数值为1开始赋值给输出模块,且延迟计数器每计数一次,ram按[b(k2-m 1)-1:b(k2-m)]的方式赋值给输出模块,m为延迟计数器当前的计数值,1≤m≤k2;从而使得所述ram读出数据与延迟一拍后的计数器(延时计数器)对齐;其中,所述延迟计数器即为当前计数器延迟一拍后所形成的计数器;举例如下:k=48,b=24,k2=2,当延迟计数器的计数值m为1,ram[47:24]赋值给输出模块,当延迟计数器的计数值m为2时,ram[23:0]赋值给输出模块即完成1、2的二次赋值。再有,在本步骤中,计数器计数值为1时,ram读使能有效,所述读地址加1,以为下一次的数据读出准备

好地址信号;同时从图4所示时序图可知,所述地址信号与计数器直接对齐。另外,在图4中,clk为时钟信号,rden为外部读使能信号,rdcnt为计数器,ramrd为ram读使能信号,ramaddr为ram的地址信号,ramdo为ram的输出数据,radcntd为延迟计数器,dovld为输出数据有效信号,dout输出数据。如上所述,在本步骤中对从ram回读的数据进行计数拆分,并将其对应的bit位输出,通过这种方式,使ram数据与输出数据位宽匹配,并给出输出数据和数据有效信号,从而实现对输出数据的有效转换并成功输出。

[0031]

下面请再结合参考图2,举例说明本发明ram的读写控制方法的配置过程。其中,clk,wen,cen,addr,wdata,rdata为常规ram接口。

[0032]

例如:当前需要实现外部输入数据16bit,外部输出数据32bit,ram深度为256,ram数据接口位宽为64bit。(由于实际使用情况,以及ram的灵活性,默认ram数据位宽大于等于外部数位宽)则参数设置如下:

[0033]

输入数据位宽:data_i=16;

[0034]

输出数据位宽:data_o=32;

[0035]

ram地址位宽:ram_addr=256;

[0036]

ram数据位宽:ram_data=64;

[0037]

输入数据位宽比例:ram_i_bit_ratio=4;

[0038]

输出数据位宽比例:ram_o_bit_ratio=2。

[0039]

综上所述,本发明的ram的读写控制方法,通过参数配置对数据输入端以及数据输出端的位宽进行设置,同时也可以对ram地址深度和数据位宽的参数进行配置,通过计数器的有效标志进行计数来实现高低位宽的数据转换,同时控制ram的读写使能,从而实现输入数据、输出数据与ram之间的位宽匹配,实现数据的正常交互,使得在不同的模块中不再需要反复地控制逻辑编写,减少了开发人员的重复性工作,也提高了通用性。

[0040]

以上结合最佳实施例对本发明进行了描述,但本发明并不局限于以上揭示的实施例,而应当涵盖各种根据本发明的本质进行的修改、等效组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。